PLL-VCO設計及制作第一部分

在此說明以晶體振蕩器做為基準振蕩器,將其與VCO以及PLL電路組合成為信號產生器的情形也被稱為頻率合成器。

此一PLL-VCO電路的設計規格如表l所示。振蕩頻率范圍為40M~60MHz內的10MHz寬。每一頻率階段(step)寬幅為10kHz。頻率的穩定度目標與晶體振蕩電路相近。

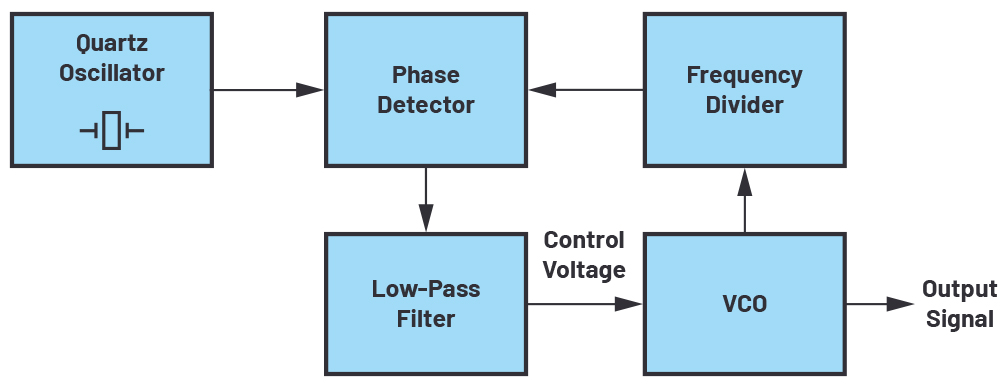

PLL-VCO的工作原理

| 表一 PLL-VCO的設計規格 | |

| 振蕩頻率 | 40M-60MHz中的10MHz寬幅 |

| 頻率階段 | 10KHz |

| 頻率穩度 | 與晶體振蕩器同等 |

| 振蕩波形 | 正弦波 |

| 溫度范圍 | 0-50℃ |

| 電源電壓 | 12~15V |

表1 PLL-VCO的設計規格

(根據使用目的與規格,決定振蕩頻率與頻率階段。頻率穩定度高,且可以做階段性變化。)

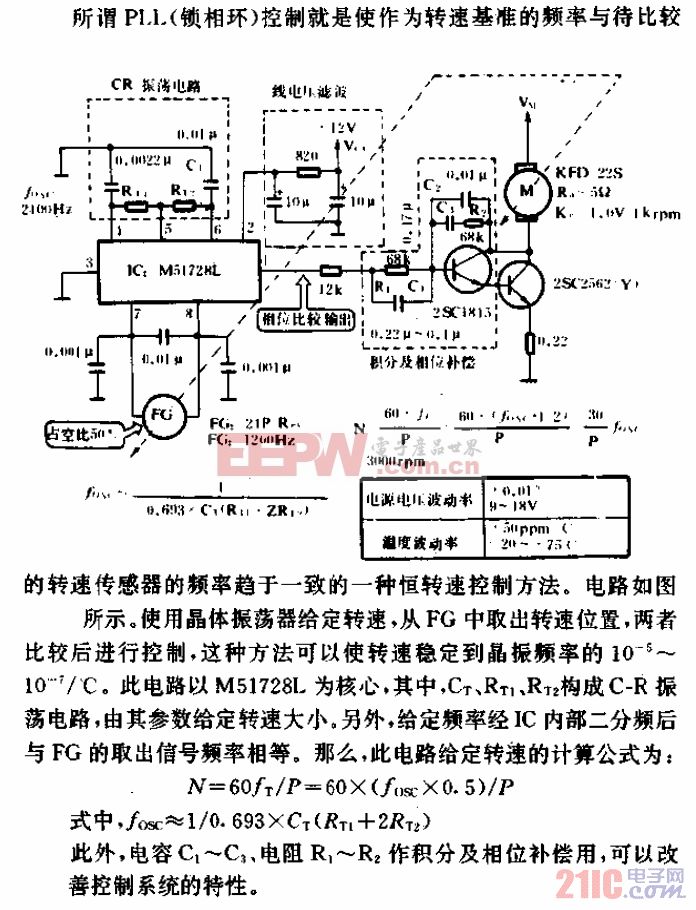

圖3所示的為此將制作的PLL.VC0電路之方塊圖。假設VCO電路的振蕩頻率為53.29MHz工作原理。

(利用數字設定用SW設定BCD符碼,做為頻率的設定,將晶體與VCO電路做相位比較,以達頻率穩定化。)

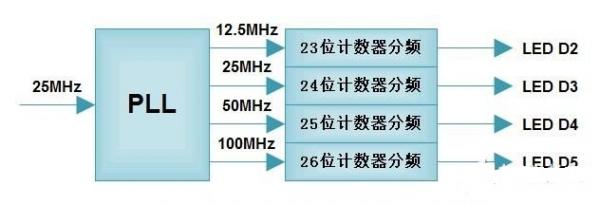

首先,利用晶體產生10.24MHz之振蕩。再將此做1024分頻,產生fr=10kHz的基準頻率。

另外,將VCO電路之振蕩頻率fosc利用N分頻電路做N分頻成為fo也即是,fo=fosc/N。此一分頻比N之值,是利用數字設定用SW,根據BCD (Binary Coded Decimal)符碼而設定的。

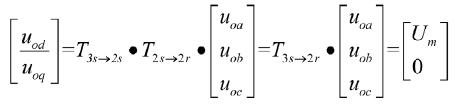

接著,利用相位比較器做fr與fo的相位比較。如果frfo時,會發生誤差檢出脈波。此再利用回路濾波器積分成為直流電壓,以此控制VC0振蕩電路,使fr=fo。

在PLL電路成為鎖栓(Locked)狀態時,VCO的振蕩頻率應該為fosc=N x f0=N x fr

假設數字設定用SW所設定的數字為"5329"時,fosc成為fosc=5329×10kHz=53.29MHz

所以,只要改變數字設定用SW所設定的數字,便可以改變VCO的振蕩頻率。

因此,PLL電路為利用頻率反饋控制,使fr=fo。而且由于fr是經由晶體振蕩器的頻率分頻而得,所以,PLL的VCO所產生的頻率穩定度可以與晶體振蕩器比美。

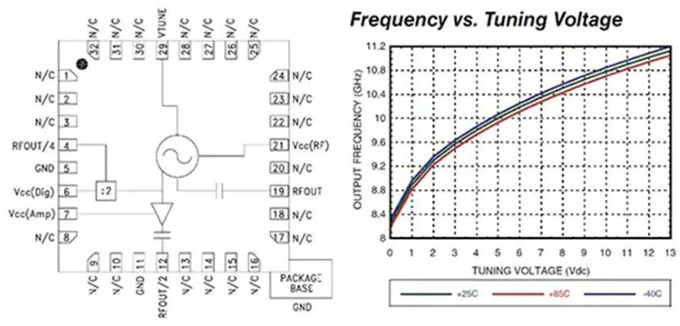

PLL用IC MC145163P

此所使用的PLL用IC為Motorola公司的MC145l63P。圖4所示的為MC145163P的特性與端子連接圖,以及方塊圖。

此一IC內含有可以產生基準頻率fr的晶體振蕩電路與分頻電路,將VCO信號分頻用的N分頻電路,以及將fo與fr做為此較用的相位比較電路。

此一IC為28個端子DIP型。電源電壓為3~9V工作原理,工作原理頻率為30MHz(電源電壓5V),如果電源電壓成為9V時,工作原理頻率可以延伸至80MHz。因此,對于設計規格為40M~60MHz而言,不會有問題。

圖4MCl45163P的構成

(此為LSI,集積度高,與VCO電路配合,可以組成PLL電路。)

電路的接地 VDD(3端子) 正電源(+5V) OSCin(26端子,27端子)

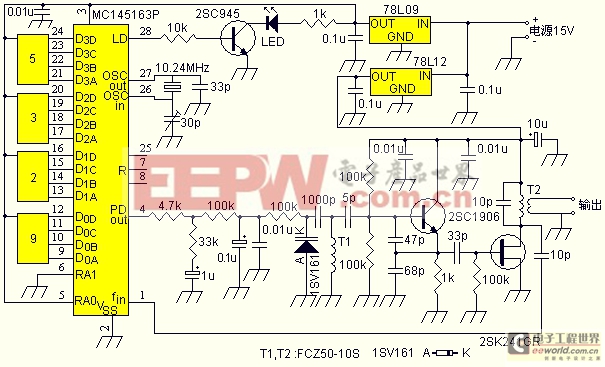

圖5所示的為實際的PLL-VCO電路的構成。MC145163P主要功能端口說明 fin

(1端子) 頻率合成器的可程式化計數器(/N計數器部)的輸入,通常fin 可以從VCO取得,以AC結合連接至1端子。在標準CMOS邏輯位準之大振幅信號的場合,也可以采用直接結合。 Vss

(2端子)PDout

(4端子)當伯VCO控制信號,由相位比較器的3狀態輸出。

頻率fv > fr或fv相位前進;負脈波。

頻率fv fr或fv相位延遲;正脈波。

頻率fv = fr與同相位;高阻抗狀態。RA0

RA1(5端子,6端子)由這些輸入,設定基準分頻器(R計數器)的分頻比。分頻比可以從512,2048,4096中選擇。 ΦR,ΦV

(7端子,8端子)利用這些相位比較器的輸出,與通低頻慮波器組合,成為VCO的控制信號。

頻率fv > fr或相位前進的場合:

ΦV 會發生L脈波,ΦR 會維持H。

頻率fv fr或fv相位延遲的場合:

ΦV 維持H, ΦR產生L脈波。

頻率fv = fr與同相位的場合:

ΦV ,ΦR 都成為H。BCD輸入

(9端子-24端子)這 些的輸入數據,在N計數器的內容成為時,會被預先設定(preset).

9端子為100位數的LSB,24端子為100位數的MSB,由于內藏有pull down電阻。因此,在輸入開放時成為L位準。利用BCD數字設定SW的使用,可以任意設定3至9999為止的任意分頻比。REFout

(25端子)內部基準振蕩器外部基準信號的緩沖輸出。 OSCout, 在這些端子上連接水晶振蕩子時,便成為基準振蕩器。使用適當值的電容連接OSCin與接地間,以及OSCout與接地間。OSCin也成為外部一產生基準信號的輸入。這些信號通常在OSCin做AC結合。但是,在大振幅信號(CMOS邏輯位準)的組合,則使用DC結合。在外部基準Mode中,不必要與OSCout連接。 LD(28端子) PLL鎖栓檢知信號,在PLL回路成為鎖栓時(fr與fv的頻率與相位為相同時)成為H,不成為鎖栓時則產生脈波。  圖5 PLL-VCO電路圖

圖5 PLL-VCO電路圖

(VCO電路與緩沖放大器的工作原理電壓為12V。為了提高MC145163P的工作原理頻率,將電源電壓提高至9V。)

評論