常用的跳頻頻率合成器方案比較

1.1 直接頻率綜合

直接頻率綜合技術(shù)的典型工作原理是將高穩(wěn)定度的晶體振蕩器輸出的頻標信號通過諧波發(fā)生器產(chǎn)生梳狀頻譜信號,并用濾波器取出所需要的頻率成分,再將它們進行組合混頻濾波,經(jīng)電子開關(guān)切換得到最終的跳頻信號。其優(yōu)點是頻率轉(zhuǎn)換時間短;相位噪聲低;輸出信號頻率較高。缺點是頻譜雜散較難抑制,隨著跳頻點數(shù)增加,硬件的復(fù)雜度呈指數(shù)關(guān)系增長,相應(yīng)的體積和重量也較大。

1.2 鎖相環(huán)頻率綜合

與直接頻率綜合技術(shù)不同,采用鎖相環(huán)頻率綜合技術(shù)的頻率合成器可以輸出較多的頻率點數(shù),頻譜雜散分量較少,相位噪聲也較低,硬件比較簡單。它的工作原理是將壓控振蕩器產(chǎn)生的射頻信號和晶體振蕩器輸出的參考信號分別進行分頻,得到兩個頻率近似相同的信號,并送到鑒相器比較出誤差信號,誤差信號經(jīng)過濾波后,控制壓控振蕩器,使壓控振蕩器輸出的射頻信號保持穩(wěn)定。它也易于得到較高頻率的信號,但是,采用鎖相環(huán)頻率合成技術(shù)的頻率合成器應(yīng)用于高速跳頻系統(tǒng)最大的弱點是其頻率轉(zhuǎn)換時間長,從數(shù)十微秒到幾百毫秒之間,這對于某些超高速跳頻系統(tǒng)而言,已經(jīng)不能滿足頻率駐留時間的要求。

1.3 直接數(shù)字頻率綜合

直接數(shù)字頻率綜合技術(shù),是一項基于大規(guī)模數(shù)字集成電路的技術(shù)。它是在外部控制命令下,直接由查表得出當前所需要的頻率和相位碼,經(jīng)數(shù)模轉(zhuǎn)換輸出相應(yīng)的模擬信號。它主要的特點是頻率轉(zhuǎn)換快,頻率點數(shù)多,而且頻率分辨率很高。但是,由于數(shù)字集成電路速度和奈奎斯特原理的限制,其輸出信號頻率不高,輸出信號頻譜雜散也較大,在較寬的工作范圍時,不能達到實用要求。

三種頻率合成技術(shù)的技術(shù)特性如表1所示。從表中可以看出,采用單一的頻率合成技術(shù),目前都難以達到所需超高速頻率合成器的要求。因此必須采用它們的組合形式,取長補短。組合方法常用的主要有DDS+PLL頻率合成和DDS+DS頻率合成方法,下面分別介紹。

表1 三種頻率合成技術(shù)的技術(shù)特性

1.4 基于DDS的組合式跳頻頻率合成器

1.4.1 DDS+PLL頻率合成方法

1) DDS激勵PLL的間接頻率合成方法[1, 2]

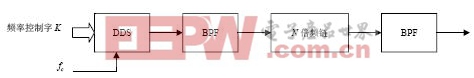

將PLL設(shè)計成N倍頻環(huán),DDS輸出通過帶通濾波器BPF直接作為PLL的參考信號。

DDS和PLL結(jié)合后,通過合理地選擇頻率控制字K、系統(tǒng)時鐘fc以及可變分頻比N,可以將DDS輸出頻率倍頻到合成器工作頻段。加入帶通濾波器可以有效地抑制DDS的寬帶頻率雜散。系統(tǒng)原理如圖1所示。

圖1 DDS激勵PLL系統(tǒng)方案原理框圖

2) PLL內(nèi)插DDS系統(tǒng)方法[1]

DDS激勵PLL的間接頻率合成方法,DDS輸出的帶內(nèi)雜散經(jīng)過倍頻后,存在著頻譜純度惡化的缺點。為充分發(fā)揮PLL頻譜純度高的優(yōu)勢,避免DDS雜散多的弱點,利用高精度的晶體振蕩器作為PLL參考頻率源。

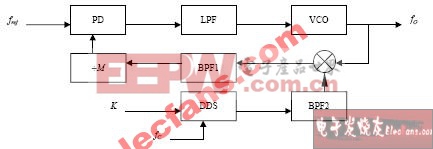

系統(tǒng)原理如圖2所示,圖中PLL作為系統(tǒng)核心,輸出合成的頻率,DDS插入到鎖相環(huán)內(nèi),與VCO輸出混頻后反饋至PD。

圖2 PLL內(nèi)插DDS系統(tǒng)原理框圖

雖然該方案避免了DDS輸出的帶內(nèi)雜散倍頻后頻譜純度惡化的問題,頻譜純度優(yōu)于DDS激勵PLL方案。但是,在反饋支路內(nèi)引入混頻器和帶通濾波器,增加了電路復(fù)雜度和調(diào)試難度。

由于DDS+PLL頻率合成方法都是基于鎖相環(huán)系統(tǒng),它是一個惰性環(huán)節(jié),鎖定時間較長,頻率合成器的頻率轉(zhuǎn)換時間一般要長達幾十微秒以上,因此DDS+PLL的實現(xiàn)方法的系統(tǒng)輸出頻率捷變速率不高,不適合高速跳頻頻率合成器的技術(shù)要求

1.4.2 DDS+DS頻率合成方法

DDS與DS相結(jié)合,利用模擬倍頻器替代PLL,克服了DDS+PLL頻率合成器的頻率轉(zhuǎn)換時間長的弱點。在該方案里,用DDS作為頻率合成器核心部件,產(chǎn)生足夠多離散頻點,然后利用多個倍頻器和濾波器組成的倍頻鏈提高DDS輸出頻率,同時拓展了DDS輸出帶寬。系統(tǒng)方案原理如圖3所示。圖中插入帶通濾波器抑制帶外的雜散,提高了頻譜純度。

圖3 DDS+DS系統(tǒng)方案原理框圖

盡管本方案帶通濾波器只能濾掉帶外雜散,帶內(nèi)雜散經(jīng)過倍頻后造成頻率純度有所惡化,但是DDS+DS方法在頻率轉(zhuǎn)換速率比DDS+PLL方法更具有優(yōu)勢,有利于高速跳頻合成器的實現(xiàn)。然而,在保證頻率高速切換前提下,如何提高頻率合成器的頻譜純度是本方案實現(xiàn)的難點。

模擬信號相關(guān)文章:什么是模擬信號

濾波器相關(guān)文章:濾波器原理

濾波器相關(guān)文章:濾波器原理

評論