Hi3510工作原理,Hi3510 -H.264 BP算法的

Hi3510是海思公司推出的一款基于H.264 BP算法的視頻壓縮芯片,該芯片采用ARM+DSP+硬件加速引擎的多核高集成度的SoC構架,具備強大的視頻處理功能。可實現DVD畫質的實時編碼性能,能自適應各種網絡環境,確保畫面的清晰度和實時性,低碼率的H.264編碼技術極大減少網絡存儲空間,并通過集成DES/3DES加解密硬件引擎確保網絡安全。Hi3510采用0.13μm工藝、LFBGA400封裝,大小為19×19mm,引腳間距為0.8mm,片內集成了包括數字視頻接口、USB、ETH、I2S、I2C、GPIO、SPI、UART、SDRAM、DDR等接口,滿足各種應用場景的設備開發的同時能大大降低了設備的BOM成本。

Hi3510的工作原理:視頻輸入單元通過ITU-R BT.601/656接口接收由VADC輸出的數字視頻信息,并通過AHB總線把接收到的原始圖像寫入到外存(SDR SDRAM或DDR SDRAM)中;視頻編解碼器從外存中讀取圖像,進行運動估計(幀間預測)、幀內預測、DCT變換、量化、熵編碼(CAVLC+Exp-Golomb)、IDCT變換、反量化、運動補償等操作,最后將符合H.264協議的裸碼流和編碼重構幀(作為下一幀的參考幀)寫入到外存中;視頻輸出單元從外存中讀取圖像并通過ITU-R BT.601/656接口送給VDAC進行顯示,應用的需求不同,視頻輸出單元從外存中讀取的圖像內容也不同,當需要對輸入圖像進行預覽時,視頻輸出單元從外存中讀取原始圖像,當需要觀察視頻編碼器的編碼效果時,視頻輸出單元從外存中讀取編碼重構幀;ARM對視頻編碼器輸出的碼流進行協議棧的封裝,然后送網口發送,以實現視頻點播業務。

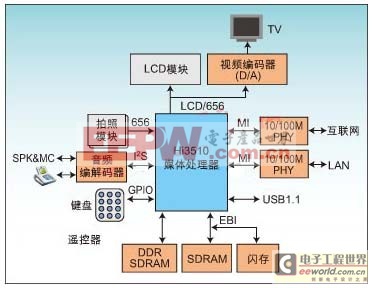

如圖1所示,該芯片由ARM+DSP+視頻編解碼加速器+圖形引擎縮放器的核心構成,集成了豐富的外圍接口,并內部集成包括如數字水印、DES/3DES算法,使得單芯片能適應基乎所有的工作,降低與其它芯片配合的開發難度,也免除廠商對算法等標準部分的內容進行重復開發,大大降低了設備廠商的投入門檻。配合海思不同應用形態的開發包,可以開發出PMP、可視電話、網絡監控、PVR、可視對講等各種產品。

圖1:Hi3510 H.264音視頻編解碼SoC邏輯框圖。

Hi3510編解碼方案的實現

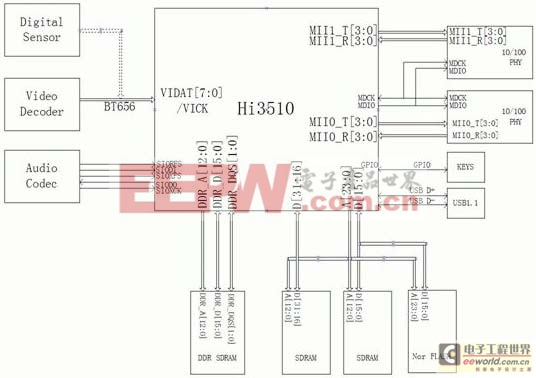

作為SoC架構的編解碼芯片,Hi3510在設計時充分考慮到兼容性和使用的方便性。支持幾乎所有的公司生產的系列AD/DA芯片。Hi3510既可以作為獨立的編碼器工作,也可以作為獨立的解碼器工作,也可以同時編解碼工作,充分考慮到了編解碼市場的各種應用場合。Hi3510是一個典型的多應用的單芯片解決方案,大大降低了設備的BOM組成和成本。如圖2所示為芯片同時編解碼的應用。

圖2:Hi3510是一款典型的多應用的單芯片解決方案。

i3510編解碼的應用

Hi3510自帶的Linux操作系統(同時支持Vxworks、WinCE等開放式操作系統)和ARM處理器,使得芯片除了編解碼功能外,還可以實現許多豐富的應用功能開發。如圖2所示,只要附加一片普通AD就可實現復合視頻信號的數字化、壓縮和存儲和傳輸的功能。Hi3510開發包提供上層API接口,就可以調用實現所有的芯片功能,并能開發自己的個性化功能。圖3為芯片的編碼方案的應用設計。

圖3:Hi3510芯片編碼方案的應用設計。

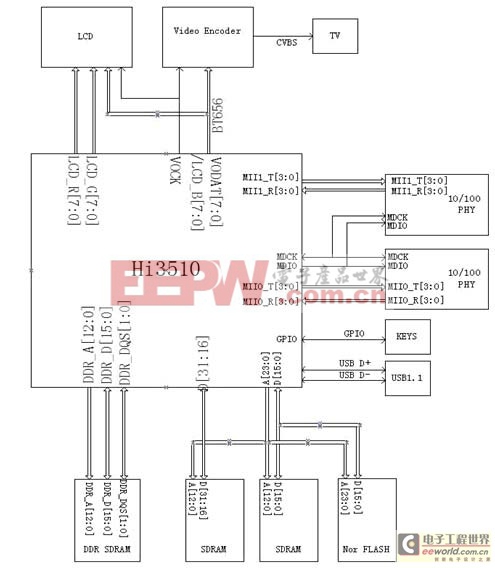

而解碼器應用在架構設計上與編碼器相同(方便方案可保持一致性,可實現一套硬件滿足不通需求,只需要軟件升級)。解碼器只需要配搭DA芯片(如果是LCD數字屏幕可以節省該芯片),就可實現把數據碼流解碼的作用,并且通過GUI或者OSD實現用戶人機互動的菜單操作,實現PMP等類似功能的產品應用。圖4為芯片的解碼方案的應用設計。

圖4:Hi3510芯片解碼方案的應用設計。

本文小結

H.264標準的應用,為視頻的網絡傳輸,尤其是低帶寬下(如無線傳輸方式)的傳輸提供了技術支持。在信息爆炸的今天,市場要求設計人員推出產品的速度越來越快,而且為了保持產品的競爭力,在產品價格、產品應用功能特點上要保持足夠優勢,尤其是在多媒體市場領域。海思的SoC芯片在提供了標準算法的基礎上,給予設計人員最大的靈活度以設計合適的產品,大大降低了廠商的投入成本,縮短了廠商的推出新產品的時間,為贏得市場做準備。

評論