高可靠性掉電保護(hù)電路設(shè)計(jì)

摘要提出掉電保護(hù)與系統(tǒng)復(fù)位同時(shí)作用,實(shí)現(xiàn)高度可靠的掉電保護(hù)電路的設(shè)計(jì)原理。介紹了ADM691微處理器監(jiān)控電路特性及其構(gòu)成的掉電保護(hù)電路。

關(guān)鍵詞微處理器監(jiān)控電路掉電保護(hù)

1問題的提出

在智能儀表及過程控制中常常要用掉電保護(hù)電路以長(zhǎng)時(shí)間保存實(shí)時(shí)參數(shù)。通常可采用E2PROM、FLASH MEMORY以及以隨機(jī)存儲(chǔ)器為基礎(chǔ)內(nèi)置電池的非易失性芯片來實(shí)現(xiàn)。E2PROM、FLASH MEMORY屬于可在線修改的ROM器件,它解決了應(yīng)用系統(tǒng)中實(shí)時(shí)參數(shù)掉電后長(zhǎng)時(shí)間保存的難題,但這類芯片寫入速度慢,一般為毫秒級(jí),擦寫次數(shù)有限,一般為萬次級(jí),有些器件擦寫次數(shù)能達(dá)到百萬次,但對(duì)某些應(yīng)用系統(tǒng)而言,其寫入次數(shù)仍然是有限的。因此這類芯片只能用在需要保護(hù)的數(shù)據(jù)量小且寫入不頻繁的系統(tǒng)中。對(duì)那些需要大容量高速反復(fù)保存實(shí)時(shí)參數(shù)的應(yīng)用系統(tǒng),只能用隨機(jī)存儲(chǔ)器RAM加掉電保護(hù)電路來實(shí)現(xiàn)。掉電保護(hù)電路一般由低功耗的CMOS-RAM、供電電路及控制電路組成。供電電路保證在系統(tǒng)正常時(shí)由電源給RAM供電,系統(tǒng)掉電時(shí)自動(dòng)轉(zhuǎn)換到由備用電池給RAM供電;控制電路保證在電源供電時(shí)RAM正常讀寫,電池供電時(shí)RAM處于保護(hù)狀態(tài),特別要防止在系統(tǒng)上電/掉電過程中的瞬間干擾信號(hào)對(duì)RAM芯片的寫入而改變RAM中的數(shù)據(jù)。基于RAM的掉電保護(hù)電路既具有RAM的高速寫入、寫入次數(shù)無限制的特點(diǎn),又能象ROM那樣長(zhǎng)時(shí)間保存數(shù)據(jù),因此得到了廣泛的應(yīng)用。實(shí)現(xiàn)上述原理的掉電保護(hù)方法很多,某些廠商甚至以RAM為基礎(chǔ)內(nèi)置電池,開發(fā)出了自掉電保護(hù)芯片。用這類單獨(dú)的掉電保護(hù)芯片或電路構(gòu)成的應(yīng)用系統(tǒng),在實(shí)際應(yīng)用中有時(shí)出現(xiàn)工作不穩(wěn)定現(xiàn)象。經(jīng)分析發(fā)現(xiàn):若系統(tǒng)電源的變化使RAM先處于保護(hù)狀態(tài),而系統(tǒng)尚未復(fù)位,微處理器正常工作,此時(shí)對(duì)RAM進(jìn)行讀寫操作,因其已處于保護(hù)狀態(tài),必定發(fā)生數(shù)據(jù)讀不出寫不進(jìn)的現(xiàn)象,引發(fā)系統(tǒng)故障。對(duì)于這種微處理器復(fù)位電平與掉電保護(hù)電平不一致而影響系統(tǒng)正常工作的問題,我們提出了用微處理器監(jiān)控電路把系統(tǒng)復(fù)位與掉電保護(hù)聯(lián)系在一起的解決方案。系統(tǒng)復(fù)位時(shí)存儲(chǔ)器處于保護(hù)狀態(tài),系統(tǒng)工作時(shí)存儲(chǔ)器處于可以正常讀寫,從而有效地解決了上述問題。下面介紹利用ADM691微處理器監(jiān)控電路按上述原理實(shí)現(xiàn)的高可靠性的掉電保護(hù)電路。

2ADM691芯片介紹

ADM691是AD公司生產(chǎn)的一種高性能微處理器電源監(jiān)視電路,其功能包括微處理器復(fù)位,備用電池切換,看門狗電路,CMOS-RAM寫入保護(hù)及電源故障告警等。

2.1芯片主要特點(diǎn)

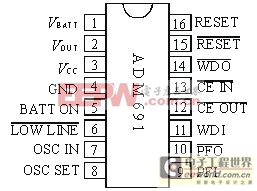

2.2芯片引腳及功能 ADM691為16腳DIP和SO封裝,引腳如圖1所示。各引腳功能如下: (1)VBATT備份電池輸入; |  圖1ADM691引腳 |

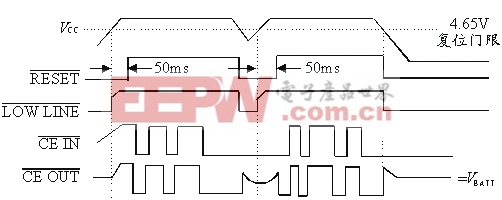

2.3ADM691復(fù)位時(shí)序 ADM691的復(fù)位時(shí)序如圖2所示。 |

圖2ADM691復(fù)位時(shí)序 |

3掉電保護(hù)電路設(shè)計(jì)

3.1硬件設(shè)計(jì)

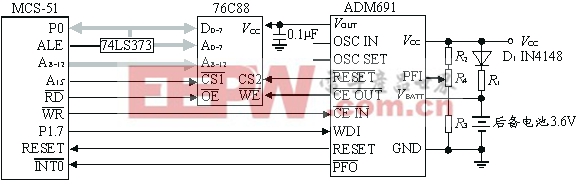

| 圖3給出了MCS-51單片機(jī)應(yīng)用系統(tǒng)中ADM691與76C88組成的掉電保護(hù)電路原理圖。 |

圖3MCS-51系統(tǒng)掉電保護(hù)電路原理圖 76C88是CMOS型的RAM芯片,其容量為8Kbit,它有兩個(gè)片選端 上電過程:當(dāng)Vcc從0V上升到復(fù)位門限4.65V時(shí), 正常工作:在此狀態(tài)下,CS2為高電平, 掉電過程:當(dāng)VCC從正常電壓下降到復(fù)位門限4.65V時(shí), 對(duì)多數(shù)應(yīng)用系統(tǒng),上電復(fù)位后程序從頭開始即能滿足要求,但對(duì)某些系統(tǒng)如由多道工序組成的流水線控制系統(tǒng),突然停電后再來電時(shí)應(yīng)接著原來的工序往下執(zhí)行,這就要求計(jì)算機(jī)記錄停電瞬間的系統(tǒng)參數(shù),重新來電時(shí)根據(jù)記錄的參數(shù)繼續(xù)往下執(zhí)行。利用ADM691的電源報(bào)警功能,能方便地達(dá)到這一目的。分析圖3可知適當(dāng)調(diào)節(jié)R4,當(dāng)VCC下降到4.80V時(shí), |

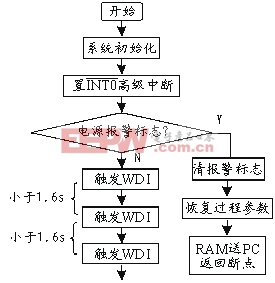

3.2軟件設(shè)計(jì)

| 圖3所示單片機(jī)系統(tǒng)的軟件可分成主程序和電源報(bào)警中斷服務(wù)程序兩部分。主程序中必須插入指令經(jīng)常觸發(fā)WDI,且間隔時(shí)間不能超過1.6s,報(bào)警中斷必須設(shè)置為非屏蔽中斷 |

(a)主程序流程 |

(b)電源報(bào)警中斷服務(wù)程序流程 |

圖4 軟件流程圖 4結(jié)束語 將系統(tǒng)復(fù)位與掉電保護(hù)結(jié)合起來,能有效的解決RAM保護(hù)與系統(tǒng)復(fù)位不協(xié)調(diào)引起的系統(tǒng)工作不穩(wěn)定現(xiàn)象,以ADM691微處理器監(jiān)控電路構(gòu)成的單片機(jī)掉電保護(hù)電路,在電腦加油機(jī)等系統(tǒng)中應(yīng)用表明,效果十分理想。 |

評(píng)論