基于DDS的調制信號發生器的設計

dds原理與ad9852的結構

基本的dds是在高速存儲器中放入正弦函數-相位數據表格,經過查表操作,將讀出的數據送到高速dac產生正弦波。常用的可編程dds系統如圖1所示。

dds系統由頻率控制字、相位累加器、正弦查詢表、d/a轉換器和低通濾波器組成。參考時鐘一般為高穩定度的晶體振蕩器,其輸出用于同步dds各組成部分的工作。

對于計數容量為2的相位累加器和具有m個相位取樣點的正弦波波形存儲器,若頻率控制字為k,輸出信號頻率為fo,參考時鐘頻率為fc,則dds系統輸出信號的頻率為:

ad9852是由adi公司生產的高性能dds芯片,主要由dds核心、寄存器、dac、數字乘法器、反辛格函數濾波器、比較器、i/o接口等電路組成。其系統功能框圖如圖2所示。

信號的產生

信號的產生

am信號的產生

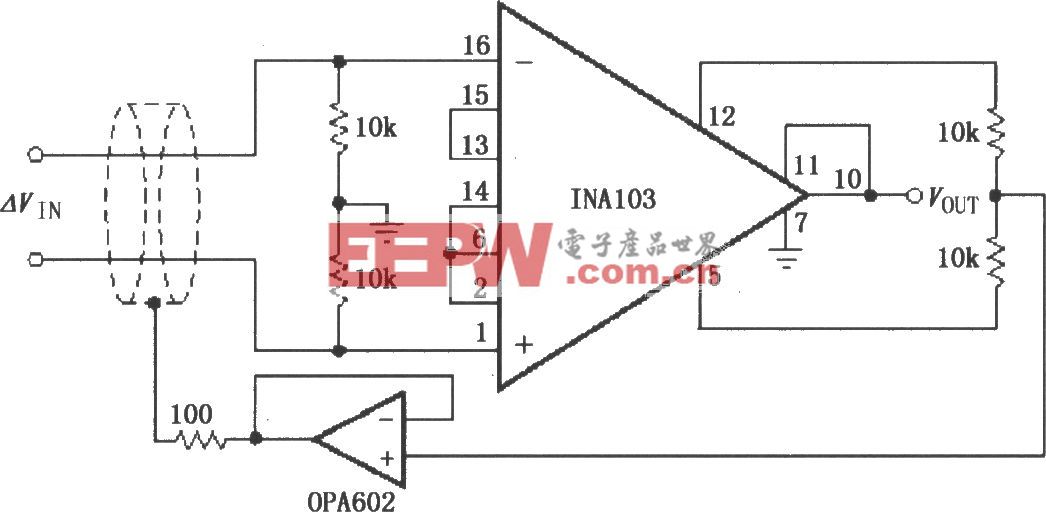

設需要產生一個載波頻率為f0,調制頻率為f 的幅度調制信號,則給ad9852輸入一個48位的頻率控制字,產生一個頻率為f0的固定幅度的載波。ad9852可以通過數字乘法器控制輸出信號的幅度,要產生一個調制頻率為f 的振幅調制信號,只需產生一系列隨著調制信號幅度變化的幅度控制字,則可直接產生數字式的調幅波。am信號產生原理如圖3所示。

fm信號的產生

fm信號的產生

根據(1)式,通過改變頻率控制字k,可以迅速改變輸出信號的頻率。因此,fm信號的產生和前面的am信號產生相似,按照調制信號幅度的變化,實時改變頻率控制字使輸出的頻率隨調制信號的幅度變化。

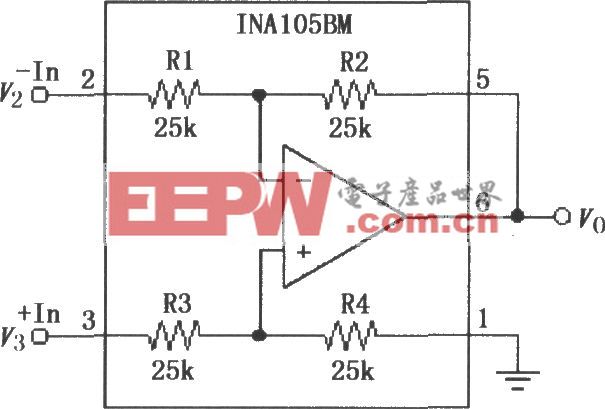

特別地,ad9852通過改變工作模式,可以產生線性調頻信號(chirp),通過改變時間步進量(斜率計數器)和頻率步進量( 頻率字)來產生不同斜率,從而實現非線性掃頻。fm信號產生原理如圖4所示。

二進制psk信號的產生

兩點(二元或兩相位)相移鍵控是在預先設置好的兩個14位相移量中快速切換。其控制信號為芯片的一個管腳“bpsk”,“bpsk”端的邏輯狀態選擇相移量,當為低時,選擇相位1;為高時,選擇相位2。在“bpsk”上輸入巴克碼信號,則輸出信號為二相巴克碼信號。

二進制ask信號的產生

二進制ask信號的產生

dds集成芯片ad9852內部包含“通斷整形鍵控”。 “通斷整形鍵控”功能使用戶控制數模變換器的輸出幅度漸變上升和下降,可減小反沖頻譜,幅度突變會在很寬的頻譜范圍內產生沖擊,要用此功能首先使數字乘法器有效,輸出幅度漸變可在內部自動進行,也可由用戶編程控制。當數字乘法器的輸人值全0時,輸入信號乘以0,產生零幅度;數字乘法器全1時,輸入信號乘以1,是滿幅度。

系統結構

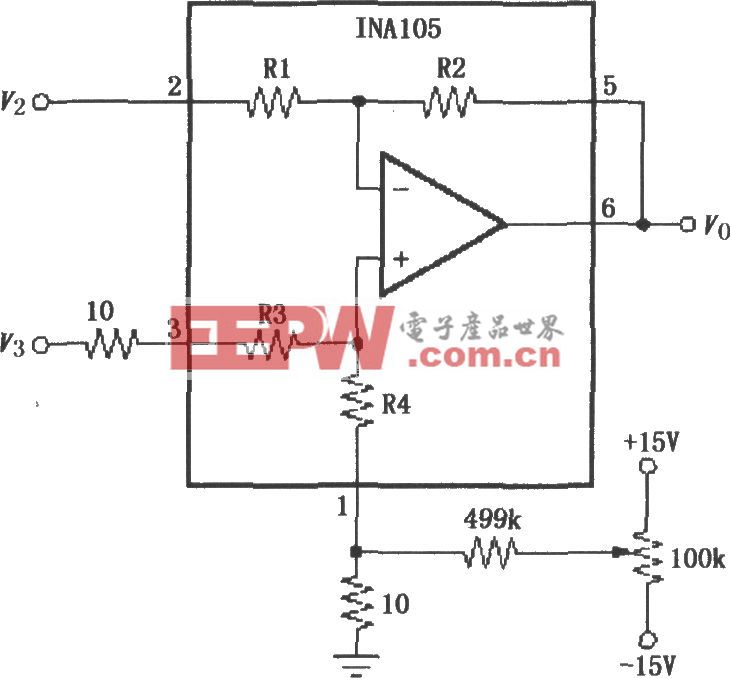

系統結構如圖6所示,由于系統是通過實時改變dds的幅度控制字和頻率控制字,來實現調幅和調頻的功能,因此對控制器的處理速度提出了較高的要求,本設計采用dsp芯片tms320c31為控制器,通過鍵盤和液晶顯示作為用戶的人機接口。由于dds輸出的信號是通過dac產生的,因此不可避免的存在一些雜散,故需在dds輸出級設計一個低通濾波器。

結束語

用ad9852實現調制信號的產生,突出地體現了直接數字頻率合成器的頻率分辨率高(達到10-6hz)、頻率轉換速度快(達到納秒級)、輸出頻譜純的特點。同時通過控制其調幅、調相、(非)線性調頻等功能,可產生多種復雜波形信號。

評論