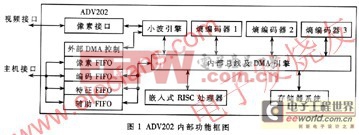

ADV202編解碼芯片介紹

ADV202的內部功能框圖如圖1所示,輸入的視頻或圖像數據進入視頻接口后經過解交錯傳輸到小波變換引擎中。在小波引擎中,每幀圖像或每個圖 塊通過5/3或9/7濾波器分解成許多子帶,生成的小波系數寫入內部寄存器中。熵編碼器將圖像數據編碼為符合JPEG2000標準的數據。內部DMA引擎 提供存儲器之間的高帶寬傳輸以及各模塊和存儲器之間的高性能傳輸。內部FIFO提供像素數據、碼流數據、特征數據和輔助數據的存儲空間,既可由外部主機通 過標準地址讀寫周期直接訪問,也可以采用DREQ/DACK協議通過DMA方式訪問或專用硬件握手機制訪問。主機接口提供16/32位的控制總線和 8/16/32位的數據傳輸總線,用于對內部寄存器的配置、控制和狀態傳遞以及壓縮數據流的傳輸。

評論