組合邏輯電路的設計

組合邏輯電路的設計與分析過程相反,其步驟大致如下:

(1)根據對電路邏輯功能的要求,列出真值表;

(2)由真值表寫出邏輯表達式;

(3)簡化和變換邏輯表達式,從而畫出邏輯圖。

組合邏輯電路的設計,通常以電路簡單,所用器件最少為目標。在前面所介紹的用代數法和卡諾圖法來化簡邏輯函數,就是為了獲得最簡的形式,以便能用最少的門電路來組成邏輯電路。但是,由于在設計中普遍采用中、小規模集成電路(一片包括數個門至數十個門)產品,因此應根據具體情況,盡可能減少所用的器件數目和種類,這樣可以使組裝好的電路結構緊湊,達到工作可靠而且經濟的目的。

下面舉例說明設計組合邏輯電路的方法和步驟。

例1:試用2輸入與非門和反相器設計一個3輸入(I0、I1、I2)

、3輸出(L0、L1、L2)的信號排隊電路 。它的功能是:當輸入I0為1時,無論I1和I2為1還是0,輸出L0為1,L1和L2為1;當I0為0且I1為1,無論I2為1還是0,輸出L1為1,其余兩個輸出為0;當I2為1且另外兩個均為0時,輸出 L2為1,其余兩個輸出為0。如I0、I1

、I2均為0,則L0、L1、L2也均為0。

解:

(1)根據題意列出真值表如下:

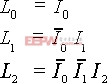

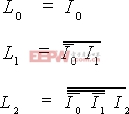

(2)根據真值表寫出各輸出邏輯表達式:

(3)根據要求將上式變換為與非形式:

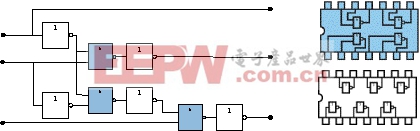

由此可畫出邏輯圖,如下圖所示。該邏輯電路可用一片內含四個2輸人端的與非門(圖中藍灰色部分)(比如74LS00)和另一片內含六個反相器(74LS04)的集成電路組成。原邏輯表達式雖然是最簡形

式,但它需一片反相器和一片3輸入端的與門才能實現(見下圖),器件數和種類都不能節省,而且三輸入端的與門器件不如二輸入端的與非門常見。由此可見,最簡的邏輯表達式用一定規格的集成器件實現時,其電路結構不一定是最簡單和最經濟的。設計邏輯電路時應以集成器件為基本單元,而不應以單個門為單元,這是工程設計與理論分析的不同之處。

例2 試設計一可逆的4位碼變換器。在控制信號C=1時,它將8421碼轉換為格雷碼;C=0時,它將格雷碼轉換為8421碼。

解:

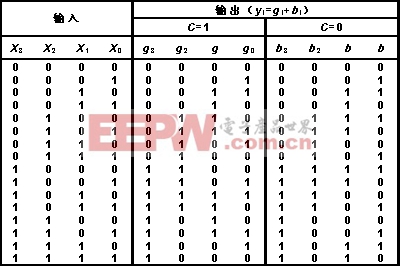

(1)列出真值表如下:

當C=l時,輸入X3X2X1X0作為8421碼,對應的輸出g3g2g1g0為格雷碼;

當C=0時,輸入則作為格雷碼,對應的輸出b3b2b1b0為8421碼。此時,X3X2X1X0作為格雷碼的排列順序體現在它與b3b2b1b0的——對應關系。

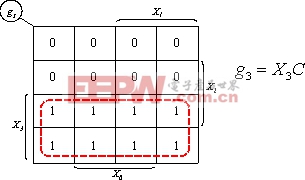

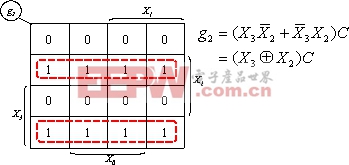

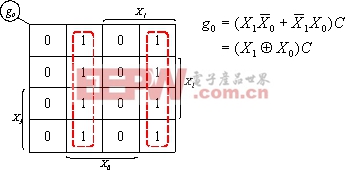

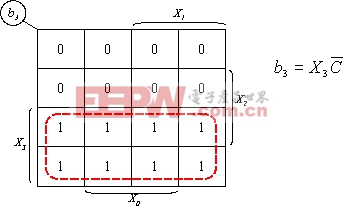

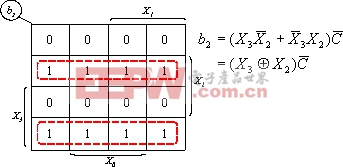

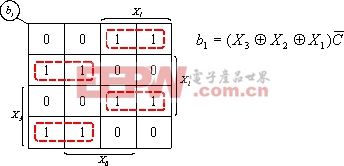

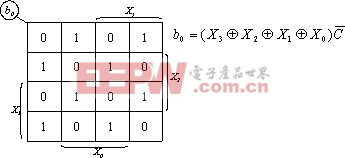

(2)分別畫出C=l和C=0時各輸出函數的卡諾圖和對應的輸出邏輯表達式如下:

C=1時有:

C=0時有:

(3)寫出總的輸出邏輯表達式:

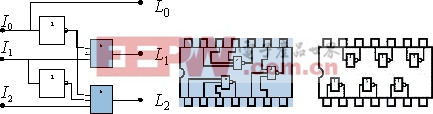

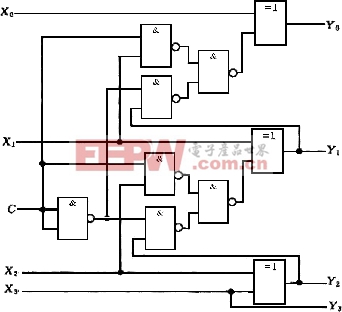

(4)畫出邏輯圖:

從以上邏輯表達式和邏輯圖可以看出,用異或門代替與門和或門能使邏輯電路比較簡單。在化簡和變換邏輯表達式時,應盡可能使某些輸出作為另一些輸出的條件,例如,利用Y2作為Y1的一個輸入,Yl又作為Y0的一個輸入,這樣可以使電路更簡單。在化簡時,若注意綜合考慮,使式中的相同項盡可能多,則可以使電路得到簡化。此外,我們還將與或換成與非形式,從而減少了門電路的種類 。該邏輯電路可由兩片各含四個2輸入端的與非門(740)和一片內含四個異或門(7486)的集成電路組成。

評論