NMOS邏輯門電路

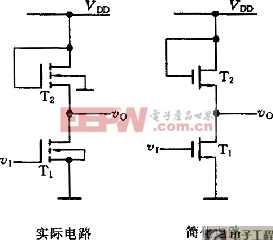

上圖是表示NMOS反相器的原理電路,其中T1為工作管,T2為負載管,二者均屬增強型器件。若T1和T2在同一工藝過程中制成,它們必將具有相同的開啟電壓VT。從圖中可見,負載管T2的柵極與漏極同接電源VDD,因而T2總是工作在它的恒流區,處于導通狀態。當輸入vI為

高電壓(超過管子的開啟電壓VT)時,T1導通,輸出vO;為低電壓。輸出低電壓的值,由T1,T2兩管導通時所呈現的電阻值之比決定。通常T1的跨導gm1遠大于T2管的跨導gm2,以保證輸出低電壓值在+1V左右

。當輸入電壓vI為低電壓(低于管子的開啟電壓VT)時,T1截止,輸出vO為高電壓。由于T2管總是處于導通狀態,因此輸出高電壓值約為(VDD—VT)。通常gm1在100~200 之間,而gm2約為5~15

之間,而gm2約為5~15 。T1導通時的等效電阻Rds1約為3~10kΩ,而T2的Rds2約在100~200kΩ之間

。T1導通時的等效電阻Rds1約為3~10kΩ,而T2的Rds2約在100~200kΩ之間

。負載管導通電阻是隨工作電流而變化的非線性電阻。

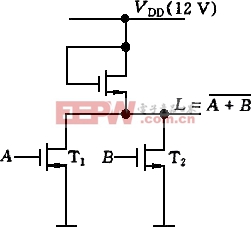

在NMOS反相器的基礎上,可以制成NMOS門電路。下圖即為NMOS或非門電路。只要輸入A,B中任一個為高電平,與它對應的MOSFET導通時,輸出為低電平;僅當A、B全為低電平時,所有工作管都截止時,輸出才為高電平。可見電路具有或非功能,即

或非門的工作管都是并聯的,增加管子的個數,輸出低電平基本穩定,在整體電路設計中較為方便,因而NMOS門電路是以或非門為基礎的。這種門電路不像TTL或CMOS電路作成小規模的單個芯片 ,主要用于大規模集成電路。

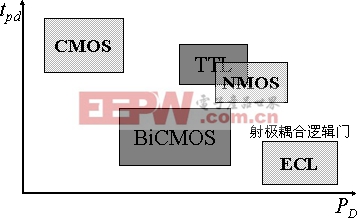

以上討論和分析了各種邏輯門電路的結構、工作原理和性能,為便于比較,現用它們的主要技術參數傳輸延遲時間Tpd和功耗PD綜合描述各種邏輯門電路的性能,如圖所示。

評論