譯碼器

一、二進制譯碼器

二、譯碼器CT74LS138

1.邏輯圖。

2.真值表。

3.邏輯功能:

4.全譯碼器:

5.功能擴展

6.4.2 二-十進制譯碼器

一、二一十進制譯碼器

二、4線一10線譯碼器CT74LS42

1.邏輯圖。

2.真值表。

3.邏輯函數式

4.功能變化

6.4.4 用譯碼器實現組合邏輯函數

一、實現原理:

二、實例

6.4 譯碼器

課堂討論:日常生活中什么地方用到了譯碼器?

譯碼是編碼的逆過程。

譯碼:將表示特定意義信息的二進制代碼翻譯出來。

譯碼器:實現譯碼功能的電路。

二進制譯碼原則:用n位二進制代碼可以表示![]() 個信號

個信號

則,對n位代碼譯碼時,應由 ![]() 來確定譯碼信號位數N。

來確定譯碼信號位數N。

提問:8位電話號碼能供多少用戶使用?(電話號碼為十進制)

6.4.1 二進制譯碼器

一、二進制譯碼器:將輸入二進制代碼譯成相應輸出信號的電路。

二、MSI譯碼器CT74LS138

由于它有3個輸入端、8個輸出端,因此,又稱3線一8線譯碼器。

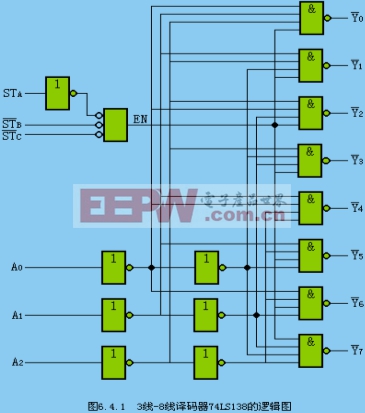

1.邏輯圖。

輸入端:A2 、A1 、A0 ,為二進制代碼;

輸出端:![]() ,低電平有效;

,低電平有效;

使能端:STA(高電平有效)、![]() (低電平有效)和

(低電平有效)和 ![]() (低電平有效),

(低電平有效),

且![]() 。

。

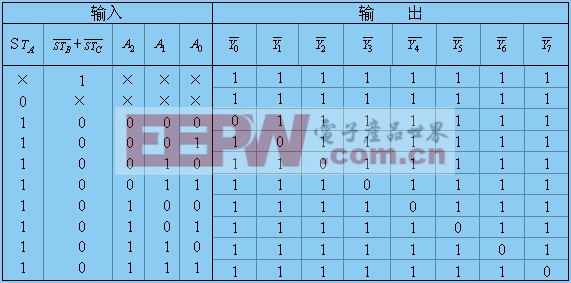

2.真值表。

表6.4.1 3線一8譯碼器CT74LS138的真值表

現代教學方法與手段:用DLCCAI演示MSI 器件74LS138的功能。(5分鐘)

3.邏輯功能:

(1)當STA=0,或![]() +

+![]() =1時,EN=0,譯碼器禁止譯碼,輸出

=1時,EN=0,譯碼器禁止譯碼,輸出![]() 都為高電平1。

都為高電平1。

(2)當STA=1且![]() +

+![]() =1時,EN=1,譯碼器工作,輸出低電平0有效。

=1時,EN=1,譯碼器工作,輸出低電平0有效。

這時,譯碼器輸出![]() 由輸入二進制代碼決定

由輸入二進制代碼決定

輸出邏輯函數式為

4.全譯碼器:二進制譯碼器的輸出將輸入二進制代碼的各種狀態都譯出來了。因此,二進制譯碼器又稱全譯碼器,它的輸出提供了輸入變量的全部最小項。![]()

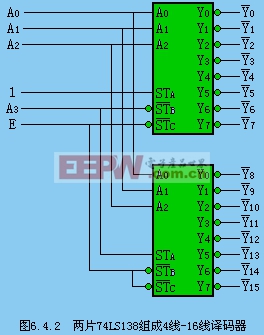

5.功能擴展:用兩片CT74LS138組成4線一16線譯碼器。(利用使能端)

CT74LS138(1)為低位片,CT74LS138(2)為高位片。并將高位片的STA和低位片的![]() 相連作A3,同時將低位片的

相連作A3,同時將低位片的![]() 和高位片

和高位片![]() 、

、![]() 相連作使能端E,便組成了4線一16線譯碼器。工作情況如下。

相連作使能端E,便組成了4線一16線譯碼器。工作情況如下。

當E=1時,兩個譯碼器都不工作,輸出![]() 都為高電平1。

都為高電平1。

當E=1時,譯碼器工作。

(1)當A3=0時,低位片CT74LS138(1)工作,這時,輸出![]() 由輸入二進制代碼A2A1A0決定。由于高位片CT74LS138(2)的STA=A3=0而不能工作,輸出

由輸入二進制代碼A2A1A0決定。由于高位片CT74LS138(2)的STA=A3=0而不能工作,輸出 ![]() 都為高電平1。

都為高電平1。

(2)當A3=1時,低位片CT74LS138(l)的![]() =A3=1不工作,輸出

=A3=1不工作,輸出![]() 都為高電平1。高位片CT74LS138(2)的STA=A3=1,

都為高電平1。高位片CT74LS138(2)的STA=A3=1,![]() =

=![]() =0,處于工作狀態,輸出

=0,處于工作狀態,輸出![]() 由輸入二進制A2A1A0決定。

由輸入二進制A2A1A0決定。

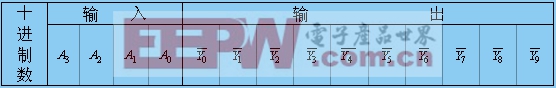

6.4.2 二-十進制譯碼器

提問:若要對8421BCD碼進行譯碼,輸出信號應有多少個?

一、二一十進制譯碼器:將4位BCD碼的十組代碼翻譯成0~9十個對應輸出信號的電路。

由于它有4個輸入端,十個輸出端,所以,又稱4線一10線譯碼器。

二、4線一10線譯碼器CT74LS42

1.邏輯圖。見教材中圖6.4.3。

輸入端:A3、A2、A1、A0 ,為4位8421BCD碼

輸出端:![]() ,低電平有效。

,低電平有效。

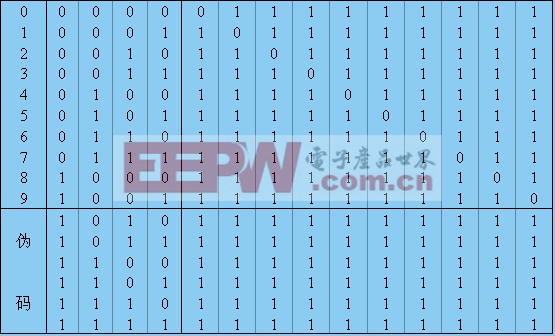

2.真值表(代碼1010~1111沒有使用,稱作偽碼。)

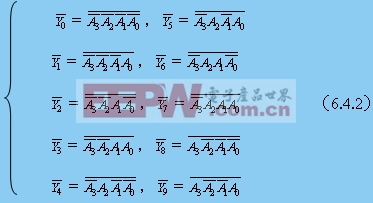

3.邏輯函數式

由式可知,當輸入偽碼1010~1111時,輸出![]() 都為高電平1,不會出現低電平0。因此,譯碼器不會產生錯誤譯碼。

都為高電平1,不會出現低電平0。因此,譯碼器不會產生錯誤譯碼。

4.功能變化:CT74LS42可作3線—8線譯碼器:輸出![]() 不用,并將 作使能端使用。

不用,并將 作使能端使用。

6.4.4 用譯碼器實現組合邏輯函數

一、實現原理:

提問:邏輯函數的標準最小項之和式?

譯碼器CT74LS138的輸出邏輯函數式?

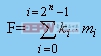

由于二進制譯碼器的輸出為輸入變量的全部最小項,即每一個輸出對應一個最小項

Yi=mi(譯碼器輸出高電平) ![]() (譯碼器輸出低電平)而任何一個n位變量的邏輯函數都可變換為最小項之和的標準式

(譯碼器輸出低電平)而任何一個n位變量的邏輯函數都可變換為最小項之和的標準式

, 的取值為0或1,

因此,用譯碼器和門電路可實現任何單輸出或多輸出的組合邏輯函數。

當譯碼器輸出低電平時,多選用與非門;當輸出為高電平時,多選用或門。

二、實例

[例6.4.1]試用譯碼器和門電路實現邏輯函數

![]()

解:(1)根據邏輯函數選用譯碼器。

由于邏輯函數Y中有A、B、C三個變量,故應選用3線一8線譯碼器CT74LS138。

其輸出為低電平有效,故選用與非門。

(2)寫出標準與—或表達式為

(3)將邏輯函數Y和CT74LS138的輸出表達式進行比較。

設A=A2、B=A1、C=A0,比較得

![]()

(4)畫邏輯電路圖。

[例6.4.2] 試用譯碼器設計一個一位全加器。它能將兩個二進制數及來自低位的進位進行相加,并產生和數與進位數。

解:(1)分析設計要求。列出真值表。

設在第i位的兩個二進制數相加,設被加數為Ai ,加數為Bi ,來自低位的進位數為Ci-1 。

輸出本位和為Si ,向高位的進位數為Ci 。

表6.4.4 全加器的真值表

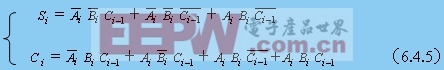

(2)根據真值表寫輸出邏輯函數為

(3)選擇譯碼器。

全加器有三個輸入信號Ai 、Bi 、Ci-1 ,有兩個輸出信號Si 、Ci 。

因此選用3線一8線譯碼器CT4LS138和兩個與非門。

(4)將Si 、Ci 式和CT74LS138的輸出表達式進行比較。

設Ai=B2、Bi=A1、Ci-1=A0 ,比較后得

(5)畫邏輯電路圖。

評論