MP3播放機雖然是可攜式多媒體(PMP)裝置中,集成技術比較單純的一種。但是,這種單純性是來自于SoC處理器的強大功能,簡化了工程師原本繁復的工作。本文將介紹成本低、功能簡單的MP3播放機系統集成技術。

MP3播放機雖然是可攜式多媒體(PMP)裝置中,集成技術比較單純的一種。但是,這種單純性是來自于SoC處理器的強大功能,簡化了工程師原本繁復的工作。當然要獲得這樣的單純性和便利性,是要付出代價的──須支付SoC處理器和操作系統軟件的授權金和權利金。這就像Wintel集團的PC解決方案一樣,雖然開發方便,可以及早量產,但是其核心的技術知識(know-how)是近似于封閉和不可探知的。 |

| |

功能單元

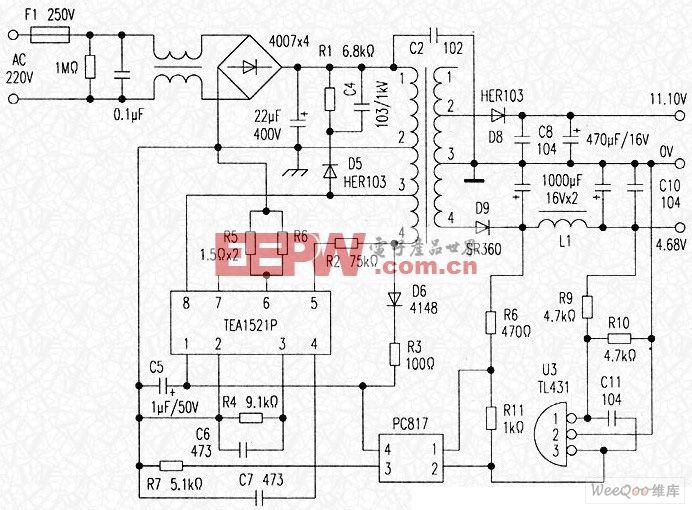

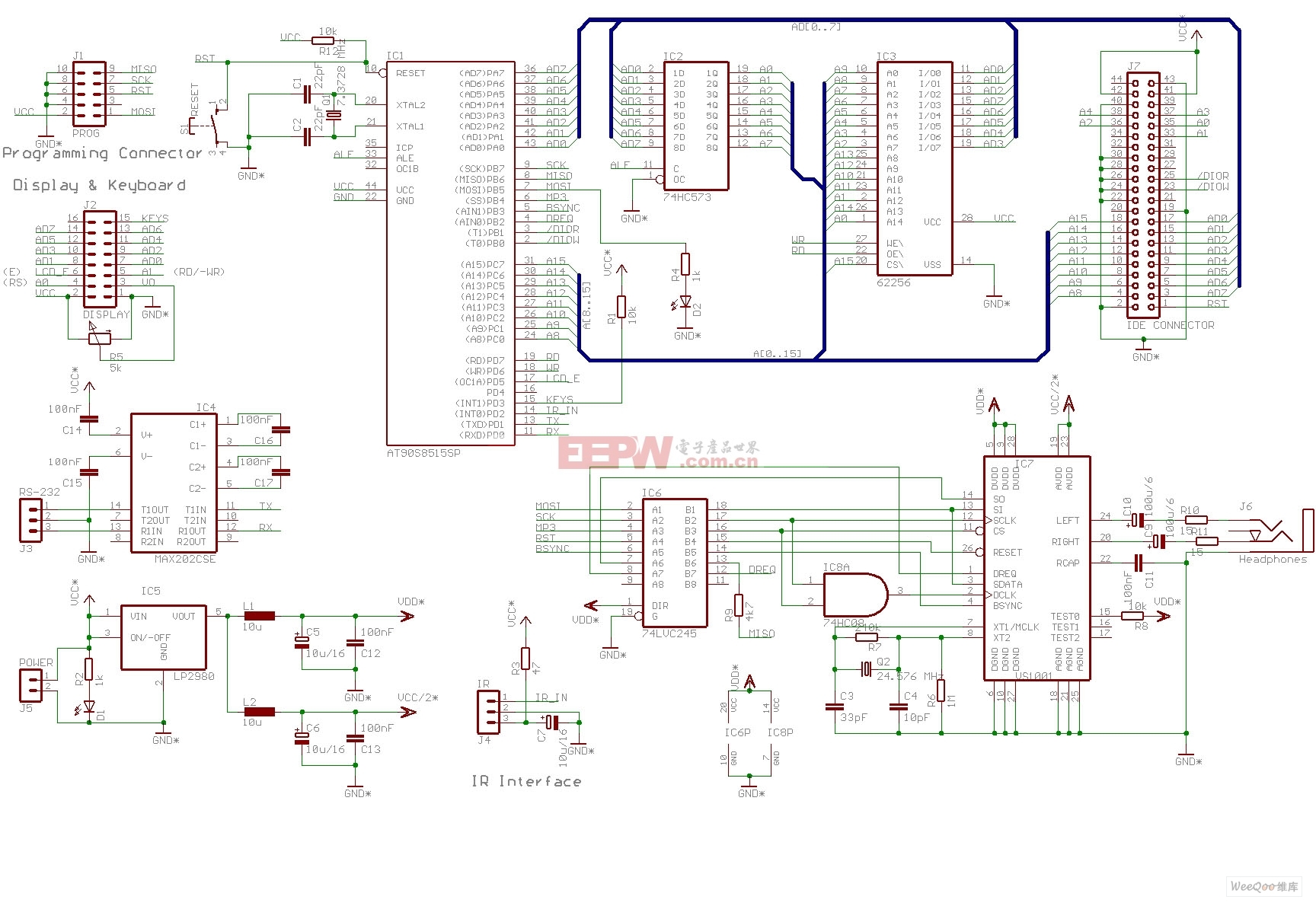

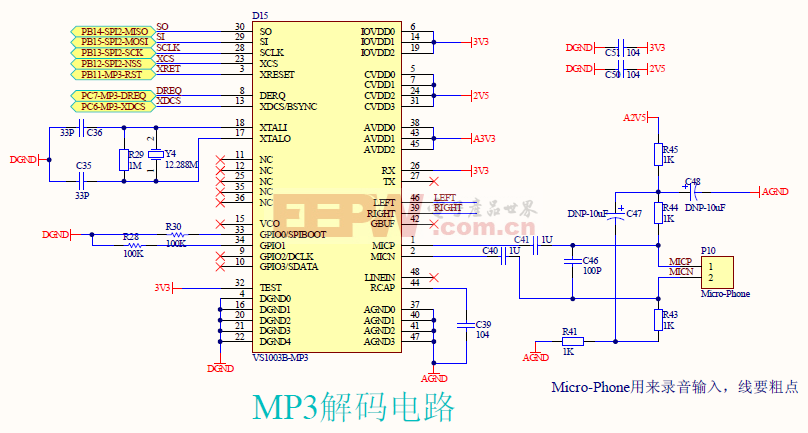

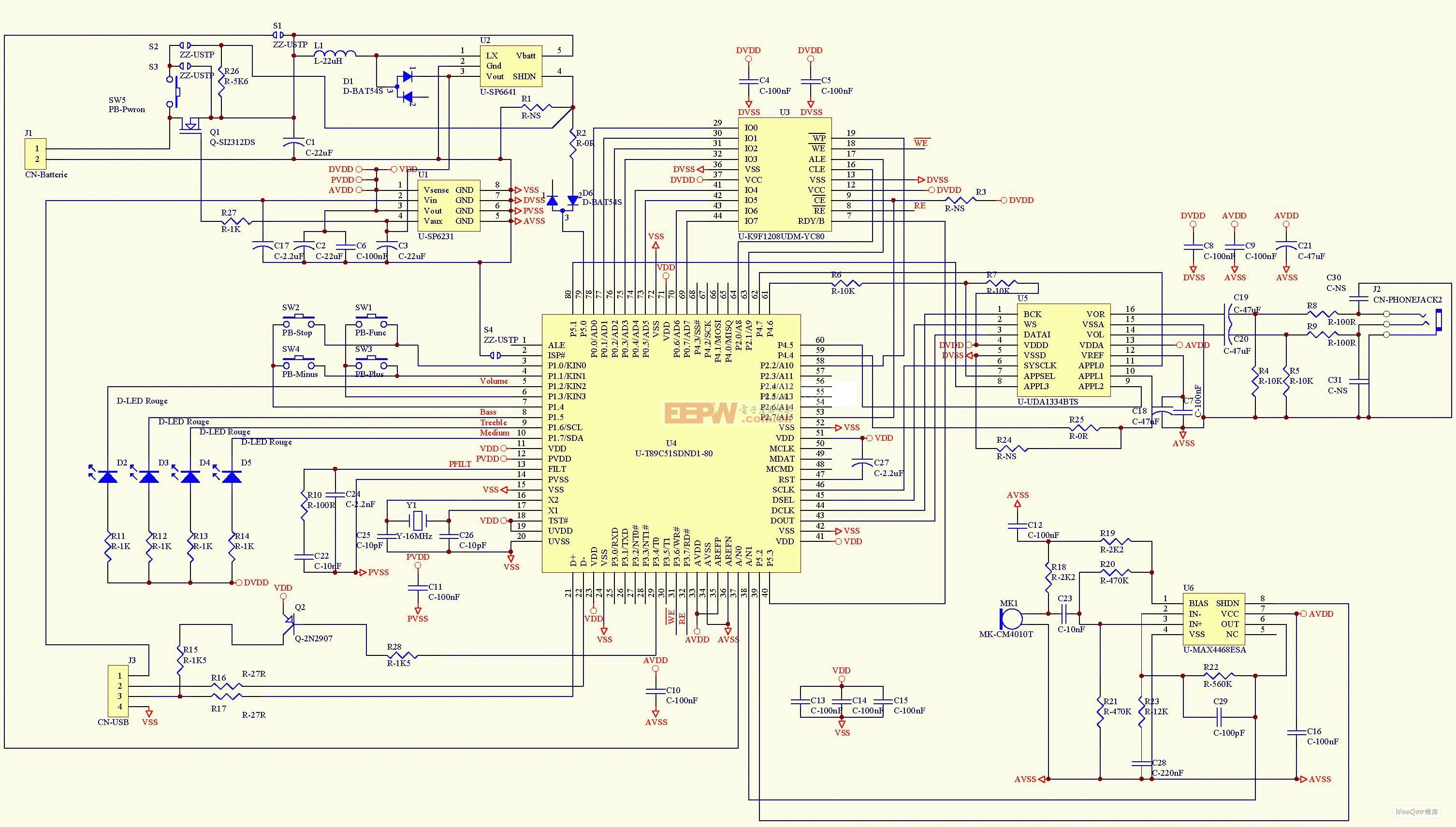

成本低、功能簡單的MP3播放機至少需要以下的基本單元:處理器/微控制器、MP3譯碼器、DMA、內存、硬盤、電源電路、DAC或I2S,LCD和鍵盤則是選項。當然還需要外接揚聲器。為了減少組件的數量、提高設計的彈性、縮小體積,可以使用FPGA來設計DMA、內存控制器、IDE控制器。如附(圖一)所示。 |

| |

FPGA電路

在附圖一的FPGA電路中,列舉其中功能比較重要者說明如下:

●主電路:這是完整的數據路徑----從微控制器總線到可共享的參數/地址映像內存、到DRAM/IDE總線。它包含了微控制器能夠存取的所有外部緩存器、事件偵測(event detection)和移動請求位(action request bits)。外部緩存器組是位于DRAM內,執行各種特定的任務;當關機時,這些緩存器將會消失。事件偵測、移動請求位都是為了讓微控制器得知目前的狀態,并采取適當的移動、或執行特定的韌體程序。

●控制用的狀態機:負責接收各種移動請求位,并使所有的控制線生效(assert),最后導致數據移動。它是一種簡單的,但大型的狀態機;平時它處于閑置和等待的狀態,直到要采取移動。所有的狀態是采用S_state_#的方式命名的。OR閘在適當的狀態下,會使正確的控制訊號生效,如附圖二所示。這個電路也包含了「優先級編碼器(priority encoder)」。在閑置狀態時,若擱置了許多個請求,則優先級編碼器可以決定哪一個要先執行。這種電路雖然有點復雜,但是它使用「一熱(one-hot)」的簡單概念。所謂「一熱」是指每一個狀態是使用一個正反器(flip-flop)實現的,在每一個狀態下,只有一個正反器是處于高值,其余都是低值,而且「熱位(hot bit)」會一直移動,直到回到閑置狀態。在DMA路徑上,具有一個正反器(也可以省略不用),當結束DMA作業的條件成立時(ISZERO),此正反器會收到「熱位」。所有的控制訊號是由OR閘產生的,只要輸入的狀態訊號群組中有一個是高值,OR閘就會輸出高值(使控制訊號生效)。例如:若(圖二)的OR2的S_RD_IDE_1或S_WR_IDE_1為高值,則IDE_ADDR的輸出也會是高值,因此IDE_ADDR生效了。不過,有一些對時間要求很嚴格的(timing critical)訊號,并不是使用OR閘產生的,它們是使用建立/重置(set/reset)緩存器產生的。建立/重置緩存器的功效和OR閘一樣,但是沒有延遲。

微控制器總線MOVX偵測

傾聽微控制器總線,當沒有MOVX指令要執行時,使DMA_OK訊號生效。當DMA_OK未生效時,優先級編碼器不會讓任何非CPU的硬件單元存取DRAM。所以,它對微控制器的讀取和寫入請求是立即響應的,不會有延遲發生。這對8051微控制器而言,是很重要的,因為8051沒有等待狀態。如果有偵測到一個MOVX作業碼,但是MOVX沒有被執行,一個31周期的定時器可以使DMA_OK再次生效。

■微控制器的地址譯碼

這些訊號生效后,可以使外部緩存器在微控制器的內存映像區域內使用。通常,這是將地址排線和REG_RD訊號或REG_WR訊號AND在一起;REG_RD和REG_WR訊號是由狀態機產生的。

■DRAM/IDE地址多任務器(mux)

在DRAM的行列式地址位(address bits)、IDE的地址位(來自于微控制器)之間,做DRAM/IDE地址腳位的切換;或為零,當執行IDE DMA的直接傳輸作業時(類似PIO)。

■MP3輸出位移緩存器(shift register)

這是16位的位移緩存器,它從IDE接口得到一個16位的字組(word),并以位移的方式將此字組送至 MP3譯碼器。

■MP3位計數器

計算位移緩存器送至MP3譯碼器的位數目。當所有的16位都被移出時,會產生一個訊號,此時,位移緩存器準備供給STA013 DMA使用,以繼續從DRAM中讀取和傳送下一個字組。

■DRAM的重清(refresh)時脈

這個電路會每15.2 ?s 產生一個脈沖,要求狀態機執行一個DRAM重清周期。此脈沖會在主電路內,建立一個請求旗標,當總線可以使用時,狀態機會開始執行重清作業,而且優先等級比較高的請求不會被擱置。

■DRAM/IDE地址緩沖器(buffer)

保存地址,這些地址是用來驅動DRAM和IDE接口。

■32-byte的SRAM內存

使用兩個16×16寬度的DRAM內存,將它們虛擬成具有地址或數據鎖定(latch)功能的SRAM。其中一個保存DRAM的分頁(page)號碼,這些分頁是映像至微控制器的地址空間0xFF00至0xFF1F的區域(DRAM_PAGE_CFG緩存器),它們和微控制器的12個地址位一起被送至DRAM/IDE地址多任務器,最后可以為DRAM的讀寫作業,產生一個唯一的地址。第二個SRAM負責保存DMA的參數值(在0xFF20至0xFF3F的區域內)。微控制器的外部內存(DRAM)空間映像如附(表一)所示。

■地址映像內存的寫入功能生效

允許對地址映像內存進行寫入作業。不過,它只允許微控制器在0xFF00至0xFF1F的內存區域寫入數據。

■DMA參數內存的寫入功能生效

允許對DMA參數內存進行寫入作業。微控制器能寫入這些參數,而且,這些參數也可以被狀態機更新,例如:在進行DMA傳輸作業時,狀態機可以改變它們。

■16位的遞增/遞減電路

在進行DMA傳輸作業時,16位的遞增/遞減可以用來更新參數值。遞增電路是為了計算DRAM的目標地址,遞減電路是為了計算字組。DMA參數內存的輸出值會被送至此電路中,而且也會被送至16個多任務器中,以允許DMA參數被轉譯成地址,就好像它們來自于微控制器的地址總線(address bus)一樣。

■零、壹和奇數值檢測器

當DMA參數值被改變時,這個電路能夠立即得知;如果DMA參數值是零、壹或奇數地址,這個電路也能夠通知狀態機。當DMA參數值是零時,狀態機會清除DMA的請求旗標,以終止DMA作業,并將「完成DMA傳輸」的中斷旗標設為1。

■微控制器的「地址鎖定致能(address latch enable;ALE)」訊號之同步

能使微控制器的ALE訊號和FPGA 的時脈同步。微控制器的其它控制訊號也是采用類似的同步機制,但是它們位于主電路中。

■2:1多任務器/4位

此電路允許在每32 byte內存內的地址,可以被內存的一般功能控制,或被微控制器的總線控制(當韌體從這些緩存器中讀出或寫入,來改變地址映像或建立DMA傳輸時)。

■2:1多任務器/8位

它被使用在IDE區塊內。它允許從微控制器的數據區域中,將數據加載至輸出緩沖器內。

■2:1多任務器/16位

當執行一個DMA周期時,利用這個電路,可以從微控制器的地址總線(一般作業),切換成DMA參數內存的地址總線。

■2:1多任務器/16位

利用這個電路可以選擇DMA參數內存的輸入值;它是在更新的DMA參數(在一個DMA周期內)和微控制器的數據總線(當微控制器寫入DMA設定值)之間做切換。單獨設計這個16位的多任務器,是因為FPGA開發工具的「可設定的邏輯區塊(configurable logic block;CLB)」之映像,無法將額外的邏輯閘納入上列的那些2:1多任務器內(如此會浪費8個CLB,并在重要的時序路徑上,增加額外的延遲時間),除非邏輯閘是在同一個電路設計圖內。

■16至8位總線,三態(tri-state)緩沖器

此三態緩沖器允許一個16位總線的任一半字節(8 bit)去驅動一個8位總線。它可以讓微控制器從寬16位的內存中讀取數據。

■8至16位總線緩沖器

連接兩個8位的總線成為一個16位總線(但FPGA開發工具并不會因此混淆)。

■8至16位總線緩沖器

連接一個8位的總線兩次,成為一個16位總線(但FPGA開發工具并不會因此混淆)。此16位總線的任一半字節都是來自于此8位總線,如附(圖三)。

■8位緩存器

一個8位緩存器,用來收集微控制器的地址位。

此外,由于不同的FPGA開發工具的性能差異,可能還需要:

●數個具有不同位數(例如:5至9位)的位移緩存器:它們在狀態機中使用。可以避免因為在同一電路設計圖內具有太多的符號,而使FPGA開發工具當機。

●正反器(在CLB中):這是唯一的CLB正反器,以一個比在FPGA開發鏈接庫(library)中還要小的符號來重設計。

●正反器(在IOB中):這是唯一的「I/O區塊(IOB)」正反器,以一個比在FPGA開發鏈接庫(library)中還要小的符號來重設計。

FPGA電路算是此MP3播放機系統中,比較復雜的一部份,一般的OEM/ODM可以指定規格委外設計。另一個OEM/ODM廠商必須注意的是韌體的設計;或許韌體也可以委外設計,但是他們必須懂得如何使用底層韌體(匯編語言)所提供的應用程序接口(API),來設計上層的使用者程序(C語言程序)。

|

| |

應用程序接口

應用程序接口至少包含:動態配置內存(memory allocation)、檔案/目錄的讀取、MP3音樂的播放、與其它外圍的通訊(包括:可當作除錯用途的串行端口、LCD顯示器…..等)。這里僅介紹動態配置內存的應用程序接口如下:

■動態配置內存

對使用者程序而言,一定需要配置內存來儲存字符串、結構、或其它項目。它的功能就像C語言里的malloc( )一樣。這里使用的是simm_malloc( ),它的原式如下所示:

●simm_id simm_malloc (unsigned int num_bytes):

分配num_bytes的DRAM內存空間,并傳回simm_id代表這個空間。simm_id不是一個指標(pointer),而是一個號碼。想要得到配置好的實際的內存空間地址,必須透過addrX函式,如下所示:

●xdata void * addr5 (simm_id addr32):映射至0x5000~0x5FFF

●xdata void * addr6 (simm_id addr32):映射至0x6000~0x6FFF

●xdata void * addr7 (simm_id addr32):映射至0x7000~0x7FFF

將simm_id所代表的內存空間映像至微控制器的地址空間,并傳回一個指標。這些函式的回傳值幾乎是使用「類型轉換(typecast)」,例如:(xdata char *)addr5(string_id)。每一個函式會分別映像至一個屬于微控制器地址空間的特殊區段。如果有任何一個指標已經被使用了,這個特殊區段就不是有效的;因此,對同一個simm_id而言,只能透過上列的3個函式,獲得3個不同的指標,而且它們不能被使用,這樣的地址空間才是有效的。

想要釋放simm_malloc( )先前配置的內存空間,必須使用下列的函式:

void simm_free (simm_id addr32)

在表一中,從0x0000至0xEFFF的區域是儲存數據用的分頁(page),其余都是緩存器。每一個分頁(或區塊)大小是4K(Bytes)。所支持的DRAM模塊大小,是從1024(4MBytes)至8192(32MBytes)個區塊。系統初始化后,這些4K大的區塊會被配置且閑置著(free)。當一組區塊被配置時,通常第一個區塊的號碼會先被用掉,后面的區塊是透過呼叫next_block( )函式來依序存取。DRAM控制器允許任何15個區塊能映像至微控制器的地址空間中,從0x0000至0xEFFF。下面條列出與分頁管理相關的函式(是以匯編語言寫成的):

●init_memory_mgr:將「內存管理者(memory manager)」初始化。它會檢測出DRAM模塊的大小,少部份的內存區塊會被保留下來,供作設計所有區塊的鏈接串行(linked list)之用。此鏈接串行可以追蹤哪些區塊是閑置的,哪些是被使用的。當應用程序需要一組區塊時,這個被保留的內存區塊就會儲存那組區塊的串行。在使用其它函式之前,必須先呼叫此函式。

●malloc_blocks:配置1個或更多個區塊(4K大的分頁),并傳回第一個區塊的號碼。若要配置一個以上的區塊,須配合使用next_block函式來擷取其它區塊。請注意,它和simm_malloc( )一樣,這些區塊并不會自動映射至微控制器的尋址空間。

●map_block:將一個區塊映射至微控制器的尋址空間。輸入分頁號碼(0~14)和區塊數量。

●free_blocks:將配置好的區塊釋放。釋放后的區塊之映射并不會自動消失。輸入第一個區塊的號碼,與它同一組的區塊都會被釋放。

●next_block:擷取一個以上的區塊時,配合malloc_blocks使用。輸入目前的區塊的號碼,它會傳回下一個區塊的號碼。

|

| |

結語

許多中小型電子公司而言,使用SoC處理器和操作系統軟件來開發PMP產品,其成本是偏高的。「低成本」似乎只是一種理想而已,因為當組件成本降低時,集成技術的成本可能會上升。集成技術需要許多種不同的技術和知識,這就像設計SoC處理器一樣,若要找到專精于各種技術領域的人才,就難免要增加人事成本了。(本文原載于零組件雜志第164期)

|

評論