AD9958高性能可雙路輸出的DDS器件

AD9958是Analog Devices公司生產的一款高性能、動態特性優異、可雙路輸出的DDS器件,每路可單獨控制頻率,相位/幅度。這種靈活性可用于校正信號之間由濾波、放大等模擬處理或PCB布局失配而引起的不平衡問題。由于兩個通道共享一個公共系統時鐘,因此它們具有固有的同步性,可支持多個設備的同步。AD9958內部集成了10 bit的輸出幅度控制,內部工作頻率高達500 MHz,使其可產生最高頻率為250MHz的雙路信號。其內部有許多用于控制輸出信號參數的控制寄存器,具有32位頻率調整分辨率、14位相位失調分辨率、10位輸出幅度可縮放分辨率,有增強數據吞吐率的串行SPI口。可工作于多種模式,支持單頻信號模式(single-tone)、調制模式(modulation mode)、線性掃頻模式(linearsweep)以及混合信號模式。可以執行高達16階的頻率、相位或幅度調制(FSK、PSK、ASK)。

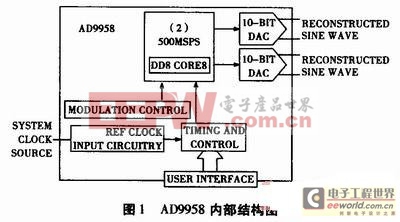

1 AD9958的結構

AD9958的串行I/O端口可支持多種配置,提供了極大的靈活性。與ADI公司以往DDS產品中提供的SPI工作模式類似,串行I/O端口提供SPI兼容工作模式。四個數據引腳(SDIO_0/SDIO_1/SDIO_2/SDIO_3)對應串行I/O的四種可編程模式,從而提供了高靈活性。AD9958采用高級DDS技術,可在低功耗下提供高性能。這款器件集成了兩個具有卓越寬帶和窄帶SFDR性能的高速10bitDAC。每個通道均具有專用的32bit頻率調諧字、14bit相位偏移和10bit輸出比例乘法器。DAC輸出以電源電壓為參考源,必須經由電阻或AVDD中心抽頭變壓器連接到AVDD。每個DAC均具有各自的可編程基準源,用于實現每個通道不同的滿量程電流。當使用REF_CLK作為輸入,并由DAC提供輸出時,這款DDS可用作高分辨率分頻器。兩個通道共用REF_CLK輸入源,REF_CLK輸入源可被直接驅動,或與高達最大值500MSPS的內置REF_CLK乘法器(PLL)配合使用。 PLL倍增因數的可編程范圍為4~20,步進為整數。REF_CLK輸入還具有振蕩電路,可將外部晶振用作REF_CLK源,晶振的頻率必須在20 MHz與30 MHz之間,晶振可與REF_CLK乘法器配合使用。

AD9958采用節省空間的56引腳LFCSP封裝。DDS內核(AVDD和DVDD引腳)采用1.8 V電源供電。數字I/O接口(sPI)在3.3 V電壓下工作,并需要將DVDD_I/O引腳(引腳49)連接至3.3 V電壓。AD9958可在-40℃~+85℃的工業溫度范圍內工作。

AD9958的內部結構如圖1所示,主要特性如下:

*兩個500 MSPS同步DDS通道

*所有通道之間獨立的頻率/相位/幅度控制

*頻率、相位和幅度變化時的延時匹配

*卓越的通道間隔離

*線性頻率/相位/幅度掃描功能

*高達16階頻率/相位/幅度調制(引腳選擇)

*內置兩個10 bit數模轉換器(DAC)

其主要應用在以下幾方面:

*捷變本振(ALO)頻率合成

*相控陣雷達/聲納

*儀器儀表

*同步時鐘

*用于AOTF(聲光可調濾波器)的RF源

*單邊帶抑制載波

*正交通信

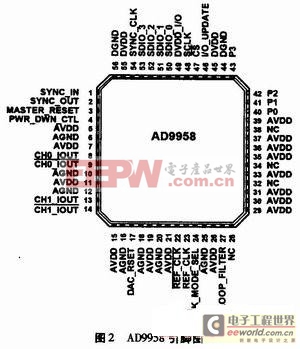

2 引腳說明

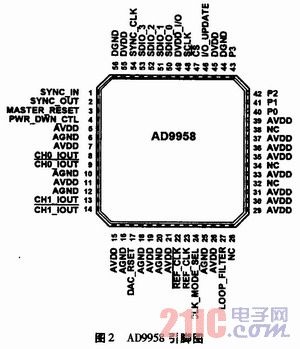

AD9958采用56腳LFCSP封裝,其引腳圖如圖2所示,其主要引腳功能如下:

SYNC_IN:同步多片AD9958的輸入信號,使用時與主器件AD9958的SYNC_OUT相連;

SYNC_OUT:同步多片AD9958的輸出信號,使用時與從器件AD9958的SYNC_IN相連;

MASTER_RESET:復位引腳,高電平有效;

PWR_DWN_CTL:電源掉電控制引腳;

CH0_IOUT、CH1_IOUT:通道0、1輸出端,無需上拉電阻,輸出范圍可達AVDD;

CH0_IOUT、CH1_IOUT:通道0、1互補輸出端,無需上拉電阻,輸出范圍可達AVDD;

DAC_RSET:DAC復位端,為DAC創建參考電流,通過一個1.91 kΩ的電阻接至AGND端;

REF_CLK、REF_CLK:參考時鐘或晶振輸入端;

CLK_MODE_SEL:振蕩器模式控制引腳,為1時使能振蕩器為REF_CLK源,為0時不使能;

LOOP_FILTER:與鎖相環環路濾波器的零點補償電路連接,此引腳與AVDD間串接一個0 Ω電阻和680pF電容。

P0,P1,P2,P3:調制數據引腳;

I/O_UPDATE:I/O口更新寄存器控制端,此引腳上升沿數據從串口緩沖器送入寄存器。

:片選端,低電平有效,允許多芯片共用SPI總線;

SCLK:I/O口讀寫時的串行數據時鐘輸入端,上升沿寫操作,下降沿讀操作;

SDIO_0:專用串行I/O口引腳;

SDIO_1,SDIO_2,SDIO_3:用作串行I/O口引腳或初始化DAC輸出幅度增減量控制引腳;

SYNC_CLK:同步時鐘輸出引腳,為系統時鐘的4分頻。

評論