基于門控時鐘的低功耗電路設計方案

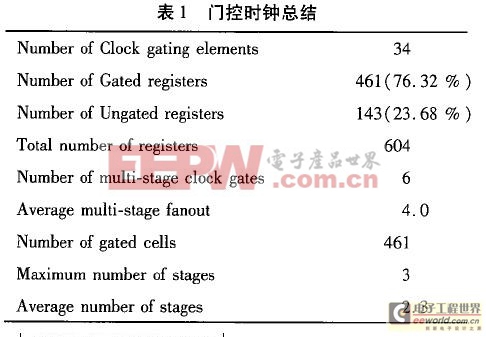

fanout的大小對功耗和時序都有影響。數值越大則表示一個門控單元可承受較多的負載,即代表越節省功耗,需要的門控單元也越少,但對門控單元輸入端建立時間的要求也就更加嚴格。位寬決定一組寄存器能被門控的最小寬度。級數則確定多級門控時鐘的最大級數。本設計在這三個參數的選取上,主要是依據設計本身對功耗的要求,結合綜合時的時序約束和單元庫中門控單元的時延信息加以估計,確定一個粗略的數值范圍。fanout的值在滿足時序的前提下,不經編譯就可確定,方法如下:首先按約束文件中的扇出值約束此處fanout,然后insert_clock_tree,加入時序約束并傳遞至門控時鐘,用re_port_clock_gating– multi_stage查看報告,重點關注第1項。發現fanout按約束文件取值為15時,門控單元的數目達到61個, fanout取值為20或更高時,門控單元數目為41,見表1,而被門控的寄存器數目卻保持不變,多級門控單元的數目也由fanout取值為15時的7級減小到當前的6級。由于門控單元也會消耗相當大功耗,因此在被門控的寄存器數目相同的情況下門控單元數越少就越節省功耗。因此確定fanout為20。

num_stages最初取值為2,插入門控時鐘后的報告顯示平均級數為1. 4,其值增至3時,平均級數為2. 3,如表1 所示。從對時鐘網絡的平衡性來講,stage值為2時要優于取值為3時的情況,但結合其后的編譯,綜合考慮時序面積功耗因素,折衷考慮選定stage為3。

bitwidth初值為3,經過編譯,得出了功耗和延時信息。以此為基準,根據設計改變bitwidth數值,然后再編譯,對比功耗延時。發現當bitwidth取值為5時,設計的各個性能指標達到最優。

通過以上試驗,得出下列結論: 對門控時鐘而言,若不考慮設計的平衡性,插入的門控單元越少且被門控的寄存器越多, 門控的效果就越好,反之亦然。

經編譯,查看時序功耗報告,在滿足電路性能指標情況下, RTL級代碼經綜合生成層次化門級網表和門級時序約束文件。

為查看門控單元在不同設置下的插入情況,用report_clock_gating– multi_stage得到表1所示報告。

從中可知,有23. 68 %的寄存器沒有被門控,原因在于位寬, 使能等不滿足門控要求,對設計無影響。

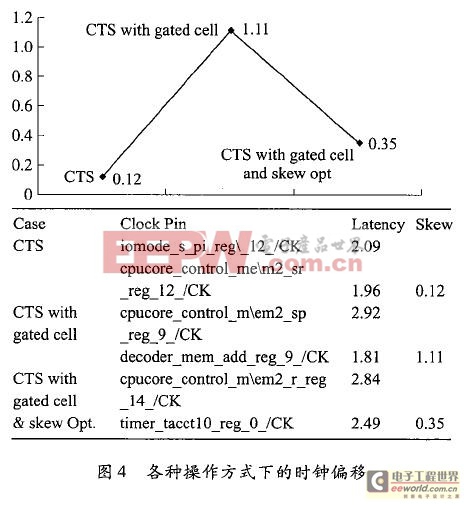

在布局布線階段,基于門控時鐘的功耗優化流程主要如下:在布局之前,設置set_Power_op tiONs–clock_gating true,之后在布局、時鐘樹綜合和布線階段的主要命令中添加選項- power即可。上述設置可實現最基本的門控時鐘布局布線,但在本設計中生成的時鐘網絡分布不均勻,而且skew很大。需要采取額外的優化措施來消除其帶來的不利影響。

門控單元的加入給CTS帶來的影響主要有兩個方面,一方面會造成整個時鐘網絡分布不平衡,另一方面導致時鐘偏移增大。單采用上述措施,時鐘偏移最大可達到1. 11,見圖4中的第二項,嚴重偏離了不采用門控時鐘時的偏移量0. 12。在優化時鐘偏移上,目標有三個方面:構造一個相對平衡的時鐘網絡,使得在各個層上,層的各個分支上的單元數目相近;減小時鐘偏移至可承受范圍;盡量保持功耗同只采用門控時鐘而不優化時鐘偏移狀況下的功耗相近或更小。

分析引起skew偏大的原因,通過在ICC中跟蹤路徑,查看時鐘網絡電路圖,發現時鐘層分布極不均勻,分支節點最大相差6 層。在具體時序路徑中,兩條路徑延時過大,插入了許多不必要的buffer,為構造一個平衡的時鐘樹,減小skew并減少對功耗的影響,在CTS階段采取了三個措施。

第一,設置set_clock_tree_op tions– LOGIC_ level_bal2ance為true。CTS的操作模式有三種: 模塊模式,頂層模式,邏輯級平衡模式。默認為模塊模式。

此處選取邏輯級平衡模式可得到最佳的skew,但對功耗有一定影響。第二,復制門控單元。主要是通過修正ICG輸出端的DRC來平衡扇出,并添加緩沖單元來驅動沒有被門控的寄存器使得整個時鐘樹的結構更加平衡。首先設置cts_push _down_ buffer為true。然后split_ clock _ gate – ob2jects { 3 . / Latch} – gate_ sizing– gate_ relocation。

并且在時鐘樹綜合時結合使用- inter_clock_bal2ance選項。最后,為了彌補功耗優化方面的不足,在CTS完畢之后用p synop t– power。不采用門控時鐘、采用門控時鐘但不做skew優化、采用門控時鐘且進行skew優化三種情況下的skew見圖4。由此可見,優化后的skew較原來相比雖有所增大,但要遠小于優化前的設計。

2. 3 功耗測量過程及實驗結果分析

布局布線完成后,導出網表到VCS中進行后仿,并得到分析功耗所需的saif文件。將此saif文件和布局布線后帶有實際延時信息的網表讀入PT中,加以適當的時序約束進行功耗分析

評論