DDS的信號模擬器設計

概述

在雷達的研制和生產過程中,對雷達的性能指標進行調試和檢測是雷達研制和生產過程的一個重要環節。如果對雷達性能的測試都采用外場實物的話,即用真實的目標(如艦艇、坦克)給雷達提供測試信號,不僅要耗費大量的人力和物力而且使研制周期變長。因此,目標模擬器一數字模擬技術與雷達技術相結合發展起來的專門的系統,它為雷達的信號處理系統和顯示終端技術指標的測試以及性能驗證提供必要條件。

1971年,美國學者J.Tierney等人撰寫的“A DigitalFrequency Synthesizer”一文首次提出了以全數字技術、從相位概念出發直接合成所需波形的一種新的頻率合成原理。如今,DDS技術已成為頻率合成技術發展的主流方向,它高度的集成性,對于簡化電子系統的設計方案,降低硬件的復雜程度,提高系統的整機性能意義重大。可以預料將來DDS產品的時鐘頻率將越來越高,雜散會越來越低,價格也將更低,DDS產品將會得到普遍的應用和發展。

1 DDS信號模擬工作分析

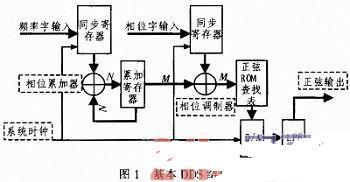

1.1 DDS原理

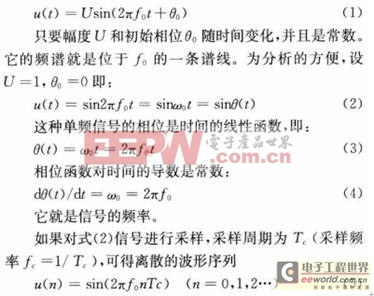

一個頻譜純凈的單頻信號可表示為:

相應的離散相位序列:

是連續兩次采樣之間的相位增量。

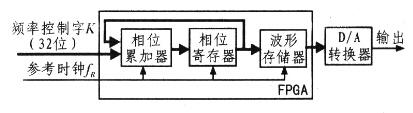

1.2 總體設計方案

DDS信號模擬器系統主要由DDS信號發生器模塊(軟件模塊、控制器、DDS芯片)、濾波放大模塊和調制模塊3部分組成。其系統總體框圖如圖l所示。

1.3 工作流程

首先用戶通過運行于計算機上的控制軟件,選擇要生成的信號,并設置相應的幅度、頻率等指標參數,由控制軟件將這些要求通過RS232接口傳送給CPLD,或利用鍵盤進行頻率選擇。CPLD不僅實現根據接收到的控制字對DDS芯片進行設置,并實時地啟動DDS芯片使其按要求生成所需要的信號。經過濾波放大,將所生成的信號傳送到ASI接口,由此將所生成的基帶信號通過雷達(或其他調制器)調制到高頻,發射出去。

1.4 軟件程序設計方案

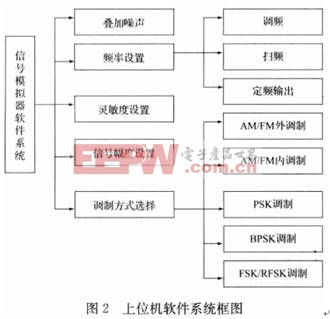

上位機軟件系統結構如圖2所示。

基于DDS的多功能信號模擬器,不僅要能夠實現普通射頻合成信號源的功能,正如能夠在幅度、頻率等方面對所需生成的信號加以控制,能夠實現定頻、掃頻以及跳頻等輸出方式上的選擇。同時,該系統增加了疊加噪聲模塊和靈敏度設置模塊,以便能夠更好地實現對各種條件下雷達回波信號的模擬。

1.5 DDS射頻信號產生電路

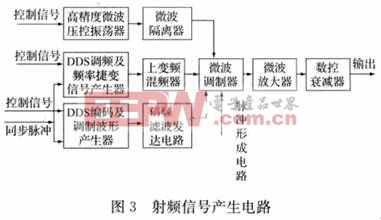

DDS的微波電路構成射頻信號產生電路,其組成框圖如圖3所示,其信號來源分為3路:

第1路是由高精度微波壓控振蕩器產生頻率穩定度很高的微波信號,頻率精度:±2.5×10-6,經微波隔離器隔離輸出。

第2路是由DDS調頻及頻率捷變信號產生器產生各種調頻(普通調頻、線性調頻和非線性調頻等)和頻率捷變信號,DDS工作模式為單音頻工作模式時,通過改寫頻率控制字可實現跳頻和頻率捷變和頻率調制,工作模式為線性調頻模式時,通過設定起始頻率、頻率部進和掃描時間,可實現線性調頻。

第3路是由DDS編碼及調制波形產生器產生各種編碼和調制信號,DDS的一個顯著的特點就是在數字處理器的控制下能夠精確而快速地處理頻率和相位。DDS允許用戶對通過改寫相位偏移控制字可實現相位的任意控制,碼元的產生完全由軟件靈活控制,可產生包括二相編碼(巴克碼、偽隨機碼)、多相制編碼等,并經倍頻、濾波和放大后形成調制包絡信號。

最后來自第l路微波信號和第2路的變頻信號在微波上變頻器混頻,產生載頻信號,來自第3路的調制包絡信號和脈沖產生器產生的調制脈沖對載頻信號進行調制,形成雷達信號,最后經天線輸出。圖4、圖5為最后輸出的波形。

1.6 DDS硬件設計

1.6.1 硬件電路的組成

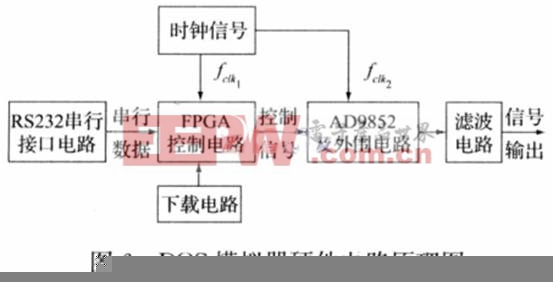

圖6為DDS模擬器硬件電路的組成原理。該信號模擬器主要由6個部分組成:電源電路、串行接口電路、下載電路、FPGA控制電路、AD9852外圍電路以及濾波電路。

1.6.2 AD9852外圍電路

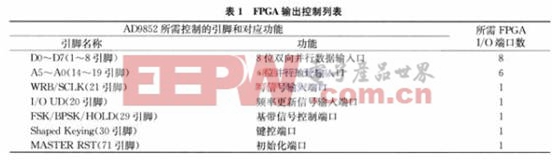

如表1所示,在并行工作模式下,FPGA主要實現對AD9852以下各引腳的控制。

AD9852內部包括1個具有48位相位累加器、1個可編程時鐘倍頻器、1個反sinc濾波器、2個12位300 MHzDAC、1個高速模擬比較器以及接口邏輯電路。其主要性能特點如下:

(1)高達300 MHz的系統時鐘;

(2)能輸出一般調制信號,FSK、BPSK、PSK、CHIRP、AM等;

(3)100 MHz時具有80 dB的信噪比;

(4)內部有4*到20*的可編程時鐘倍頻器;

(5)2個48位頻率控制字寄存器,能夠實現很高的頻率分辨率。

(6)2個14位相位偏置寄存器,提供初始相位設置。

(7)帶有100 MHz的8位并行數據傳輸口或10 MHz的串行數據傳輸口。

圖7為在DDS的信號發生器中AD9852的外圍電路設計。

2 測試結果

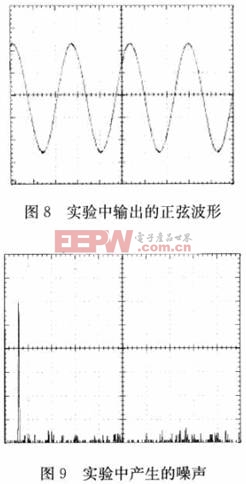

本文設計的DDS信號模擬器輸出最大頻率受到D/A轉換器輸出建立時間的限制,因為外接存儲器的數據讀取時間為15 ns,可編程邏輯器件FPGA的最大時鐘頻率可達120 MHz。相位累加器的字長為31位,用于尋址波形數據存儲器的地址信號為13位;編程產生的正弦波的輸出的頻率范圍是0~120 MHz。其中產生的正弦波如圖8所示,但是隨著時間的增長,噪聲會加大如圖9所示。

3 結束語

本文結合DDS信號模擬器的工作原理從理論和實際2個方面,對直接數字頻率合成技術(DDS)進行了研究。

首先通過對DDS信號模擬工作理論分析,再通過對DDS射頻信號產生電路的研究實驗使得微波信號和變頻信號在微波變頻器上混頻,產生載頻信號,再者使得調制包絡信號和調制脈沖對載頻信號進行調制,形成雷達信號,然后經天線輸出。最后結合理論分析的結論,通過測試實驗得出了系統的性能以及帶寬線性調頻和帶寬10點跳頻的過程最終輸出了雷達視頻

模擬信號相關文章:什么是模擬信號

隔離器相關文章:隔離器原理

評論