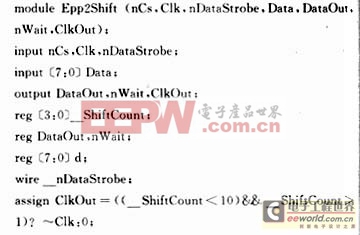

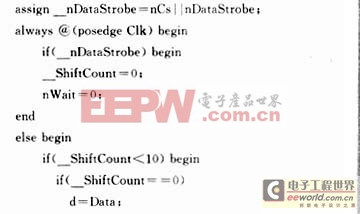

ize-adjust: auto; -webkit-text-stroke-width: 0px"> 硬件電路使用Altera公司的復雜可編程邏輯器件(CPLD)來實現。其結構用Verilog HDL語言描述。其中,nCs為片選信號,由地址譯碼產生(地址輸出及譯碼的描述省略),Clk為外部時鐘源,DataOut和ClkOut分別為輸出數據和輸出同步脈沖。為防止系統超時,Clk應有較高的頻率,大約為10 MHz左右。接口的Verilog HDL描述如下:4 結束語

用EPP并行口擴展移位寄存器輸出接口,充分利用了EPP的握手信號,因而在軟件設計時不需要對移位寄存器的狀態進行查詢,只需對基地址+4端口進行寫操作,即可完成一個字節的移位寄存器輸出,簡化了軟件編程,實現了高的傳送速率(傳送速率可達8Mbit/s)。以此為例還可擴展出多路開關量通道等接口。

1 Institute of Electrical and Electronics.IEEE Standard Signaling Method for a Bidirectional Parallel Peripheral Interface for PersonalComputers.IEEEStd 1284,2000

2 宋萬杰等.CPLD技術及其應用.西安:西安電子科技大學出版社,1999

3 J.Bhasker.Verilog HDL硬件描述語言.北京:機械工業出版社,2000

模擬電路文章專題:模擬電路基礎

評論