基于GAL的I2C總線時序模擬

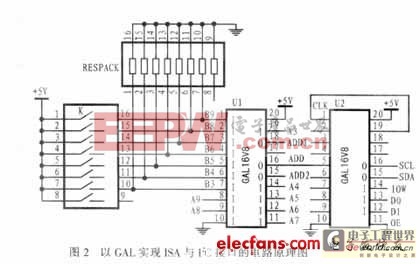

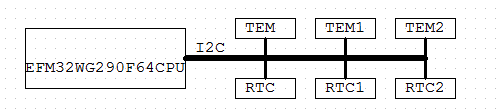

圖2中,撥碼開關K用以設定作為計算機外設的FI1256 MK2的地址,U1用于計算機訪問外設時地址的譯碼,U2則用于實現用ISA總線的兩條數據線模擬I2C總線時序。下面給出兩片GAL的邏輯方程(以FAST-MAP格式書寫),并對照方程簡要說明電路所實現的功能。

通過以上方程可使U1完成地址的譯碼功能。當ISA總線上出現的外設地址與撥碼開關設定的地址相匹配時,在其地址有效輸出端ADDR上將得到高電平。由于GAL最多只能有8個或項,所以方程中使用了ADD1和ADD2兩個中間運算結果,他們被當作反饋信號在GAL內部重新引到輸入端。使用AEN信號是為了在DMA周期內屏蔽總線上出現的地址。

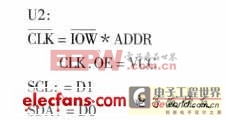

U2的時鐘信號是由地址ADDR和外設寫信號IOW的引入是為了消除總線上出現訪問內存的信號,同時利用其上升沿鎖存數據。SCL和SDA可分別用數據線D0和D1模擬。當一個外設寫周期過后,D0和D1的數據將鎖存在SDA和SCL上,而在下一個對相同外設地址的外設寫周期到來之前是不變的。這就使得I2C總線的時序可以在D0和D1兩根數據線上通過間隔輸出數據的方式獲得。

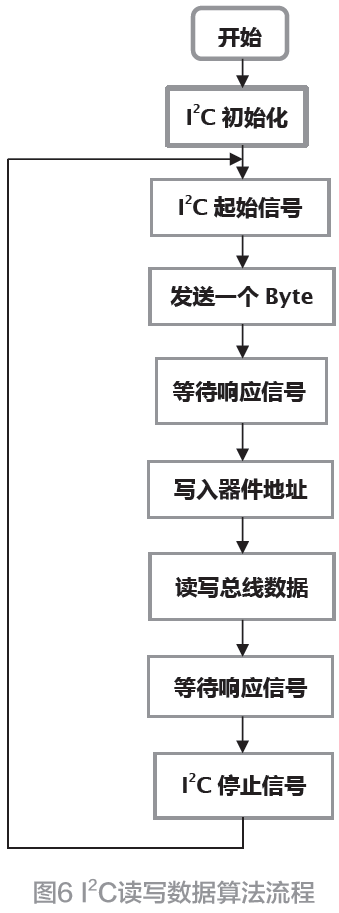

通過分析圖1給出的數據傳輸格式,可以把傳送的數據流劃分為三種傳送狀態,即傳送起始信號、傳送終止信號和傳送一個字節(后面帶一個應答位)。不同的數據過程只是寫入的數據字節數目不同。只要模擬軟件能實現上述三種傳送狀態,就可以模擬出任何的主控器寫操作過程。因此可以用下列子程序分別實現上述三種傳送狀態。

(1)字節傳送子程序

由于SCL和SDA是用D1和D0模擬的,所以,只要往設定的I/O地址傳送相應的數據就可以模擬傳送不同的數據字節。為了保證數據的可靠傳輸,I2C總線規范對總線上的時序作了嚴格的規定。實驗證明,ISA總線上信號的上升沿和下降沿都在10ns以內,完全可以滿足I2C總線對上升沿與下降沿的要求,所以不需考慮信號的上升與下降時間,而只需考慮信號的建立和保持所需的時間即可。

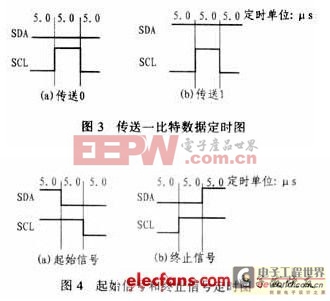

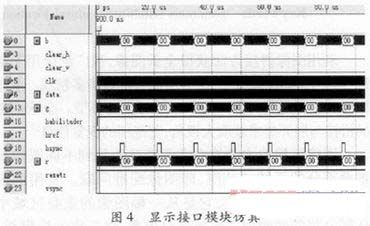

根據對I2C的定時要求,可以在SCL低電平的中點將信號進行分割,并把一個字節數據分為8個比特來分別進行傳送(傳送0和1分別用兩個子程序實現),從而使SDA線上的數據變化總是處在SCL低電平的中點。圖3所示是傳送一比特數據的定時時序圖。

由于在對FI1256 MK2的操作過程對實時性要求不是太高,所以可以使傳送一比特數據的三個狀態都持續5.0μs,這樣,就可以滿足所有的定時要求。把圖3中的兩個定時圖進行組合即可傳送任意的數據字節。在每個數據字節的8比特數據后,都會在SCL上送出一個時鐘周期而讓SDA保持高電平,以使FI1256 MK2送出應答信號。應答信號定時圖與圖3(a)相同。

評論