放大器實用設計案例精華匯總(一)

![]()

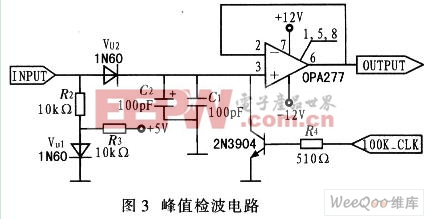

4.2 峰值檢波電路

峰值檢波電路由二極管電路和電壓跟隨器組成。其工作原理:當輸入電壓正半周通過時,檢波管 VU2導通,對電容C1、C2充電,直到到達峰值。三極管的基極由FPGA控制,產生1Oμs的高電平使電容放電,以減少前一頻率測量對后一頻率測量的影響,提高幅值測量精度。其中Vu1為常導通,以補償VU2上造成的壓降。適當選擇電容值,使得電容放電速度大于充電速度,這樣電容兩端的電壓可保持在最大電壓處,從而實現峰值檢波。

該電路能夠檢測寬范圍信號頻率,較低的被測信號頻率,檢波紋波較大,但通過增加小電容和大電容并聯構成的電容池可濾除紋波。而后級隔離,則增加由OPA277構成的射極跟隨器,如圖3所示。

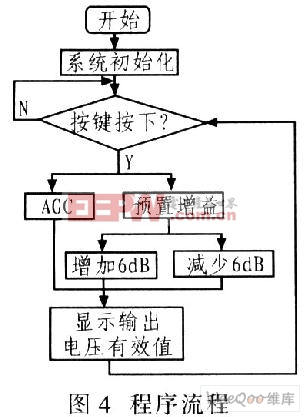

5 系統軟件設計

5.1 程序部分設計

系統軟件設計遵循結構化和層次化原則,由一個主程序及若干子程序構成。主程序通過調用子程序控制子程序間的時序,從而使整個程序正常運行。系統軟件設計部分由單片機和FPGA組成。單片機主要完成讀取鍵值、控制增益和顯示功能。而FPGA則作為總線控制器,管理鍵盤、液晶和A/D轉換器與單片機之間的數據交換。以Ouartus II 7.2為設計環境,用Verilog HDL硬件描述語言編程,完成各功能模塊的設計,并仿真測試設計好的各個模塊,再將各個模塊相互連接。程序以按鍵中斷為主線,以各項功能為分支,圖4為程序流程。

5.2 FPGA部分設計

FPGA主要完成A/D、D/A轉換器的串并轉換。采用12位D/A轉換器TLV5618,該器件是串行接口,大大節約系統端口資源,但MCU的P0、 P2端口是并行口,與串行器件的時序匹配較復雜,用靜態口P1端口模擬串行口時序又會占用MCU很多處理時間,影響系統效率。

為使MCU對串行器件操作簡單,把串行時序在FPGA中用狀態機描述,同時該控制狀態機又對MCU提供P0口、CS、WR的微機標準時序接口形式,這樣MCU只需選中相應地址,就可寫入所要得到的電壓數據,狀態機會完成串并轉換。

以串行接口時序將數據寫入器件并鎖存,與寫IO端口操

電子管相關文章:電子管原理

評論