單電源供電的全差分斬波運放電路

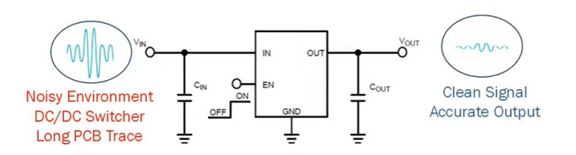

主運放采用全差分折疊式cascode結(jié)構(gòu),在Class-D的結(jié)構(gòu)中,由于輸出功率MOSFET大電流的頻繁開啟,產(chǎn)生的電磁干擾(EMI)會在電源上形成很強的紋波,在實際應(yīng)用中發(fā)現(xiàn)當芯片工作在5V的電源電壓下,EMI引起的電源波動能達到±2V,全差分結(jié)構(gòu)既可以提高運放的電源抑制比和共模抑制比,減弱電源噪聲和共模噪聲的影響,而且避免了鏡像極點,因而對于更大的帶寬仍能表現(xiàn)出穩(wěn)定的特性。

為了提供更高的增益和電壓輸出擺幅,在fold-cascode后加入共源運放輸出級。采用二級運放后.對運放的頻率穩(wěn)定性進行分析。暫時不考慮斬波開關(guān)的影響,可以推斷該電路至少有三個LHP極點,它們分別是miller補償電容引入的主極點Wp1,輸出濾波電容產(chǎn)生的輸出極點Wpout。為第一非主極點,以及folded-cascode(MN1的漏端、MN3的源端)引入的非極點Wp3,三者之間的關(guān)系為Wp1

共模反饋電路由MN7~MN10、MP10-MP12構(gòu)成,輸入一端接VDD/2的基準電壓,另一端接主運放的共模輸出,共模檢測電路由電阻和電容構(gòu)成.經(jīng)過誤差放大后調(diào)控主運放的偏置電流。

4 仿真結(jié)果及版圖設(shè)計

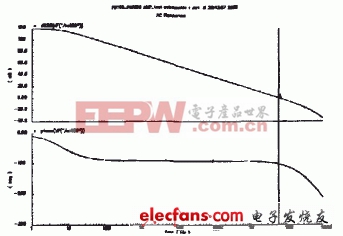

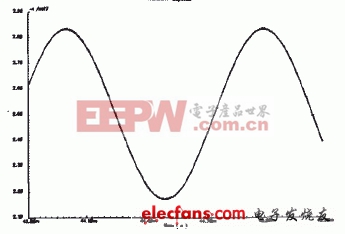

在SMIC O.35微米N阱工藝下.利用cadence spectre工具對本文所設(shè)計的電路進行了仿真分析。其中,各器件的工藝參數(shù)為典型情況,電源電壓5V,輸入信號為幅度10uV,頻率為1KHz的標準正弦波,斬波頻率fch=150K,仿真波形如圖5和圖6所示。

圖5 運放的幅頻~相頻特性曲線

圖6 斬波輸出波形

從圖5可以看出,在典型情況下,該運放的主極點在10HZ以內(nèi),相位裕度75度左右.能充分保證運放在各個comer條件下的穩(wěn)定性。從輸fn波形來看,斬波引起的殘余電壓尖峰也有了明顯的改善。表1為運放的開環(huán)仿真結(jié)果。

表1 運放開環(huán)仿真結(jié)果

評論