襯底驅動軌至軌運算放大器設計

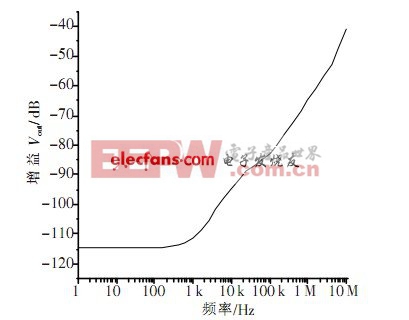

圖4 運算放大器的幅頻特性曲線

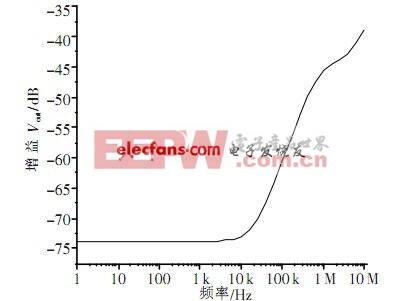

在運算放大器的兩個輸入端加相同的信號,做交流小信號分析,測出電路的共模電壓增益如圖5所示。在低頻下,電路的共模增益為-114 dB,結合前面交流小信號分析的結果,可得出電路的共模抑制比為176.1 dB。圖6為電壓抑制比仿真曲線,低頻時,電壓抑制比約為-73.8 dB。

圖5 共模電壓增益

圖6 電壓抑制比仿真曲線

綜上仿真結果表明,該襯底驅動運算放大器具有良好的性能。雖然運算放大器的頻率帶寬和線性度有所下降,但是卻能有效避開閾值電壓的限制,將電源電壓降低到0.8 V,功耗為65.9 μW,同時實現了軌至軌的輸入/輸出電壓范圍。在傳統的柵驅動軌至軌運算放大器信號通路中存在MOS管閾值電壓的影響,因此限制了其在超低電源電壓下的應用。

總結:本文通過采用襯底驅動互補差分對電路,有效降低了CMOS模擬集成電路對電源電壓的要求,通過改進型前饋式AB類輸出級來提高電壓的增益,實現了超低壓下運算放大器信號放大,獲得了-0.36 V~0.39 V的共模輸入范圍和-0.39 V~0.395 V的輸出電壓范圍。仿真得到該運算放大器具有良好的性能指標,能夠有效地驅動阻性負載,且結構簡單,適于低壓低功耗模擬集成電路應用。

評論