窄脈沖小信號(hào)運(yùn)算放大電路方案

1 設(shè)計(jì)目的

根據(jù)項(xiàng)目需要,本次設(shè)計(jì)的差分運(yùn)算放大器是用于放大檢波器輸出的信號(hào)的,由于接收機(jī)接受的信號(hào)是小信號(hào)脈沖調(diào)制,因此設(shè)計(jì)的運(yùn)放必要能夠放大小信號(hào)窄脈沖。因?yàn)樵谛⌒盘?hào)情況下,檢波器輸出為毫伏級(jí)別,而指標(biāo)要求輸出在-2~+2V之間,所以設(shè)計(jì)的差分放大電路放大倍數(shù)約100倍。

2 設(shè)計(jì)思路

由于此次設(shè)計(jì)的運(yùn)放是為了放大脈沖信號(hào)的,所以必須要考慮脈沖信號(hào)上升沿的問(wèn)題,如果上升沿時(shí)間太大會(huì)導(dǎo)致脈沖信號(hào)的失真,因此設(shè)計(jì)的最初就是要限定脈沖信號(hào)上升沿時(shí)間T50ns.由于脈沖信號(hào)的帶寬和上升沿存在如下關(guān)系:F×T=3.5(F表示帶寬),可知上升沿時(shí)間越小,帶寬就越大,當(dāng)上升沿時(shí)間T=50ns時(shí)。帶寬就要達(dá)到70MHz.因?yàn)檫\(yùn)放的帶寬和增益成反比,如果只使用一級(jí)運(yùn)放,在達(dá)到要求帶寬的同時(shí)增益就達(dá)不到要求的100,因此本次設(shè)計(jì)的運(yùn)放采用兩級(jí)放大結(jié)構(gòu),每級(jí)放大10倍。

3 相關(guān)電路

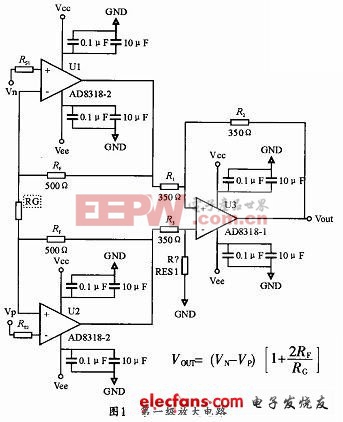

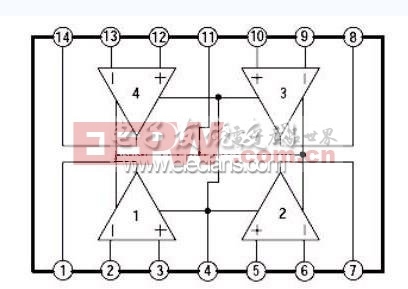

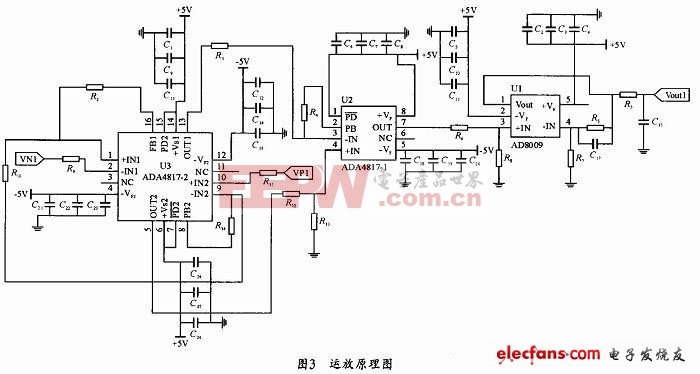

從以上分析可知本次運(yùn)放電路采用兩級(jí)結(jié)構(gòu)。第一級(jí)首先對(duì)基帶信號(hào)進(jìn)行差分放大,芯片選擇AD公司的ADA4817-1和ADA4817-2,第一級(jí)放大電路如圖1所示。

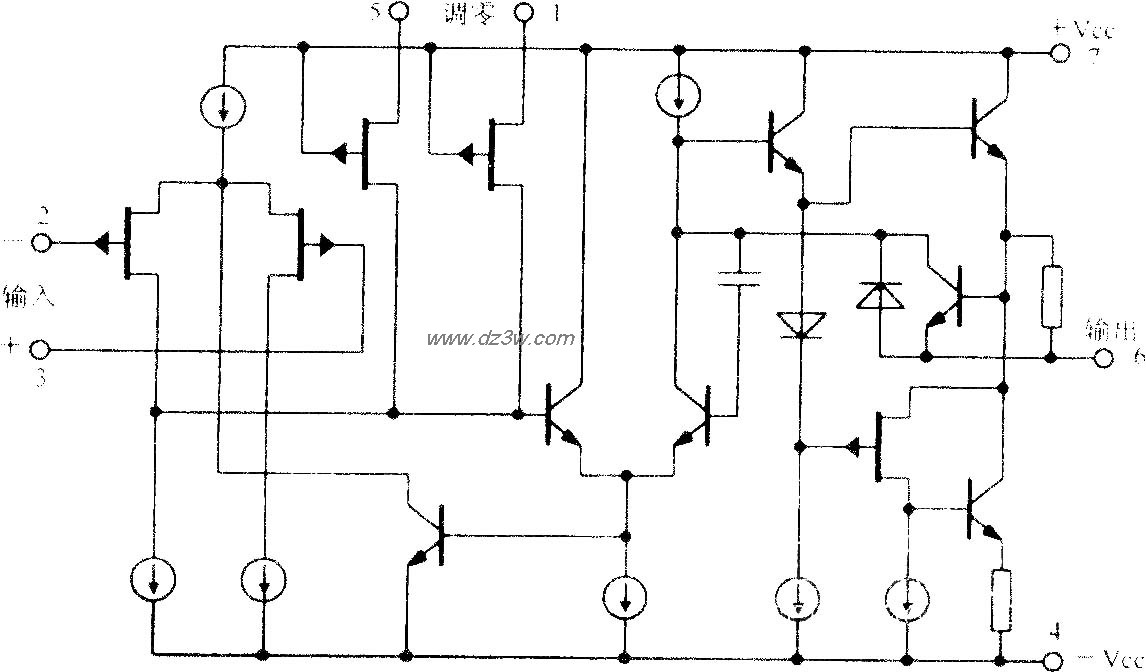

第一級(jí)放大所用的芯片ADA4817-1(單通道)和ADA4817-2 (雙通道)FaSTFET放大器是單位增益穩(wěn)定、超高速電壓反饋型放大器,具有FET輸入。這些放大器采用ADI公司專(zhuān)有的超高速互補(bǔ)雙極型(XFCB)工藝,這一工藝可使放大器實(shí)現(xiàn)高速和超低的噪聲(4nV/√Hz;2.5 fA/√Hz)以及極高的輸入阻抗。

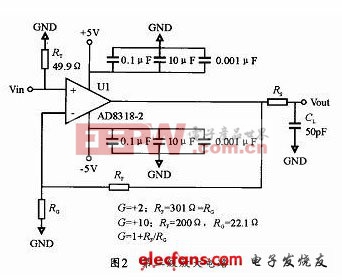

將第一級(jí)輸出的信號(hào)進(jìn)行二次放大,第二級(jí)放大選擇AD公司的AD8009芯片。圖2所示是第二級(jí)放大電路。

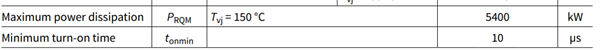

第二級(jí)放大所用的芯片AD8009是一款超高速電流反饋型放大器,壓擺率達(dá)到驚人的5 500 V/μs,上升時(shí)間僅為545ps,因而非常適合用作脈沖放大器。

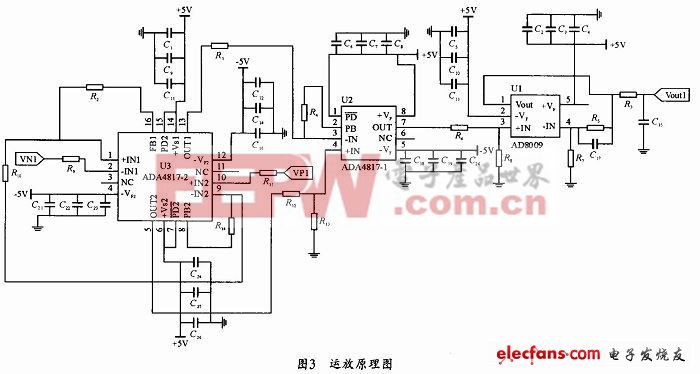

此外為了防止自激,在兩級(jí)放大的中間連接了一個(gè)10Ω電阻。圖3是差分運(yùn)放的整體原理圖。

圖4是示波器上顯示的是差分輸入端得兩個(gè)信號(hào),從圖上可以看出,兩個(gè)信號(hào)的差是2.32mV。

圖5是運(yùn)放的輸出信號(hào),從圖中可以看出輸出信號(hào)為220mV,相比輸入信號(hào)的2.32mV,實(shí)現(xiàn)了接近100倍的放大。而且可以從圖中看出,上升沿為50ns,也是滿足設(shè)計(jì)目標(biāo)的。

圖6是運(yùn)放的實(shí)物圖,實(shí)物圖中包含了兩組運(yùn)放還有12V轉(zhuǎn)成+5V和-5V的電源轉(zhuǎn)換模塊。

5 結(jié)束語(yǔ)

綜上所述,說(shuō)明該運(yùn)放幾乎無(wú)失真的將檢波器輸出的毫伏級(jí)窄脈沖小信號(hào)放大了接近100倍。這證明本次設(shè)計(jì)的差分運(yùn)放是能夠滿足要求的并且性能良好。

模擬信號(hào)相關(guān)文章:什么是模擬信號(hào)

電路相關(guān)文章:電路分析基礎(chǔ)

模數(shù)轉(zhuǎn)換器相關(guān)文章:模數(shù)轉(zhuǎn)換器工作原理

脈沖點(diǎn)火器相關(guān)文章:脈沖點(diǎn)火器原理

評(píng)論