先進3D芯片堆疊的精細節距微凸點互連

除了Cu/Sn微凸點(μbump)互連外,實現芯片與芯片互連的另一替代方法是基于銦(In)的精細節距焊料凸點。銦是非常軟的材料,熔點低(156℃),但成本高,一般局限于高端成像傳感器一類的特殊應用。

實驗

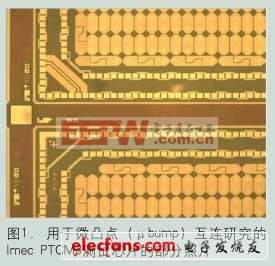

本文全部實驗均用5×5mm2 Imec封裝測試芯片進行。圖1是晶圓上一些關鍵測試圖形的照片。這些芯片由氧化物介質中的標準單大馬士革Cu互連層組成、用氧化物/氮化物層鈍化。用于微凸點互連的測試結構主要是菊花鏈觸點的周邊行。在一種測試芯片中,它們連接總計480個直徑25μm的微凸點連接點,節距為40μm。另一種測試芯片含有8200個直徑25μm的微凸點陣列,節距為50μm。微凸點形成工藝是用半加成電鍍技術。首先依次淀積Ti/Cu籽晶層和光刻膠層。然后進行光刻確定用于微凸點的開口區域。將光刻膠顯影后,再依次電鍍Cu和Sn,形成微凸點。最后,剝離光刻膠層,將Ti/Cu籽晶層刻蝕掉。

圖1所示測試芯片采用60μm周邊焊盤節距,并與TSV結合使用。實現這些TSV所用的工藝有詳細描述。加工TSV前,把晶圓厚度減至50μm。TSV直徑是25μm,深度為50μm。TSV Cu填充和微凸點形成在單一工藝中結合完成。Ti/Cu籽晶層在TSV刻蝕后淀積于深寬比為2的50μm TSV上。Cu填充前,應用10μm厚負光刻膠掩膜層,它允許同時形成Cu填充TSV和Cu/Sn凸點。用Cu填充TSV后,直接鍍一層3.5μm厚Sn層。光刻膠剝離后,用化學方法除去金屬籽晶層。

測試樣品的鍵合在SET FC-150倒裝芯片鍵合機上溫度為150-250℃時進行。鍵合前應用不同的清洗劑(如助溶劑)。鍵合期間加壓(5MPa-150MPa),鍵合時間3-20分鐘。

鍵合后,測量交織的菊花鏈的電阻和絕緣以檢查互連的電氣性能。有些樣品還送去做X截面SEM檢驗。

結果

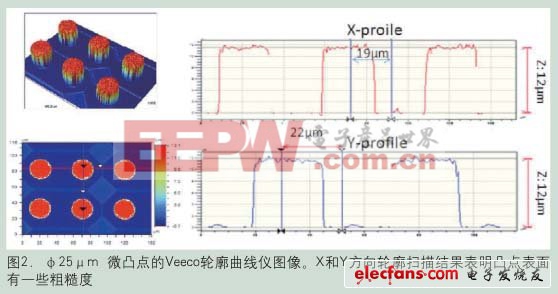

微凸點由焊料凸點和上芯片上的UBM組成。可焊金屬“凸點焊盤”(此例中為Cu)置于下面的襯底上。焊料微凸點的使用也是選項,但本實驗未使用。焊料與UBM/可焊金屬的反應結果形成金屬間化合物,因此上下芯片就連接。本研究中,UBM是Cu或Cu/Ni雙金屬層,而焊料凸點或包含純Sn,或包含SnAg。圖2是φ25μm微凸點的光學干涉測量剖面,在Cu/Ni UBM上形成了SnAg焊料凸點。

由于Sn和Cu的吉布斯(Gibbs)自由能低,二者均易被氧化。實際上發現,去除氧化物對確保SSD鍵合的金屬間化合物形成至關重要。一些商用清洗劑(如助溶劑)和稀有機酸在倒裝芯片鍵合過程中清洗Cu和Sn。助溶作用也可以用所謂非流動底層填充料(NUF)提供。優點是可與封裝裝配工藝同時進行底層填充工藝。但它們均不能在很低溫度下有效去除氧化物。這使我們的SSD鍵合溫度不能低于150℃。實際上,不同清洗劑的結合給出了150℃時的最佳鍵合結果。去除氧化物對于TLP鍵合的重要性不大,此時液態Sn能潤濕Cu UBM形成金屬間化物。

與SSD鍵合不同,應用于TLP鍵合的壓力要小得多,2.5-10MPa對電良率不產生什么差異。

考慮工藝簡易和連接界面質量之間的最佳折中,以NUF鍵合為基礎工藝。這消除了毛細管底層填充的需求。進而通過采用初始高度并行的芯片至晶圓的取放、隨后集中鍵合芯片的方法增加工藝產出。該方法已被證明能用于全200mm晶圓級(圖3)。對于TLP和固態擴散鍵合方法,40/15μm節距/間距周邊陣列芯片,獲得了90%以上的器件良率。

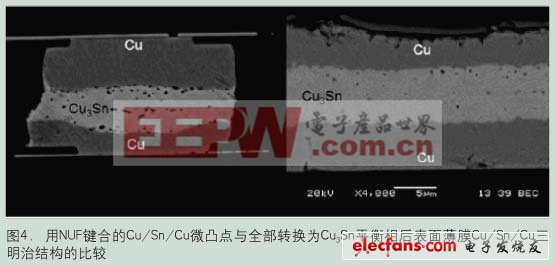

對TLP和SSD鍵合時空洞的形成也作了研究。除了由于夾帶清洗劑殘留物形成空洞外,還在Cu3Sn相中觀察到名為柯肯達爾(Kirkendall)空洞的較小亞微米空洞,Cu3Sn相在Cu-Sn鍵合后形成。為了研究制備方法對空洞形成的影響,對不同Cu/Sn/Cu三明治結構做了老化實驗。發現空洞最初位于Cu和Sn界面處,但隨老化的進展,更多空洞逐步漂離這一表面。在金屬間化物連接中心也能觀察到大量空洞。Cu/Sn/Cu表面薄膜中也發現柯肯達爾(Kirkendall)空洞,這里三明治薄膜是順次電淀積形成。不過,將微凸點樣品與表面薄膜堆疊(此堆疊持續老化到全都轉換成Cu3Sn相為止)比較時,觀察到在Cu-金屬間化物界面處和在連接中心內的空洞形成密度的不同(圖4)。因為Cu/Sn/Cu表面薄膜是用同一電鍍化學過程淀積的,不過沒有附加還原劑,這些還原劑污染物會增加空洞成核和生長。

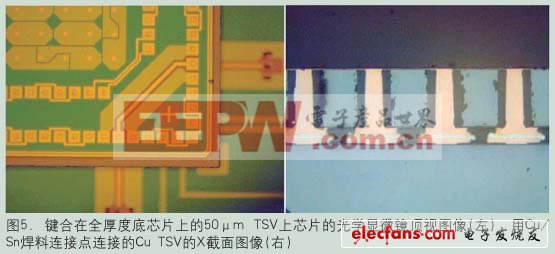

最后,我們說明基于CuSn金屬間化物微凸點在用后通孔方法形成的堆疊芯片中的應用。節距為60μm周邊陣列TSV的3D晶圓級封裝(3D-WLP)TSV器件堆疊在匹配的Si襯底上(圖5)。這些器件有菊花鏈連接,以監控TSV+微凸點連接的電學連續性。觀察到Cu-Sn堆疊工藝具有高良率。

結論

用精細節距Cu/Sn微凸點實現薄芯片堆疊。瞬時液相鍵合和固態擴散鍵合二者均有高電學良率。

評論