TMS320C61416控制FPGA數據加載設計(二)

本系統中2片FPGA加載的原理一樣。為避免繁瑣,這里以1片FPGA_A為例來作介紹。

CPLD在系統中負責2項工作。

①映射DSP端Flash分頁寄存器:控制Flash的高3位地址線,分8頁,每頁1 MB空間。

②映射DSP端2片FPGA的加載寄存器:

a.配置寄存器FpgaA(B)_config_Reg[8:O]。負責配置數據和時鐘,高8位為Byte-Swapped前的數據位,輸出到配

置引腳時進行字節交換,最低位為CCLK位。

b.控制寄存器FpgaA(B)_Prog_Reg[2:O]。負責外部控制引腳,分別為CS_B、RDWR_B和PROG_B。

c.狀態寄存器FpgaA(B)_State_Reg[2:0]。負責回讀配置中的握手信號,分別為BUSY、DONE和INIT_B。

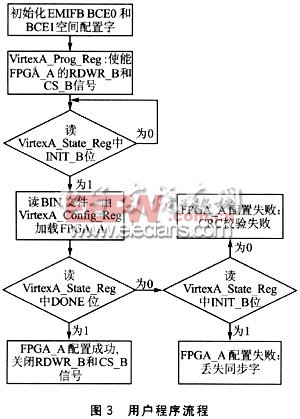

由Bootloader引導的用戶程序由C語言開發,在CCS下調試通過。它主要實現Flash翻頁,把之前燒寫在Flash中的BIN文件,通過上述CPLD中3個加載寄存器對FPGA進行上電配置。具體流程如圖3所示。

當前FPGA配置時鐘CCLK是在用戶程序中通過DSP寫命令產生的,即寫FpgaA(B)_Config_Reg的CCLK位高低電平;同時8位配置數據也連續寫2次,由CPLD鎖存到FPGA總線上,便能充分保證圖1中該有效數據在CCLK上升沿上被鎖。

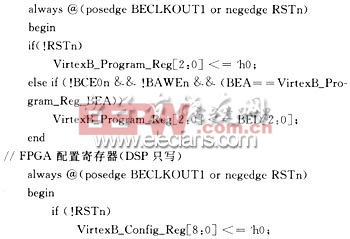

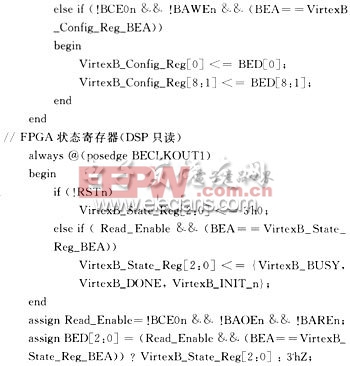

以下是CPLD中動態加載部分的Verilog代碼:

//FPGA控制寄存器(DSP只寫)

結 語

該系統已成功用于某公司一款軟件無線電平臺中,通過反復軟硬件調試,現已投放市場。此平臺不僅可以實現上述提到的上電Flash自行加載FPGA的目的,還可在其配置完以后通過主機端對FPGA實現動態加載,充分滿足了軟件無線電中可重構化、實時靈活的指導思想。

評論