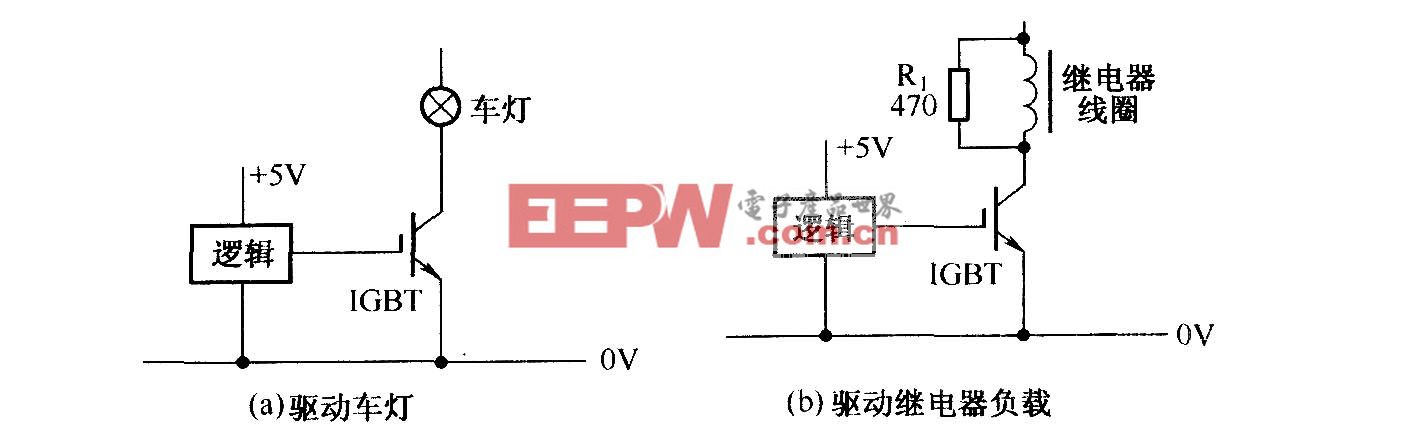

style="PADDING-RIGHT: 0px; PADDING-LEFT: 0px; PADDING-BOTTOM: 0px; MARGIN: 0px 0px 20px; WORD-SPACING: 0px; FONT: 14px/24px 宋體, arial; TEXT-TRANSFORM: none; COLOR: rgb(0,0,0); TEXT-INDENT: 2em; PADDING-TOP: 0px; WHITE-SPACE: normal; LETTER-SPACING: normal; BACKGROUND-COLOR: rgb(255,255,255); webkit-text-size-adjust: auto; orphans: 2; widows: 2; webkit-text-stroke-width: 0px"> 限時保護繼電器在關斷時產生的干擾電壓峰值較高, 因此, 在輸出電路中增加吸收電路對功率場效應管Q1 進行保護, 本電路中采用VRC 吸收電路。其中, V12 為快恢復二極, 管R15 為功率電阻, C6 為高頻無感電容。Q1 導通時, V12 反偏,C6 通過R15 放電, R 消耗能量并限制放電電流;Q1 關斷時, C6 通過V12 吸收干擾電壓, 使Q1 的尖峰電壓不會過高。 Q1 在關斷時產生的干擾電壓較高, 可由下式進行計算:

式中, Vcep為集-射極間的尖峰電壓, 單位為V; Vcc為負載電源電壓, 單位為V; L 為主電路和引線電路電感之和, 單位為H; di/dt 為MOSFET集電極電流變化速率, 單位為A/s.

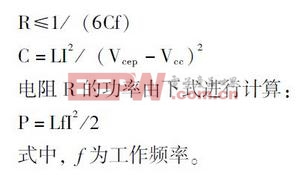

由此可見, 在大電流、關斷速度很快時, 尖峰更大。因此, 在輸出電路中增加吸收電路對MOSFET進行保護。VRC 吸收電路中R、C 由下式進行計算:

4 結束語

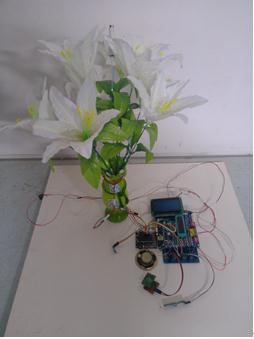

本文介紹了固體式限時保護繼電器的電路設計, 并詳細介紹了輸入電路設計、延時濾波電路設計、限時保護電路設計、隔離電路設計、驅動電路設計、串聯輸出電路設計, 并經過技術攻關, 研制出JGD24 -5 型固體式限時保護繼電器。經試驗驗證, 其各項技術指標均達到了該方案的設計要求。

繼電器相關文章:繼電器工作原理

時間繼電器相關文章:時間繼電器

評論