雙相位鎖定回路助力數位中頻系統擺脫時鐘抖動

相位雜訊產生原因分析

根據上述分析,時鐘抖動對于系統中的ADC和相位鎖定回路都有非常明顯的影響,那么如何才能在數位中頻系統中獲取更好的時鐘相位雜訊呢?首先,要理解在數位中頻系統中核心元件,例如相位鎖定迴路的基本工作原理。相位鎖定回路其實是一個數位類比混合元件,包括數位的相位偵測器和分頻器以及類比的電流泵、低通濾波器和壓控振蕩器(VCO)。相位鎖定回路是一個負反饋系統,它通過頻率訊號的負反饋和相位偵測比較,使得VCO在穩定的控制電壓下工作,從而達到穩定輸出頻率的作用。

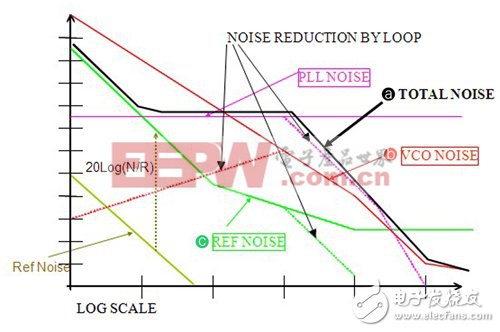

圖4是頻譜儀觀測結果,a線為相位鎖定回路輸出的相位雜訊相對頻率水準、b線為VCO的相位雜訊水準被相位鎖定回路的高通濾波回應抑制低頻部分;c線則是外部參考輸入相位雜訊的倍頻增益產物,它的高頻雜訊被相位鎖定回路的低通回應所抑制,但是低頻(也稱之近端)相位雜訊被保留。恰恰是這個特性導致若相位鎖定迴路的輸入參考的相位雜訊不好或者低通濾波器的截止頻率不夠低,就會讓參考時鐘相位雜訊被搬移到相位鎖定回路的輸出端。

圖4 Inter-N形式PLL合成器相位雜訊(a線表示PLL輸出的相位雜訊相對頻率水準,b線表示VCO相位雜訊水準,c線是外部參考輸入相位雜訊的倍頻增益產物)

使用低環路濾波器去抖動

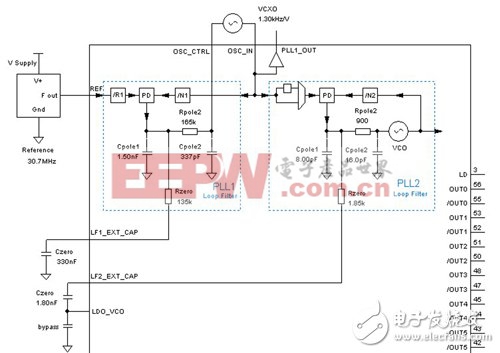

根據上述分析,系統為提高時鐘近端相位雜訊水準,就須要提高參考時鐘的相位雜訊水準或者降低相位鎖定迴路低通濾波器的頻率。而在光纖接入數位中頻系統中,參考時鐘是從光口恢復的,它本身就存在近端相位雜訊(抖動)惡化的問題。如何解決這個矛盾呢?只能從降低低通濾波器頻率下手。如圖5所示,AD9523在設計中使用了兩個相位鎖定回路,第一個相位鎖定回路接外部的參考時鐘(光口恢復的),采取非常低的低通濾波器設置(10Hz~100Hz)。它可以將參考時鐘近端相位雜訊良好濾除,而相位鎖定回路外接的壓控晶體振蕩器(VCXO)可以提供很好的近端相位雜訊,這樣保證不會因為低通濾波器頻率低而將VXCO的近端雜訊抬高(註:這裡對于VXCO來說低通濾波器變為高通濾波回應)。這樣第一個相位鎖定回路就可以將參考時鐘近端相位雜訊很好的抑制。而第二個相位鎖定回路采用高頻率VCO(3,600MHz?4,000MHz)和70MHz的相位偵測頻率。這樣可以降低雜訊頻率增益的同時,獲取更多的頻率組合(系統中有時需要不同頻率的工作時鐘,VCO須要工作在它們的最小公倍數的整數倍)。

圖5 雙相位鎖定回路可濾除相位雜訊并獲得良好頻率組合。

評論