基于TLK10002的 SERDES FIFO 溢出解決方案

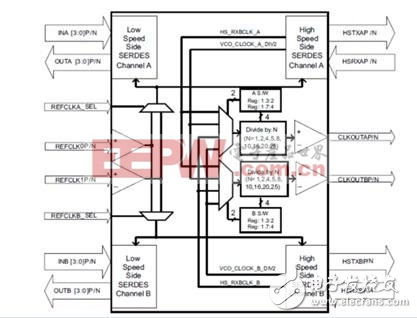

對于每個通道而言,高速側(cè) SERDES 和低速側(cè) SERDES 可以工作在一個時鐘域,即兩者使用同一參考時鐘;同時,TLK10002 也提供了另外一種時鐘模式,即高速側(cè) SERDES 和低速側(cè)SERDES 使用不同的參考時鐘,這種情況下,高速側(cè)鎖相環(huán)和低速側(cè)鎖相環(huán)會工作在不同的時鐘域。

圖 2 TLK10002 內(nèi)部時鐘架構(gòu)

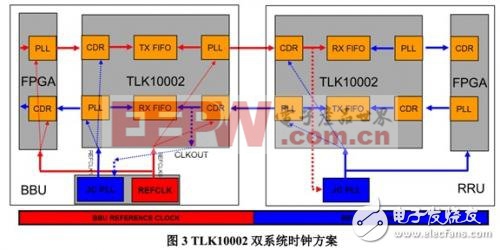

2.2 TLK10002 雙時鐘系統(tǒng)方案

基于雙時鐘 TLK10002 構(gòu)建的系統(tǒng)級聯(lián)方案如圖 3 所示。在這種方案中,TLK10002 高速側(cè)SERDES 和低速側(cè) SERDES 采用不同的參考時鐘。

在 BBU 一側(cè),高速側(cè)鎖相環(huán)采用本地的參考時鐘,一旦高速側(cè)鎖相環(huán)鎖定,并且 BBU 和 RRU 之間建立穩(wěn)定的鏈路,BBU 一側(cè) TLK10002 的 CDR 會有穩(wěn)定輸出,這個輸出給 BBU 上的 Jitter Cleaner 提供參考輸入。 一旦 Jitter Cleaner 正常鎖定,它的輸出又會作為低速側(cè)鎖相環(huán)的參考輸入。

采用這種配置,由于 SERDES 本身可以處理最高 200ppm 的頻率偏移,發(fā)射和接收通道的速率是完全相互獨立的。這樣,FIFO 的兩側(cè)完全工作在同一時鐘域,FIFO 就不會存在溢出的風(fēng)險。在這種情況下,FIFO 僅僅用來吸收不同時鐘之間的相位偏移和補償 jitter cleaner 的跟蹤能力。

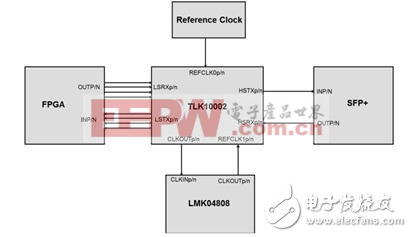

2.3 雙系統(tǒng)時鐘方案的具體實現(xiàn)

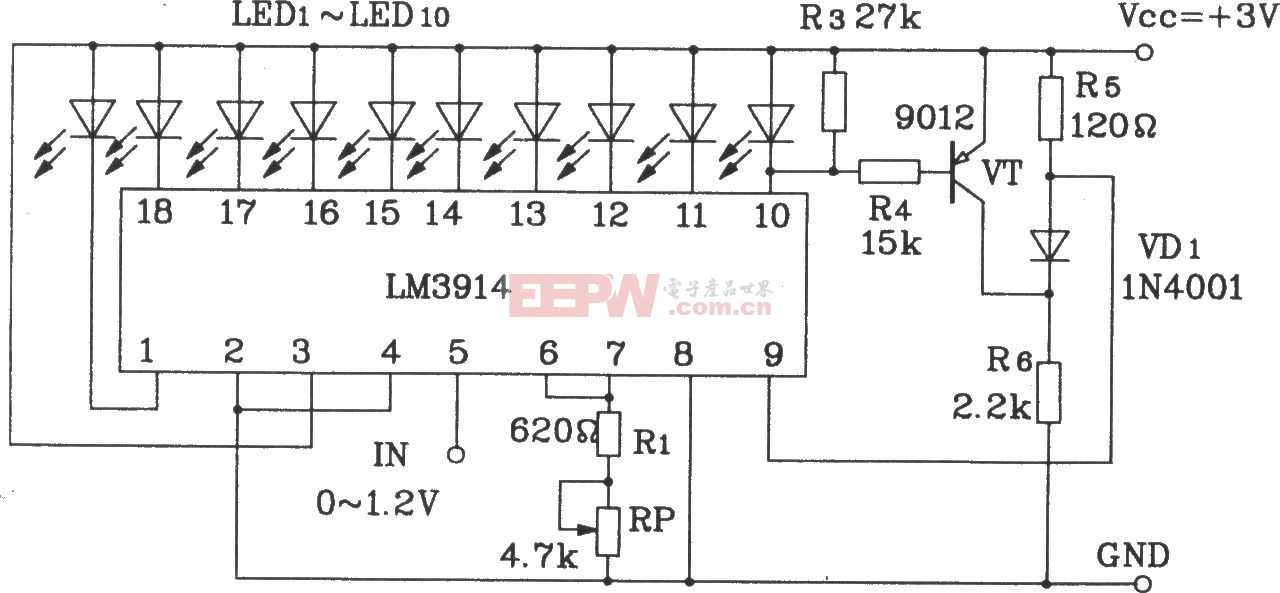

以 BBU 一側(cè)為例,雙系統(tǒng)時鐘方案具體實現(xiàn)方式如下圖 4 所示。在這個方案中,由于 LMK04808具有超低相位噪聲特性,我們使用它作為抖動消除器。

圖 4 采用雙時鐘方案構(gòu)建 BBU SERDES 系統(tǒng)

對圖 4 所示的系統(tǒng),系統(tǒng)配置及操作順序如下:

1) 正常配置 TLK10002 0X00 到 0X0D 寄存器。

2) 等待 TLK10002 高速側(cè)鎖相環(huán) HS PLL 正常鎖定。//只要本地參考時鐘準(zhǔn)備就緒,高速側(cè)鎖相環(huán)即可鎖定(此時并不需要建立穩(wěn)定的 10G 鏈路)。

3) 切換 TLK10002 ENRX:先置為 0,再置為 1。//使 HS SERDES 自適應(yīng)鏈路狀況。

4) 等待 10ms。 //等待 HS SERDES 設(shè)置參數(shù),確保 CDR 為 LMK04808 提供有效的參考時鐘。

評論