MPC860的HDLC通道驅動程序的設計與實現

3 驅動程序的設計思想及其實現

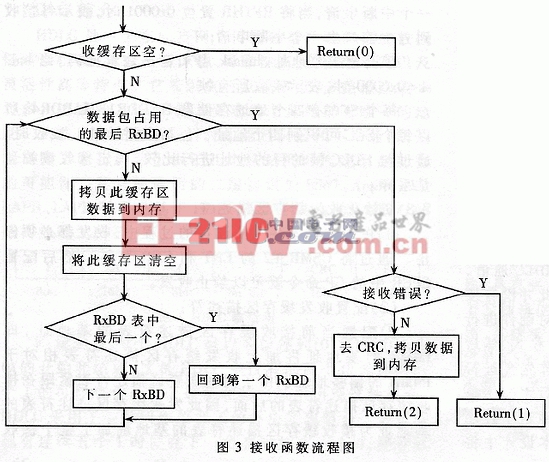

這里選擇VxWorks作為本CPU板的操作系統。VxWorks是美國風河系統公司推出的一種高性能、可裁減的實時嵌入式操作系統,以其良好的可靠性和卓越的實時性被廣泛應用于通信、軍事、航天等領域。因此,程序的設計必須按照這個操作系統的結構來構建。本文的主要目的是將MPC860處理器的一個SCC通道配置成為HDLC模式,以支持VxWorks操作系統下的HDLC通信,所以程序的設計主要圍繞這個目的進行,在此并沒有按照傳統驅動的模式構建驅動程序,而是直接對硬件進行操作。首先設置通道參數,將其配置成HDLC模式,然后設計基本功能函數。當驅動程序運行時,首先要進行SCC通道的初始化以及存儲區的初始化,然后才開始執行收發功能,在這當中要加上中斷控制。按照這個程序的基本流程,具體的實現分為下面幾步(在本設計中將SCC2配置成HDLC模式)。本文引用地址:http://www.104case.com/article/202570.htm

3.1 定義參數RAM

參數RAM主要包括通道參數RAM和通道協議參數RAM兩部分,SCC通道的主要參數都在這個里面配置。它們包含CPM RISC用來正確操作SCC通道的特定協議所用的信息。

3.2 初始化SCC2

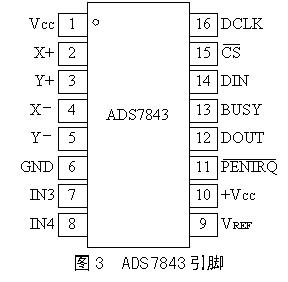

(1)將MPC860的PA12、PA13引腳作為SCC2的收發引腳。

(2)MPC860有四個BGR和八個外部時鐘引腳,將SCC的收發時鐘分別配置成內部時鐘和外部時鐘。

(3)將SCC2配置為NMSI模式。

(4)初始化SDCR寄存器,給予SDMA一個仲裁ID以提供U總線上的優先級。

(5)初始化SCC2的參數RAM(這步對所有的協議都是通用的):

①設置Rx/TxBD 表的基址相對于雙端口RAM的偏移量;

②設置收發緩沖區描述符表基址相對于IMMR寄存器中值的偏移量;

③設置Rx/Tx 的函數代碼;

④在MRBLR中設置接收緩存的最大空間。

(6)針對SCC2的HDLC模式進行初始化;

①通過C_MASK和C_PRES 設置CCITT-CRC;

②對CPM維護的五個計數器DISFC、CRCEC、 ABTSC、 NMARC和RETRC清零;

③在MFLR中定義最大幀長度,通常定義為0x0100,表示最大幀長度為256字節;

④在RFTHR中定義接收到多少個HDLC幀時產生一個中斷申請,當將RFTHR置位0x0001時,表示每接收到一個幀產生一個中斷申請;

⑤設置接收地址,hmask用來定義地址掩碼,當hmsk=0x0000時,表示接收所有幀。

評論