發現SW大小波,應該聯想到什么?應排查什么?

大家在測試電源電路時,有時會碰到輸出電壓異常、輸出紋波過大等情況,此時通常會排查 SW 信號來判斷電路工作是否正常,異常狀況下 SW 波形會呈現大小波現象。

本文引用地址:http://www.104case.com/article/202503/468686.htm今天我們就來一起看下,SW 出現大小波的常見原因有哪些?應該排查什么?

一、SW 大小波現象簡介

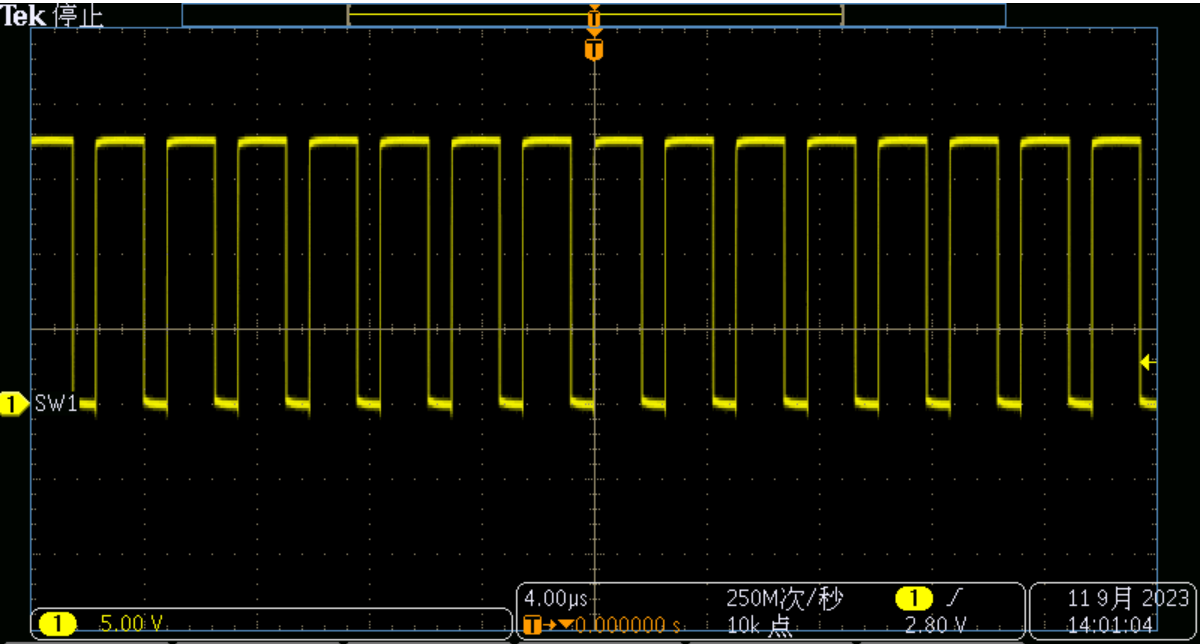

SW 代表 BUCK 電路中的開關節點。在標準工作條件下,SW 點的波形表現為固定頻率的方波。

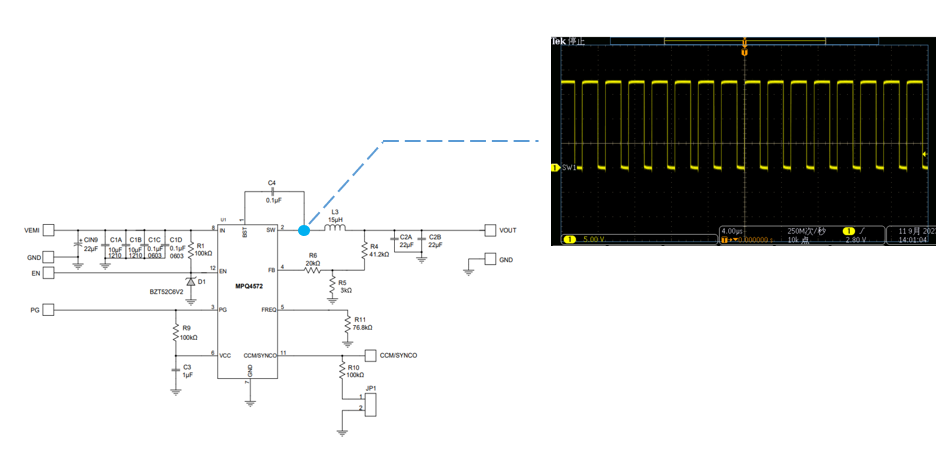

圖1 正常工況下的SW波形

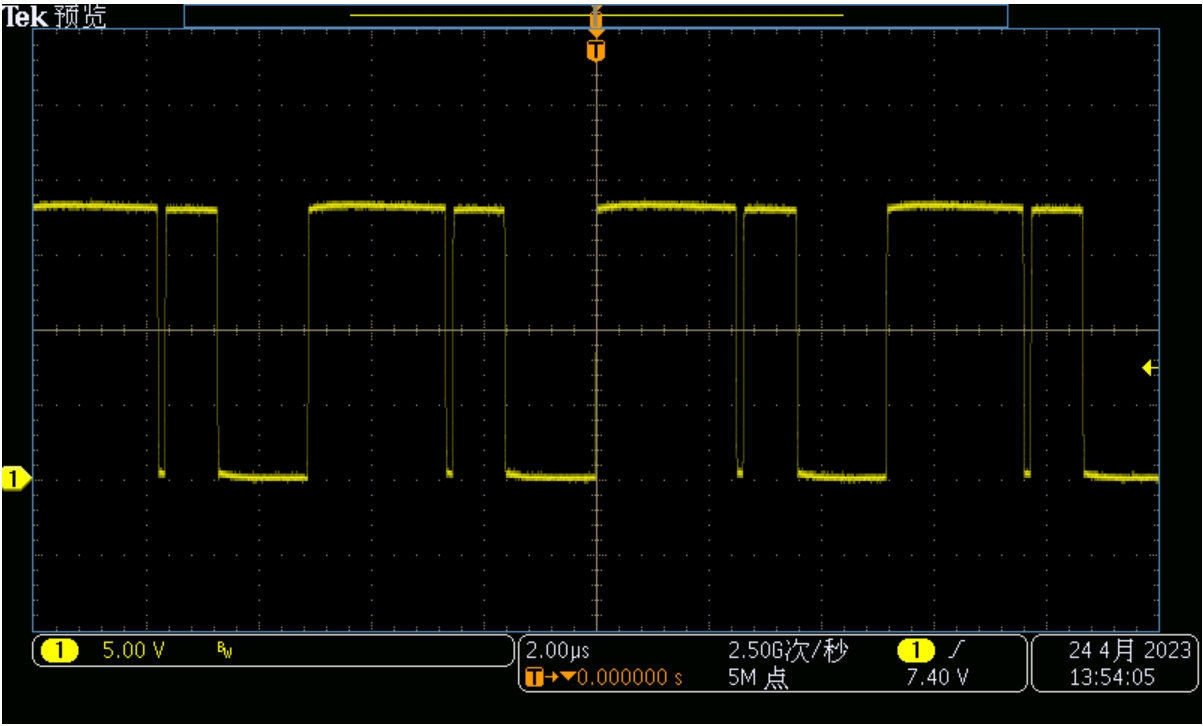

然而,在某些異常情況下,SW 波形會呈現大小波狀態。通常伴隨著輸出電壓不穩定、效率降低、芯片異常發熱,以及噪聲紋波增大等問題。

因此,在開關電源設計中,通常需要采取措施來控制 SW 節點上的電壓波動,以確保電源的穩定性和可靠性。

圖2 SW大小波

二、SW 大小波現象的原因分析

電路中 SW 出現大小波可能有以下幾種原因:

● 負載變化

● 輸入電壓不穩定

● 環路控制和補償設計不當

● PCB布局布線不合理

本文將從原理圖設計和 PCB 設計兩個方面,分析 SW 出現大小波的原因,并介紹對應的解決辦法。

在原理圖設計方面,我們從控制模式展開分析。

在 PCB 設計方面,從對 SW 影響最大的輸出電壓采樣走線和 FB 走線展開分析。

三、原理圖設計

在控制模式方面,目前常用的有峰值電流模式控制和 COT 控制。

峰值電流模式下的 SW 異常狀態我們通過 MPQ4572 舉例分析:

1.峰值電流控制模式

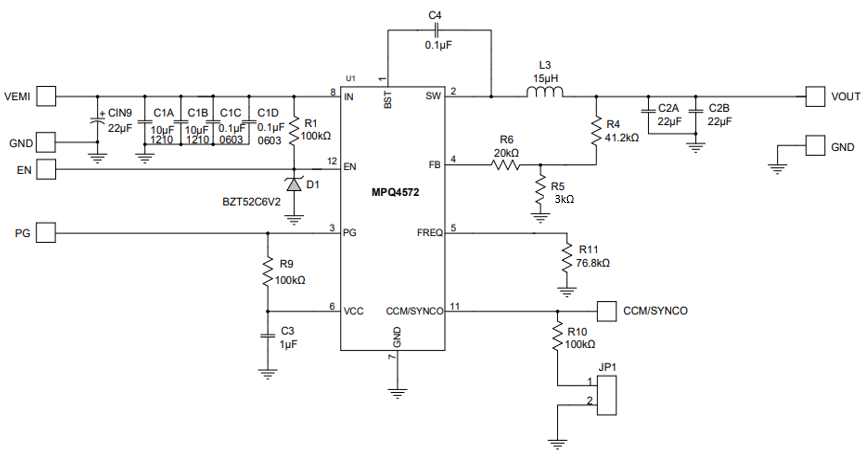

圖3 MPQ4572參考設計

MPQ4572 是一款支持 4.5V 到 60V 的寬輸入電壓范圍,持續輸出電流 2A,采用峰值電流控制模式的降壓芯片。

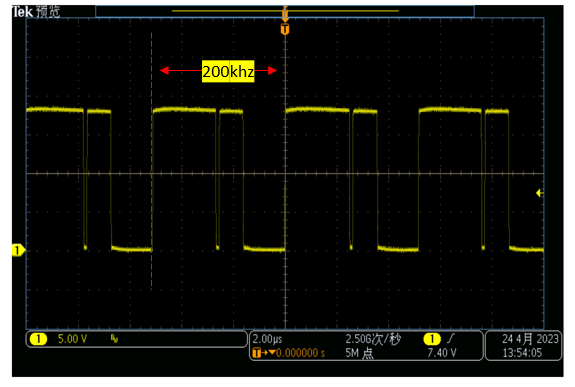

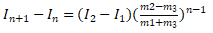

測試該芯片,設置開關頻率為 400kHz,當 Vin=18V,Vout=12V,帶載 1A 時,SW 出現了大小波,為周期性不規則波形,變化周期為 200kHz,剛好是開關頻率的一半,這種現象可能是由次諧波振蕩引起的。

圖4 SW大小波

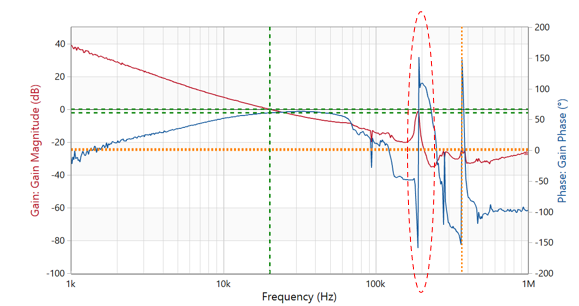

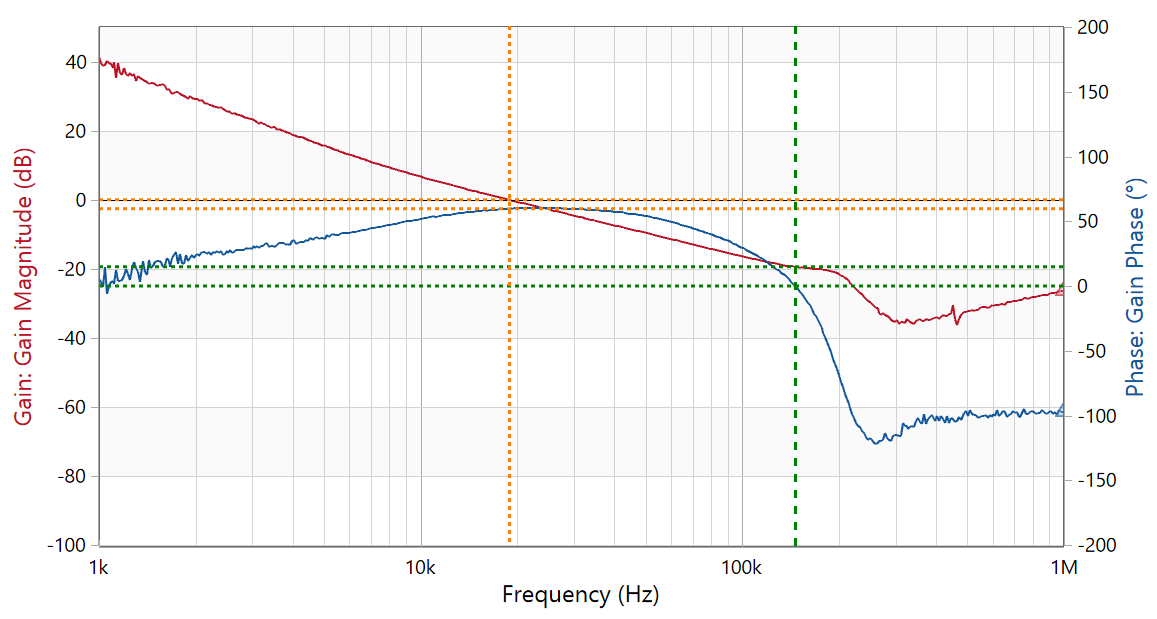

測試當前的環路波形,根據 bode 圖可以看到在 200kHz 時,增益曲線出現尖峰,相位曲線翻轉,可以判斷是發生了次諧波振蕩。當輸入電壓升高到 25V 以上時,SW 波形恢復正常。

圖5 環路測試

計算兩種輸入下的占空比分別為 :

Vin=18V,Vout=12V:D=66.7%>50%,

Vin=25V,Vout=12V:D=48%<50%,

已知在峰值電流模式下,當占空比大于 50% 時,系統可能會變得不穩定,出現次諧波振蕩,SW 呈現大小波。

為了抑制這種振蕩,通常會在控制回路中注入斜坡補償信號。但 MPQ4572 芯片的內部已經設計有斜坡補償機制,為什么還是會出現次諧波振蕩的問題呢?

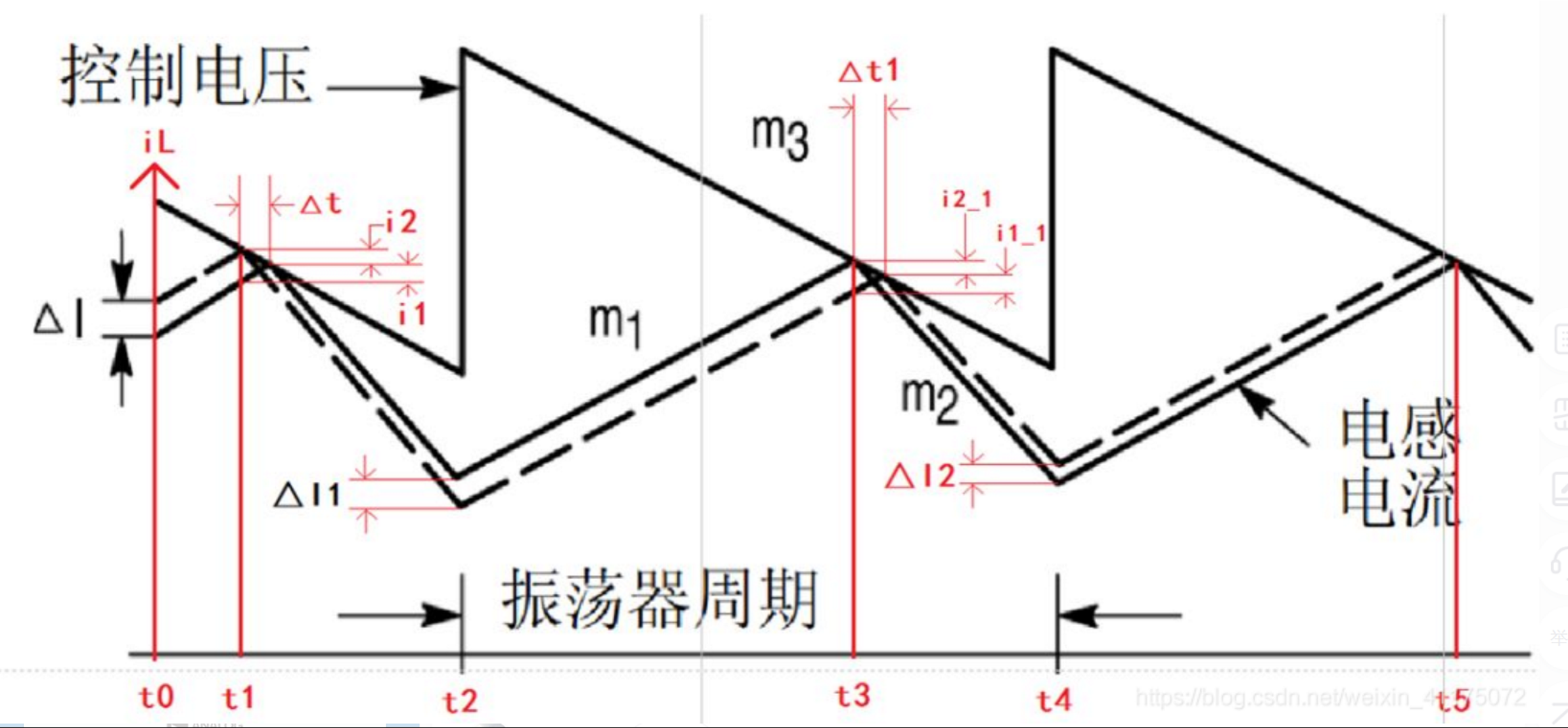

圖6 斜坡補償

在注入斜坡信號后,擾動量的公式為:

為了保證電路工作穩定,要讓擾動量收斂。注入的斜坡斜率 m3 要大于 0.5 倍 m2 才能使該式收斂。如果 m3 小于 0.5 倍 m2,即使注入了斜坡信號,也無法解決次諧波振蕩問題。

芯片內部注入的斜坡信號斜率通常是未知的固定值,也就是說 m3 是固定的,那么我們可以通過增加電感感量減小 m2 來保證 m3>0.5 倍 m2 成立。當電感感量由 15uh 修改為 33uh 后,SW 波形恢復正常。

圖7 正常SW波形

測試此時的 bode 圖,200kHz 時的增益曲線尖峰消失,環路穩定。

圖8 33uh環路測試

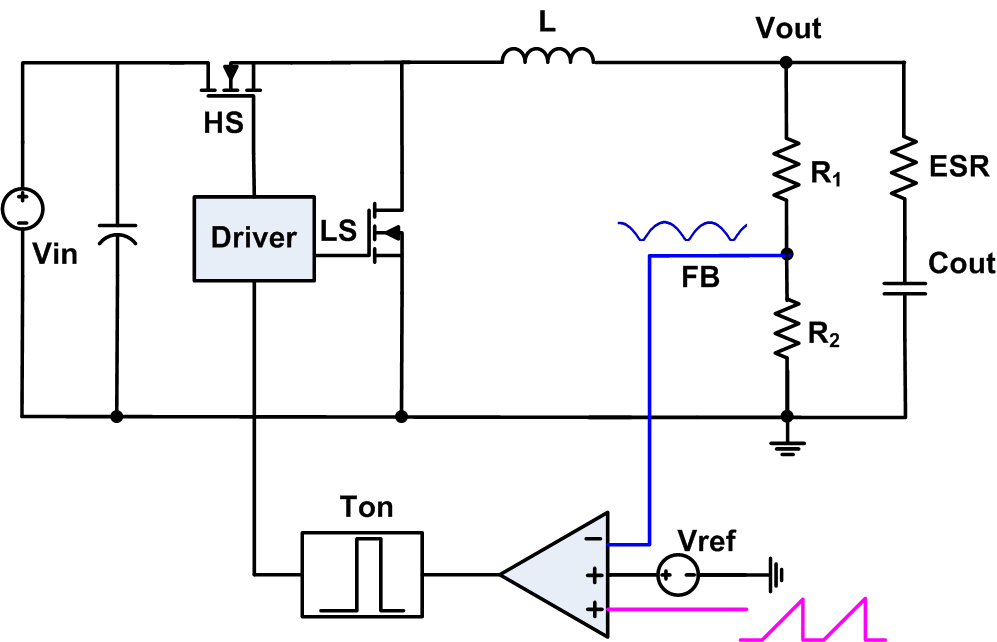

2.COT控制模式

COT 是通過比較 Vref 與 FB 管腳的電壓來實現恒壓控制,理想的 FB 電壓與電感電流同相位。

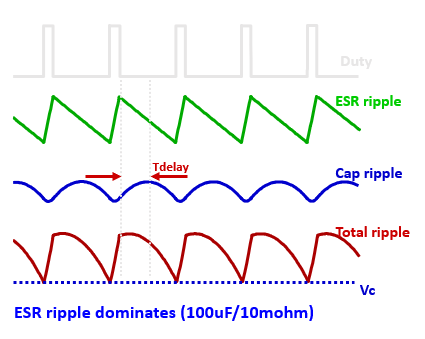

FB 采樣的輸出電壓紋波信號由電容紋波與 ESR 的紋波組成,電容紋波相較電感電流紋波有 90 度的延遲,當輸出紋波主要由輸出電容決定時,電路相位滯后,FB 信號非線性,會導致次諧波振蕩,SW 出現大小波。

在這種模式下,我們有三種方法可以用來抑制次諧波:

(1)使用 ESR 足夠大的電容

ESR 越大,總的電路相位延遲越小,紋波接近線性,可以有效抑制次諧波振蕩。

圖9 ESR紋波占主導

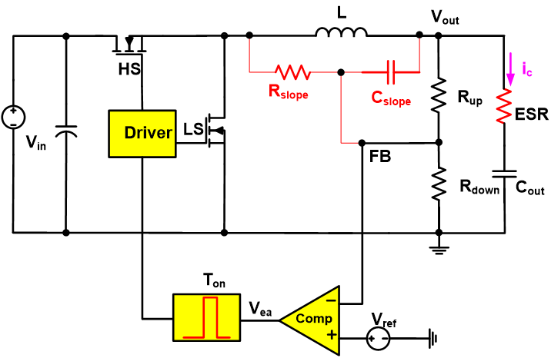

(2)注入斜坡補償

當為了效率及輸出紋波幅度考慮,需要選擇 ESR 比較小的電容時,我們可以選擇注入斜坡補償。通過外部的 RC 補償給 FB 管腳注入斜坡信號,由 Rslope 引入電感紋波,Cslope 提高相位,整體相位提升,可以抑制次諧波。

圖10 斜坡補償

具體參數如何計算可參考:MPS官網-設計-應用說明-通用-Designing a Stable COT Converter for a Desired Load and Line Regulation 的設計案例 。

(3)設置 Ramp

Ramp 的相位與電感紋波電流相位一致,部分芯片的 Ramp 可以通過 PMBUS 配置,Ramp 越大,系統越穩定,Ramp 越小,動態響應越快,實際應用中需要平衡穩態性能和動態性能。

圖11 設置Ramp

四、PCB設計

在 PCB 設計上,規避 SW 振蕩的要點包括:

(1)輸出電壓采樣走線應盡量短、直,避免干擾。

(2)FB 管腳比較敏感,應遠離噪聲源,如 SW 點、電感等。

(3)FB 分壓電阻要靠近管腳放置并確保 FB 走線短直。

五、總結

峰值電流模式控制下,確保斜坡注入信號的有效性至關重要。

在 COT 控制模式下,當輸出紋波由 ESR 主導時,電路穩定;由電容紋波主導時,可能出現次諧波振蕩。此時,我們可以通過選用 ESR 較大的電容、增加外部 RC 補償或內部配置 RAMP 來解決問題。

最后,良好的 PCB 設計也是確保電源穩定性的關鍵。

評論