傳輸晶體管邏輯簡(jiǎn)介

低電阻路徑

本文引用地址:http://www.104case.com/article/202502/466944.htm這個(gè)問(wèn)題的基本答案是,邏輯高表示電源軌上的電壓,代表二進(jìn)制 1,邏輯低表示地電壓,代表二進(jìn)制 0。這個(gè)描述是一個(gè)很好的起點(diǎn),它變得更如果我們說(shuō)“靠近電源軌”和“靠近地”而不是“在電源軌處”和“在地”,那么是準(zhǔn)確的。此修改考慮了流過(guò) NMOS 或 PMOS 溝道的電流在源極和漏極之間產(chǎn)生小電壓差的事實(shí)。

流經(jīng)通道的電流問(wèn)題會(huì)導(dǎo)致典型 CMOS 功能的一個(gè)更微妙但至關(guān)重要的方面。 CMOS 反相器確保輸出節(jié)點(diǎn)與電源軌或地具有低電阻連接;反相器總是NMOS導(dǎo)通、PMOS截止或PMOS導(dǎo)通、NMOS截止。這就是為什么我們可以說(shuō) CMOS 電路驅(qū)動(dòng)邏輯低或邏輯高。這也是為什么圍繞逆變器拓?fù)錁?gòu)建的邏輯電路如此可靠的“數(shù)字”——所有節(jié)點(diǎn)都具有明確定義的二進(jìn)制狀態(tài),因?yàn)樗鼈兪冀K具有通向電源電壓或接地的低電阻路徑。

傳輸晶體管邏輯 (PTL) 也稱(chēng)為傳輸門(mén)邏輯,基于使用 MOSFET 作為開(kāi)關(guān)而不是逆變器。結(jié)果是(在某些情況下)概念上的簡(jiǎn)化,但 CMOS 反相器嚴(yán)格的邏輯高/邏輯低輸出特性丟失了。

傳輸晶體管邏輯的示例

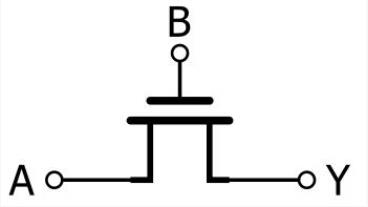

可以使用單個(gè)NMOS晶體管作為PTL開(kāi)關(guān);當(dāng)施加到柵極的電壓為邏輯高時(shí),開(kāi)關(guān)被認(rèn)為是閉合的,而當(dāng)施加到柵極的電壓為邏輯低時(shí),開(kāi)關(guān)被認(rèn)為是打開(kāi)的。下圖顯示了僅使用一個(gè)晶體管的與門(mén)(或至少類(lèi)似于與門(mén)的東西)。

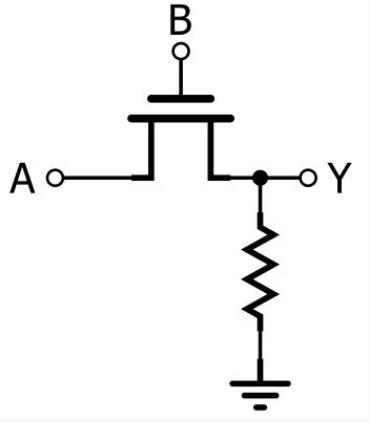

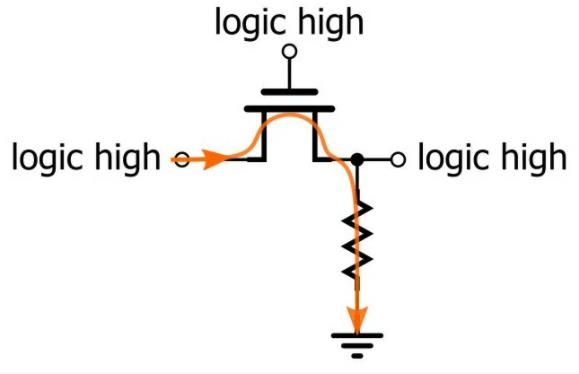

當(dāng)輸入 (A) 為邏輯高且開(kāi)關(guān)控制信號(hào) (B) 為邏輯高時(shí),輸出 (Y) 為邏輯高,而對(duì)于所有其他組合,輸出 (Y) 都不是邏輯高。這聽(tīng)起來(lái)像“與”真值表,但我們真的可以將其稱(chēng)為“與”門(mén)嗎?這取決于你的觀(guān)點(diǎn)。問(wèn)題在于,當(dāng) B 輸入為邏輯低電平時(shí),電路不會(huì)驅(qū)動(dòng)邏輯低電平。它只是斷開(kāi)連接,即浮動(dòng)。為了建立邏輯低電平,我們需要一個(gè)下拉電阻:

現(xiàn)在我們有了一個(gè)功能性與門(mén),并且只使用了一個(gè)晶體管和一個(gè)電阻器,而基于 CMOS 反相器的標(biāo)準(zhǔn)與門(mén)需要六個(gè)晶體管。然而,PTL電路絕不等同于標(biāo)準(zhǔn)CMOS版本。首先,它不能可靠地提供低電阻接地路徑。其次,只要輸出為邏輯高電平,它就會(huì)消耗靜態(tài)功耗——電流從輸入流經(jīng) NMOS、下拉電阻到地:

這意味著我們失去了基于逆變器的邏輯的一個(gè)極其有益的特性,即電源僅在開(kāi)關(guān)期間提供大量電流。 (這就是為什么 CMOS 功耗與頻率成正比——更多的開(kāi)關(guān)意味著更多的電流,更多的電流意味著更多的功率。)

傳輸晶體管邏輯中的 NMOS 與 CMOS

如上一節(jié)所示,PTL 圍繞 MOSFET 開(kāi)關(guān)構(gòu)建,這些開(kāi)關(guān)可以傳遞(因此得名)或阻止信號(hào)。使用 NMOS 晶體管作為開(kāi)關(guān)無(wú)疑是減少晶體管數(shù)量的好方法,但單獨(dú)的 NMOS 在性能方面并不令人印象深刻。更好的解決方案是 CMOS 傳輸門(mén):

本文對(duì)單獨(dú)的 NMOS 和 CMOS 傳輸門(mén)進(jìn)行了簡(jiǎn)要比較。毫無(wú)疑問(wèn),一般來(lái)說(shuō),傳輸門(mén)是更好的實(shí)現(xiàn)方式,但請(qǐng)考慮權(quán)衡。顯然需要一個(gè)額外的晶體管,但還要注意,PMOS 不是由開(kāi)關(guān)控制信號(hào)驅(qū)動(dòng),而是由開(kāi)關(guān)控制信號(hào)的補(bǔ)碼驅(qū)動(dòng)。例如,如果生成輸入信號(hào)的電路是提供

輸出的D 觸發(fā)器,則這不是問(wèn)題。不過(guò),通常只有一個(gè)輸入信號(hào)可用,在這種情況下,使用 CMOS 傳輸門(mén)意味著我們還必須有一個(gè)反相器來(lái)為第二個(gè) FET 創(chuàng)建控制信號(hào)。

評(píng)論