干貨|TTL電路詳細講解,工作原理+電路圖

今天給大家分享的是:TTL電路的分析、TTL電路工作原理、TTL電路使用方法。

本文引用地址:http://www.104case.com/article/202407/461241.htm一、TTL電路是什么意思?

TTL 是一種集成電路,通過使用雙極晶體管來執(zhí)行邏輯功能以提供開關(guān)功能。TTL 設(shè)備最重要的特性是門的輸入在未連接時將為邏輯高電平 (1)。

該技術(shù)用于設(shè)計和制造集成芯片,其中包含邏輯門和雙極晶體管、電阻和二極管。TTL 設(shè)備解決了DTL中因使用晶體管代替二極管而出現(xiàn)的容性負載問題和速度問題,提供更好的噪聲抑制和容性負載特性。具有 10ns 的傳播延遲和 10mW 的功耗。

二、TTL 邏輯電平

我們使用的大多數(shù)系統(tǒng)都依賴于 3.3V 或 5V TTL 電平。TTL 是晶體管-晶體管邏輯的縮寫。由雙極晶體管構(gòu)建的電路來實現(xiàn)切換和保持邏輯狀態(tài)。

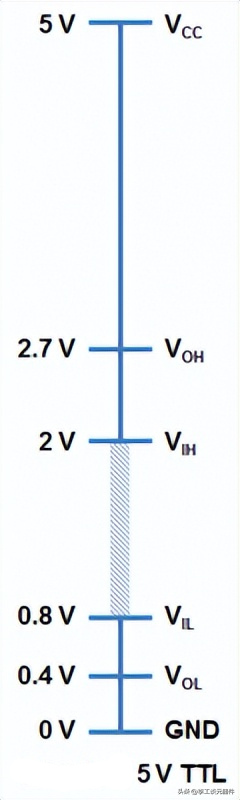

對于任何邏輯系列,閾值電壓電平是必須要了解的一個點。以下是標準 5V TTL 電平的示例:

V OH ——TTL 設(shè)備將為高信號提供的最小輸出電壓電平。

V IH -- 被視為高電平的最小輸入電壓電平。

V OL -- 設(shè)備將為低信號提供的最大輸出電壓電平。

V IL——仍被視為低電平的最大輸入電壓電平。

從上圖中可以看到最小輸出高電壓(VOH)為2.7V。這意味驅(qū)動高電平設(shè)備的輸出電壓至少為2.7V。最小輸入高電壓 (V IH ) 為 2 V,意味著基本上2V以上的電壓都將作為邏輯1(高)讀入TTL設(shè)備。

應該還可以注意到一個設(shè)備的輸出與另一個設(shè)備的輸入之間存在0.7V的緩沖,被稱為噪聲容限。

同樣,最大輸出低電壓 (V OL ) 為 0.4 V,發(fā)出邏輯0的設(shè)備將低于0.4V。最大輸入低電壓 (V IL ) 為 0.8 V,意味著低于0.8V的輸入信號在讀入設(shè)備都是邏輯0。

如果電壓介于 0.8 V 和 2 V 之間會怎樣?這個電壓范圍是不確定的,會導致無效狀態(tài),通常稱為浮動。如果在設(shè)備上的輸出引腳在此范圍內(nèi)“浮動”,則無法確定信號會產(chǎn)生什么結(jié)果,可能會在高電平和低電平之間任意反彈。

三、TTL電路如何工作?

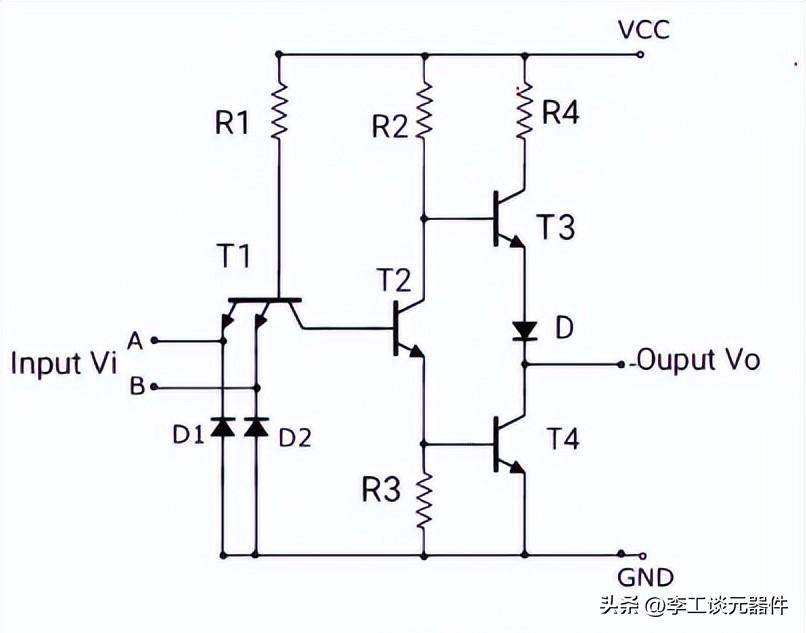

下面為標準TTL邏輯門的電路圖,正 NAND 門功能,如下圖所示。這種標準的TTL邏輯電路在某些情況下與二極管-晶體管邏輯(DTL)電路有關(guān)。

具有 2 輸入與非門的 TTL 電路

從上圖可以看出,T1是輸入三極管,在開關(guān)時間上有優(yōu)勢。晶體管 T2 是分相器,晶體管 T3 和 T4 提供圖騰柱輸出。該 TTL 電路具有極低的輸入阻抗、高扇出和更好的抗噪性,并且能夠進行高電容驅(qū)動。

當輸入 A 和 B 為高電平時,晶體管 T2 和 T3 導通并充當共發(fā)射極放大器。晶體管 T4 和發(fā)射極處的二極管正向偏置,并且流過的電流量可以忽略不計。輸出為低電平,代表邏輯 0。

當兩個輸入均為低電平時,二極管 D1 和 D2 正向偏置。由于 5V 的電源電壓 VCC,電流通過 D1 和 D2 以及電阻 R1 流向地面。R1 中的電源電壓下降,晶體管 T2 關(guān)斷,因為它沒有足夠的電壓來導通。因此,晶體管T4也因T2截止而截止。晶體管 T3 導通(高電平)并充當射極跟隨器。輸出為高電平,代表邏輯 1。

當輸入 A 和 B 中的任何一個為低電平時,二極管就會由于低輸入而正向偏置。整個操作與上述相同。因此,輸出為高電平(邏輯 1)。

四、TTL電路電路使用方法

TTL 有不同的類型,如下所示:

標準TTL電路

快速TTL電路

肖特基TTL電路

大功率TTL電路

低功耗 TTL電路

高級肖特基 TTL電路

下面介紹幾招那個TTL電路:

1、標準TTL電路

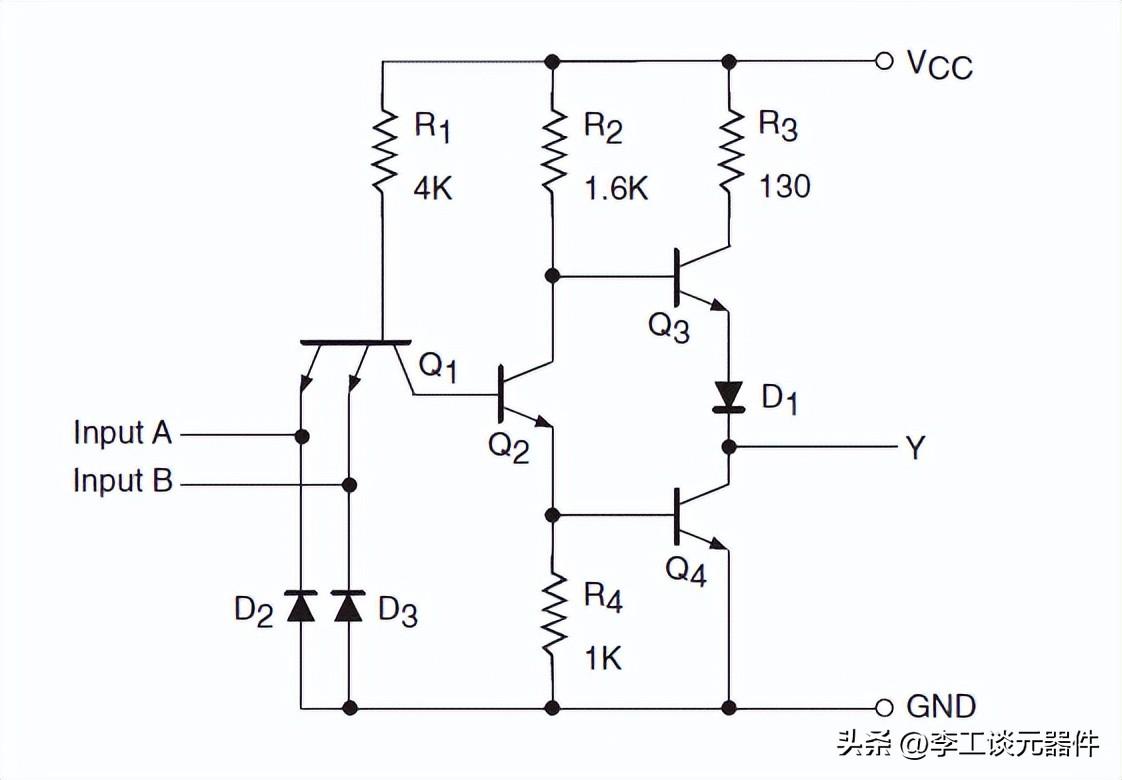

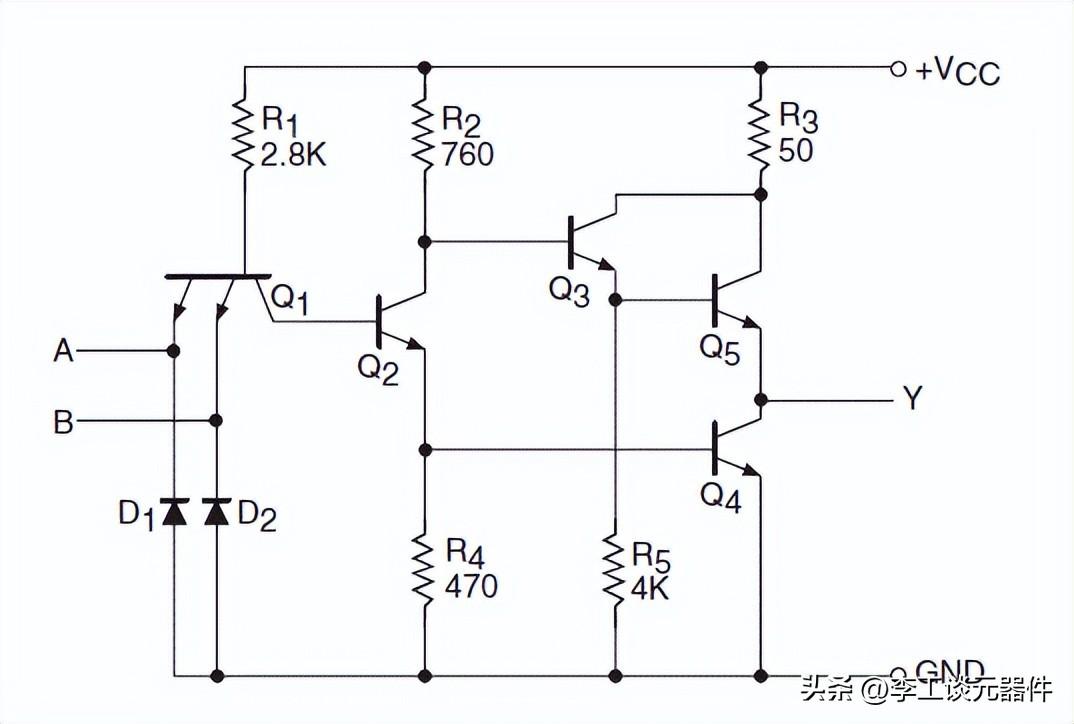

下圖顯示了標準TTL與非門的內(nèi)部結(jié)構(gòu)和特性。它的與非門是四路二輸入型。有四個5400/740電路。簡單來說,這種類型的 TTL 電路的工作原理如下。

標準TTL與非門

圖中所示的 Q1 是一個雙發(fā)射極NPN晶體管,這種類型的與非門類似于兩個晶體管,它們的基極和發(fā)射極端子連接在一起。命名為D 2和D 3的二極管用于限制本質(zhì)上為負的輸入電壓。

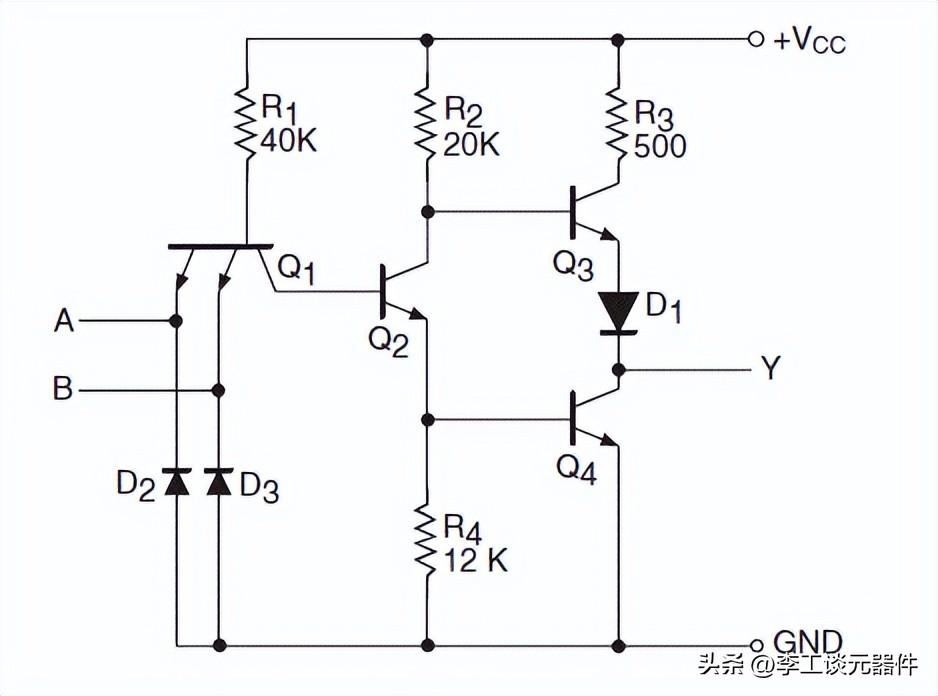

2、低功耗 TTL電路

低功耗TTL電路實現(xiàn)了較低的功耗和耗散。盡管完成操作的速度有所降低。上圖是使用與門制作的低功耗TTL。這里用到的與非門是74L00或54L00型的,這種類型的 TTL 的結(jié)構(gòu)幾乎與標準 TTL 的結(jié)構(gòu)相似,只是電阻值更高。對于這個增加的電阻值,電路的功耗降低了。

低功耗 TTL電路

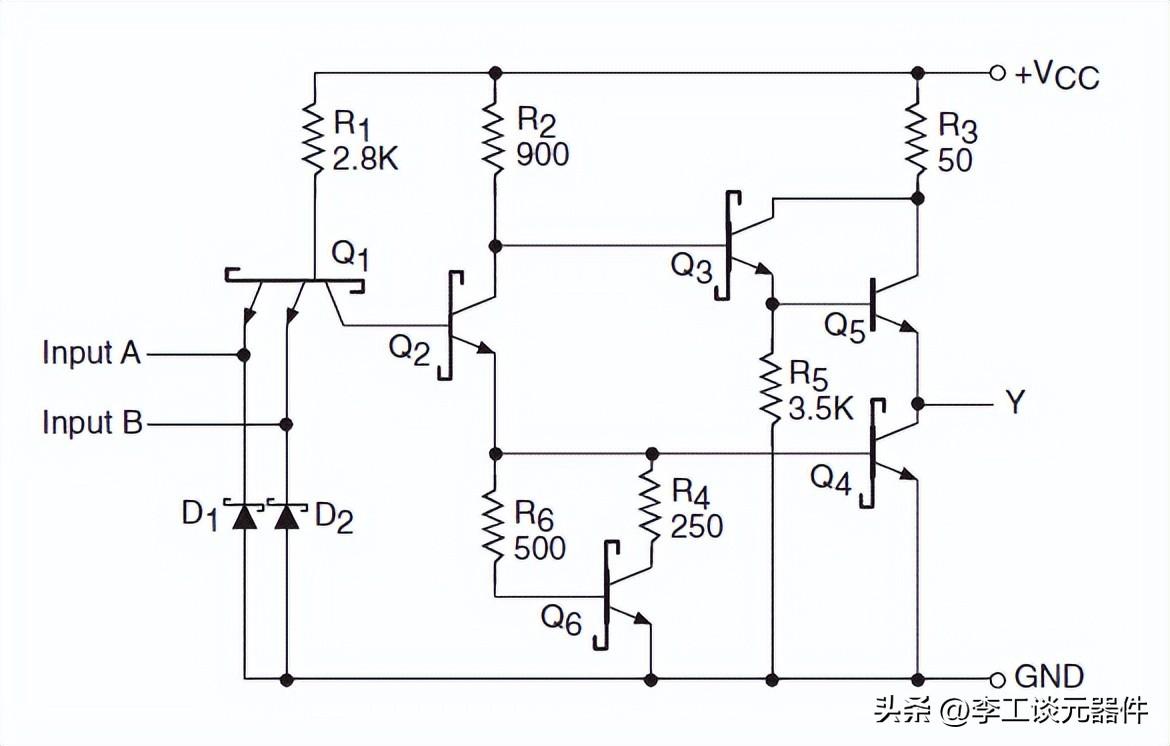

3、大功率TTL電路

與低功率 TTL 不同,高功率 TTL 是標準 TTL 的高速版本。這種類型的 TTL 的運行速度比前面討論的要快。其功耗高于之前討論的其他 TTL。下圖是高功率 TTL 與非門。與非門是 74H00 或 54H00 類型的四路二輸入。與標準 TTL 非常相似,只是 Q 3晶體管和 D 1 二極管組合已被 Q 3、 Q 5和 R 5的排列所取代。這種類型的 TTL 的運行速度更高,功耗也更高。

大功率TTL電路

4、肖特基TTL電路

肖特基 TTL電路用于加快操作時間。這種類型的 TTL 提供的速度是高功率 TTL 提供的速度的兩倍。兩個 TTL 的功耗相同,沒有額外的功耗。下圖表示基于 NAND 的基本肖特基 TTL 圖。

電路圖與大功率TTL非常相似,這里缺少大功率TTL的Q晶體管。用于這種TTL的肖特基晶體管是一個基極和集電極由肖特基二極管連接的雙極型晶體管。

肖特基TTL電路

五、TTL電路正確接線圖

這里從TTL電路輸入和輸出來看:

1、輸入

標準2輸入TTL電路

標準3輸入TTL電路

2、輸出

TTL圖騰柱輸出

TTL集電極開路輸出

TTL三態(tài)門輸出

1、標準2輸入TTL電路

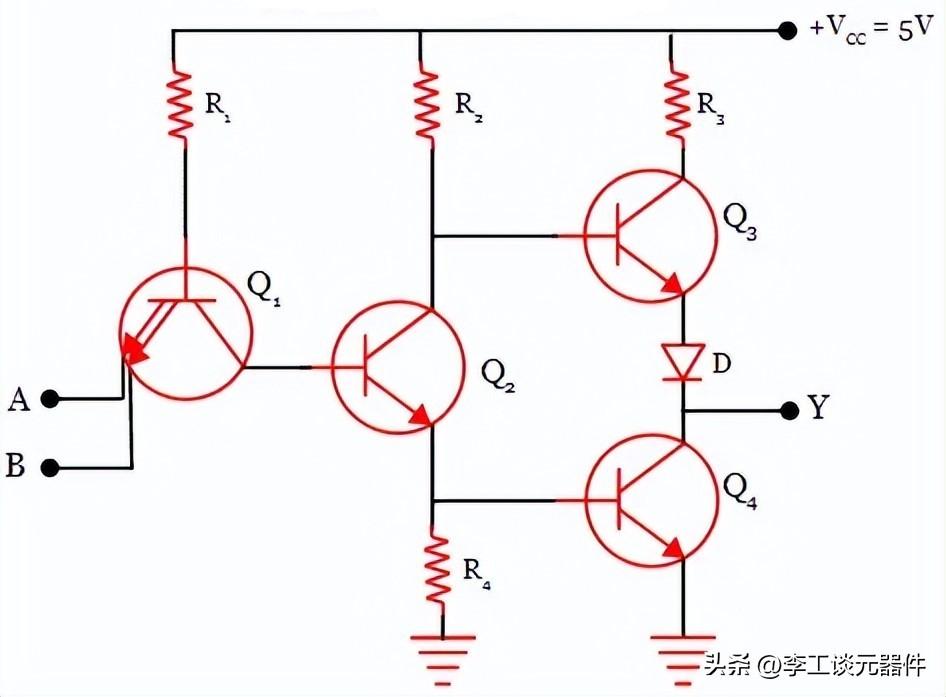

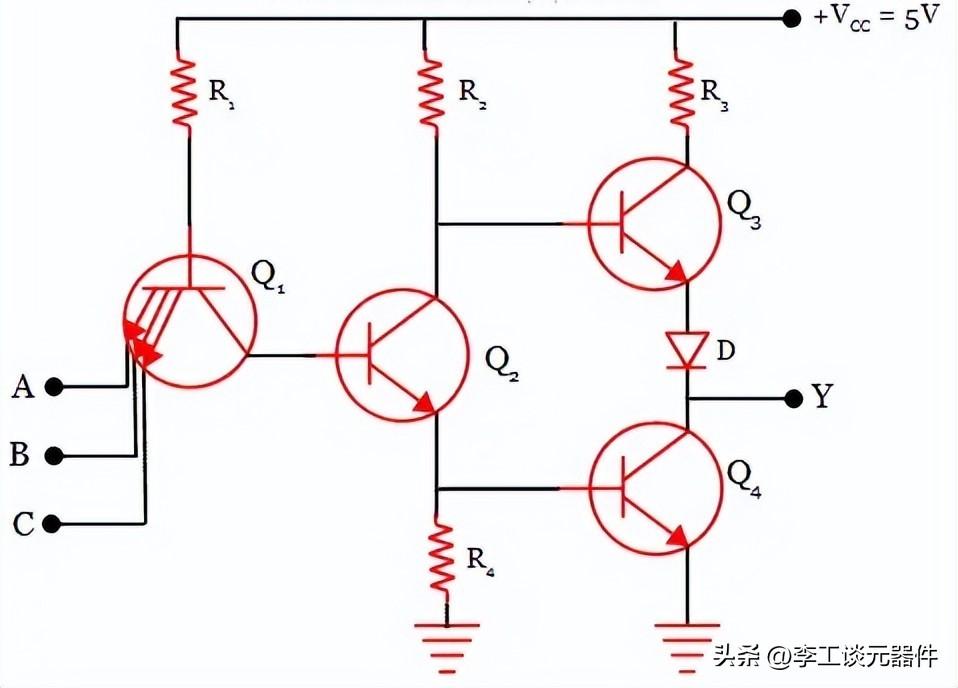

下圖為2輸入TTL與非門的電路圖。它有四個晶體管Q 1、Q 2、Q 3和Q 4。晶體管 Q 1在發(fā)射極側(cè)有兩個輸入端。三極管Q 3和Q 4組成輸出端,稱為圖騰柱輸出。

標準2輸入TTL電路

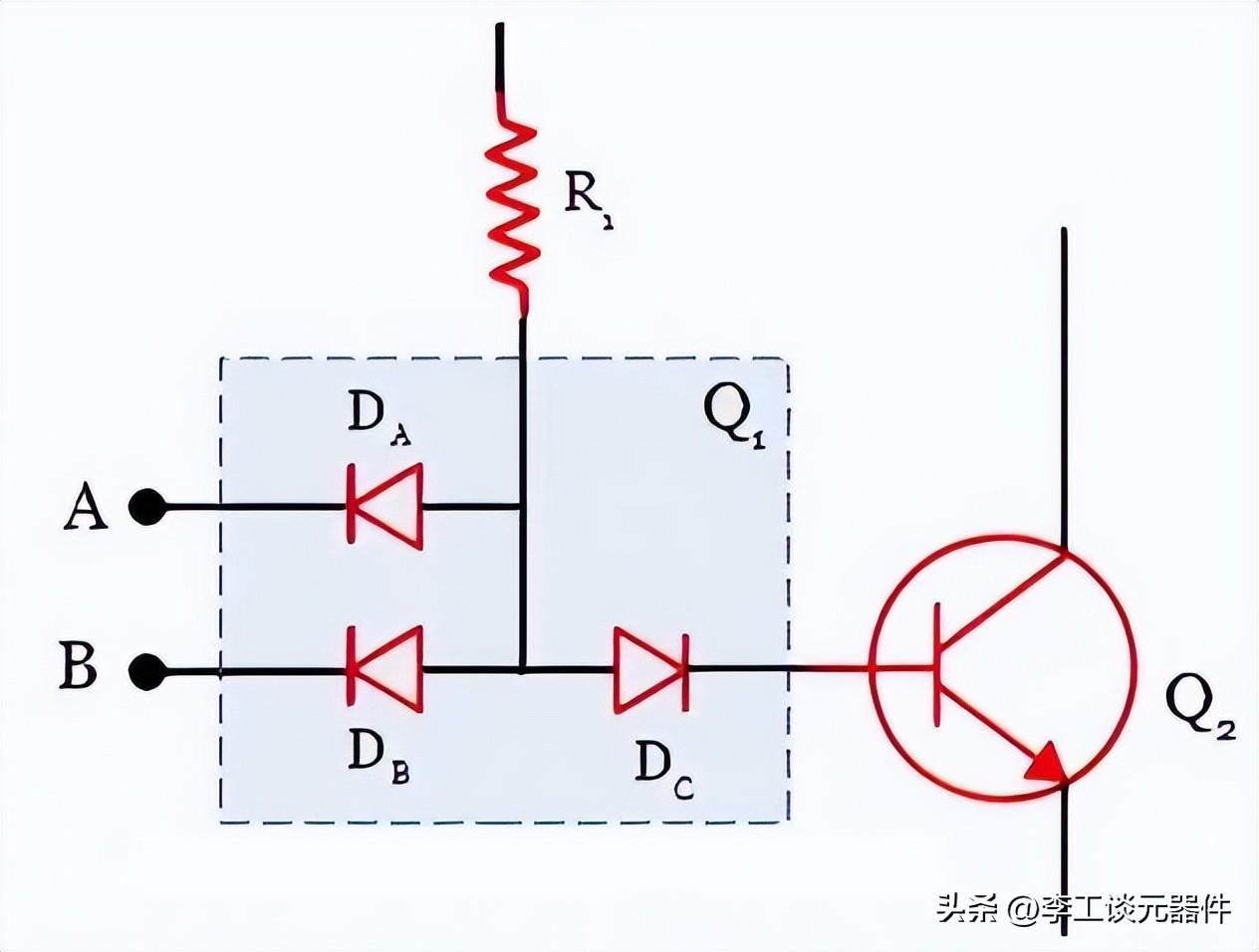

2 輸入 TTL 與非門的電路可能看起來很復雜。我們可以通過考慮 2 輸入 NPN 晶體管的二極管等效來簡化其操作,如下圖所示。

標準2輸入TTL電路

在圖中,二極管DA和DB代表晶體管Q 1的2輸入發(fā)射極結(jié)。二極管 DC代表晶體管 Q2的集電極-基極結(jié)。

當輸入 A 和 B 均為低電平時,兩個二極管均正向偏置。因此,由于電源電壓 +V CC = 5 V 而產(chǎn)生的電流將通過 R 1 和兩個二極管 D A 和 D B 流向地面。

電源電壓在電阻 R 1中下降 ,不足以導通晶體管 Q 2。隨著 Q 2打開,晶體管 Q 4也將截止。但是晶體管Q 3被拉高。由于 Q 3是射極跟隨器,因此端子的輸出也將為高電平,即邏輯 1。

當任何一個輸入(A 或 B)為低時,具有低輸入的二極管將正向偏置。將發(fā)生與上述相同的操作,在這種情況下,輸出將為高電平。

當輸入 A 和 B 均為高電平時,發(fā)射極-基極結(jié)處的兩個二極管都將反向偏置。集電極-基極結(jié)處的二極管 D C正向偏置。它將打開晶體管 Q 2。隨著Q 2導通,晶體管Q 4也將導通。

輸出端的兩個晶體管都將導通,因此終端輸出將具有低電平,這被視為邏輯 0。

2、標準3輸入TTL與非門電路

下圖為標準3輸入TTL與非門電路。這與我們在2輸入TTL與非門電路中差不多,只是這里輸入晶體管Q 1具有三個發(fā)射極而不是兩個。工作原理與 2 輸入 TTL 與非門相同。

、標準3輸入TTL與非門電路

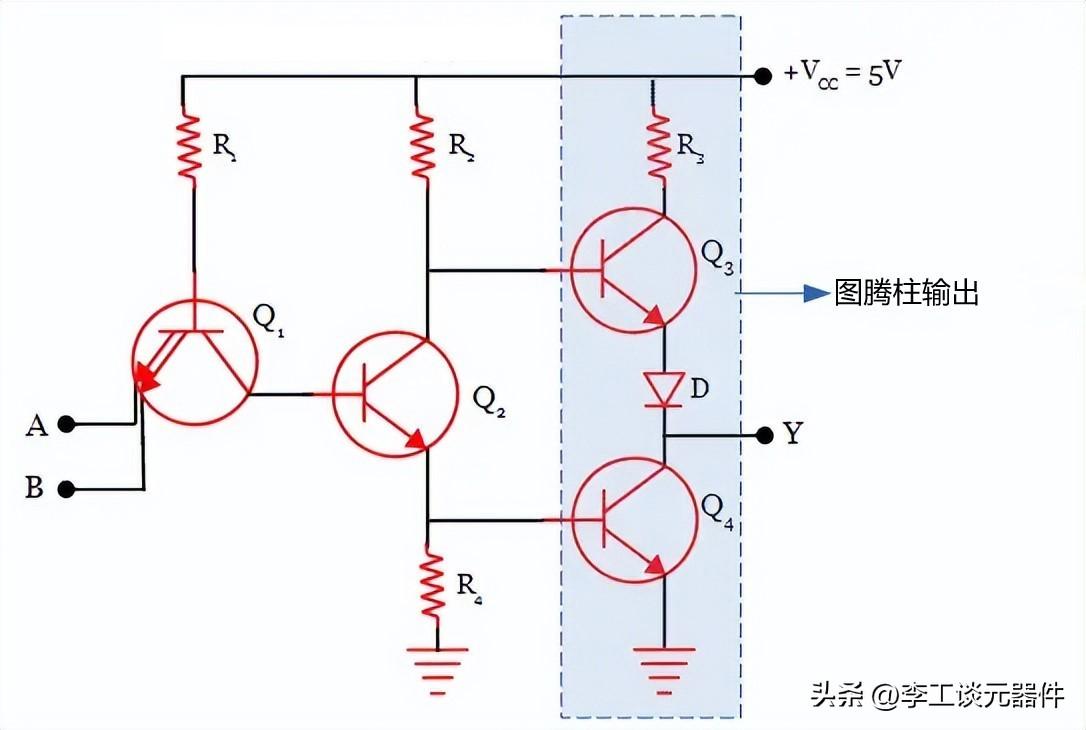

3、TTL圖騰柱輸出電路

在下圖所示的電路中,陰影部分表示圖騰柱輸出。三極管Q 3、Q 4、二極管D和限流電阻R 3構(gòu)成TTL的圖騰柱輸出結(jié)構(gòu)。

標準圖騰柱輸出,TTL電路具有以下特點和優(yōu)勢:

1、由于延遲時間短,與 DTL 相比,它們的運行速度相當高

2、抗噪性低(0.4V)

3、每個門的平均傳播延遲為 10 納秒 (ns)

4、平均功耗為 10mW

5、它的最大扇出為10,這意味著一個輸出可以驅(qū)動另外10個TTL輸入

6、其他數(shù)字電路的接口很容易。

7、與二極管相比,其中應用的多發(fā)射極晶體管占用的空間相對較小

8、該系列價格相對便宜,市場上大量供應

9、應用簡單易行

10、圖騰柱晶體管在二進制 1(高)狀態(tài)下提供非常低的輸出阻抗

11、TTL 設(shè)備是兼容的(即一個 TTL 設(shè)備的輸出可以作為輸入提供給另一個 TTL 設(shè)備。在這種情況下,第一個設(shè)備稱為驅(qū)動器,而第二個稱為負載)

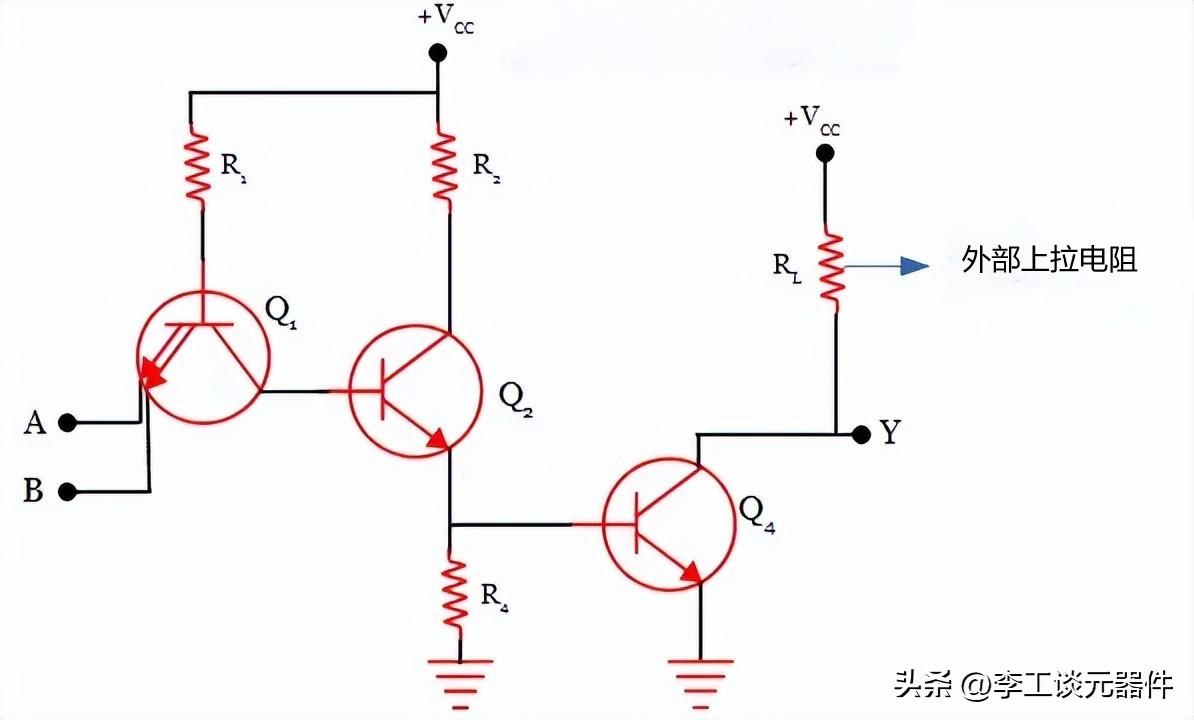

4、TTL集電極開路輸出電路

TTL邏輯的集電極開路輸出配置如下圖所示。在此配置中,取消了晶體管 Q 3和上拉電阻。取而代之的是外部上拉電阻以確保正常運行,如圖所示。

TTL集電極開路輸出

輸出取自 Q 4的集電極開路端子。當晶體管 Q 4關(guān)閉時,輸出 Y 將為高電平,而當 Q 4導通時,輸出將為低電平。

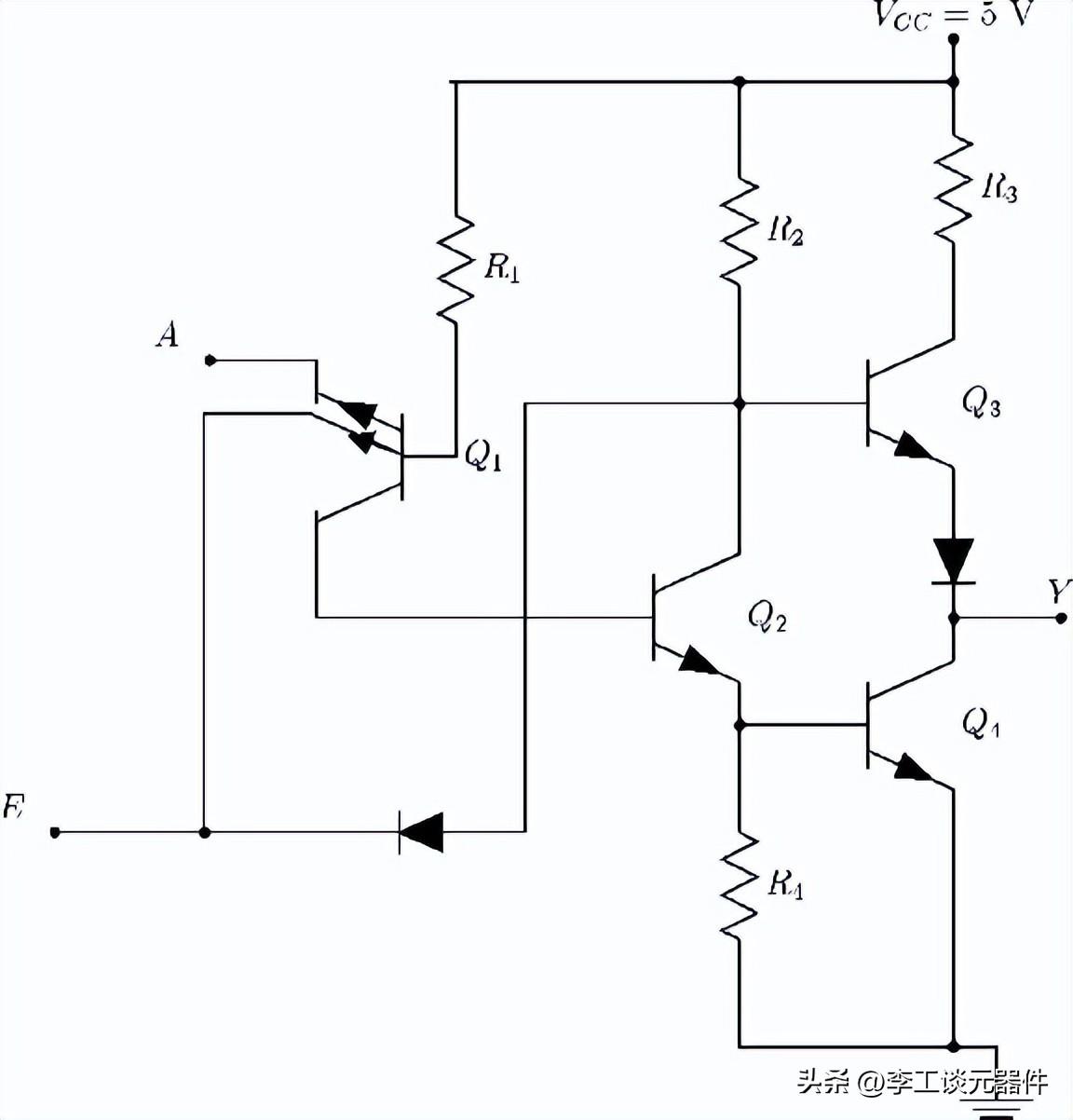

5、TTL三態(tài)門輸出電路

在這種輸出配置下操作晶體管時,可以獲得高阻抗。三種輸出狀態(tài)是:高、低和高阻抗。

三態(tài)邏輯電路利用圖騰柱排列的高速運行,同時允許輸出進行線與運算(連接在一起)。Hi-Z 狀態(tài)是圖騰柱排列中的兩個晶體管都關(guān)閉的狀態(tài),因此輸出端對地和 V CC為高阻抗。換句話說,輸出是一個開路或浮動終端,既不是低電平也不是高電平。實際上,輸出端并不是完全開路,而是相對于地和 V CC具有幾 MΩ 或更高的高電阻。

TTL三態(tài)門輸出電路

上圖顯示了三態(tài)逆變器的電路,該電路有兩個輸入:A 是正常邏輯輸入,F(xiàn) 是能夠產(chǎn)生 Hi-Z 狀態(tài)的啟用輸入。

當 F = 0 時,無論邏輯輸入 A 的狀態(tài)如何,電路都會進入其高阻抗狀態(tài)。F 處的低電平正向偏置晶體管 Q 1 的發(fā)射極-基極結(jié),并使電阻 R1 的電流從晶體管Q分流2使 Q 2關(guān)斷,從而使晶體管 Q 4關(guān)斷。E 處的低電平還正向偏置二極管 D 2以從晶體管 Q 3的基極分流電流,因此 Q 3也關(guān)閉。由于兩個圖騰柱晶體管都處于截止狀態(tài),因此輸出端基本上是開路。

具體的可以看如下真值表:F = 1 時,電路作為正常逆變器運行,因為 F 處的高輸入對晶體管 Q 1或二極管 D 2沒有影響。在此啟用條件下,輸出只是邏輯輸入的反相。

TTL三態(tài)門輸出電路真值表

TTL三態(tài)門輸出電路優(yōu)點:

高速運轉(zhuǎn),傳播延遲大約為 10 毫秒,與DTL和RTL邏輯器件相比更快。

與 DTL 和 RTL 相比功耗更低。

低成本。

更好的扇出。

噪聲可靠運行。

六、TTL的特征

TTL 的特性是扇入和扇出、功耗、噪聲容限和傳播延遲。

扇入和扇出:連接到柵極的輸入和輸出的數(shù)量,在不影響整體性能的情況下不會降低電壓。TTL 扇出10。

噪聲容限:這是輸入端允許的噪聲電壓,不應影響輸出。TTL 的噪聲容限為 0.4 V。

傳播延遲:指電路從施加輸入到產(chǎn)生輸出所花費的時間。

功耗:設(shè)備必須的。

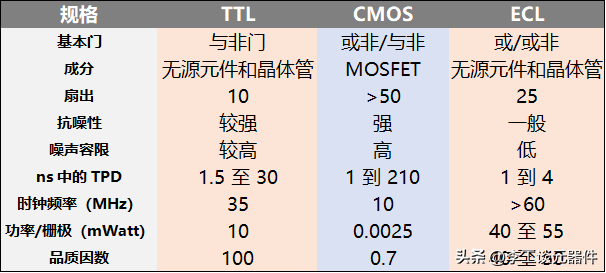

七、TTL 與其他邏輯系列的比較

下面為TTL 與其他邏輯系列的比較:

TTL 與其他邏輯系列的比較

評論