H橋電路設(shè)計(jì)實(shí)例詳細(xì),設(shè)計(jì)步驟+實(shí)際案例

一、H橋基本拓?fù)浣Y(jié)構(gòu)

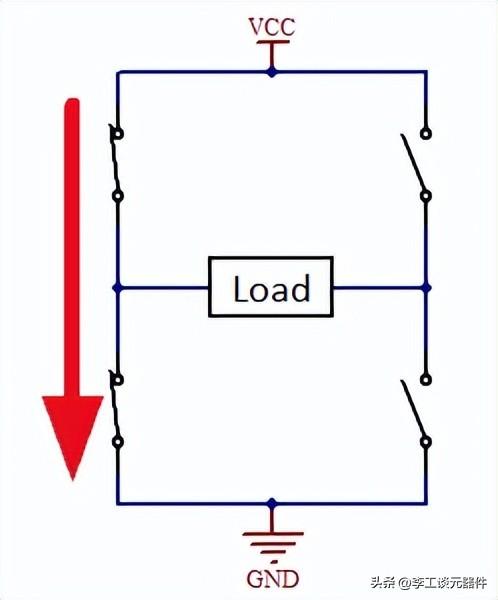

下圖顯示了H的基本拓?fù)浣Y(jié)構(gòu):

本文引用地址:http://www.104case.com/article/202405/458714.htm

H橋基本拓?fù)浣Y(jié)構(gòu)

在一般的設(shè)計(jì)中,開關(guān)通常是某種晶體管(雙極型、MOSFET、 IGBT)。開關(guān)對(duì)角閉合(左上角和右下角或者右下角和左下角)在任一方向?qū)㈦娫催B接到負(fù)載。

二、H橋需要克服的問題

H橋存在有2個(gè)問題:避免擊穿和驅(qū)動(dòng)高端晶體管。

擊穿是指左側(cè)兩個(gè)開關(guān)或右側(cè)兩個(gè)開關(guān)同時(shí)閉合的情況,這肯定會(huì)導(dǎo)致短路,這是一個(gè)壞事,可能會(huì)損壞開關(guān)或者其他組件。

下圖顯示了這里說的情況。

有2種可能發(fā)生這種情況的方式,一個(gè)是應(yīng)用了非法控制信號(hào),例如由于軟件錯(cuò)誤。

另一個(gè)是從一種極性切換到另一種極性時(shí),柵極驅(qū)動(dòng)信號(hào)中存在短暫且無意的重疊。

左側(cè)的兩個(gè)開關(guān)意外同時(shí)導(dǎo)通,導(dǎo)致大的短路電流流過

驅(qū)動(dòng)高側(cè)晶體管是相對(duì)比較難的部分,因?yàn)楦邆?cè)晶體管以相對(duì)較高的電源電壓為參考而不是以地為參考,控制信號(hào)(通常來自微控制器或類似設(shè)備)以地為參考,因此需要某種電平轉(zhuǎn)換電路。

三、設(shè)計(jì)H橋電路

主要是為了驅(qū)動(dòng)5相雙極步進(jìn)電機(jī),Iw = 0.21 A,Rw = 32 ohms,因此H橋需要能夠支持6.7V的驅(qū)動(dòng)電壓。

1、設(shè)計(jì)選擇

大約200mA的電流不是特別高,使用雙極晶體管(BJT)作為開關(guān)。對(duì)于更高的電流,必須使用具有較低電流增益的強(qiáng)大功率晶體管,就需要大量的基極電流,這樣實(shí)際上不好處理,并會(huì)導(dǎo)致大量損耗和需要消散的熱量。

這里打算在電流和電壓處理要求上留出一些余量來構(gòu)建電橋,使用MOS管來避免BJT的靜態(tài)基極電流引起的功率耗散問題。

對(duì)于給定的導(dǎo)通電阻,就元器件尺寸(成本)和柵極電容而言,NMOS管晶體管的效率大約是PMOS晶體管的3倍,因此對(duì)于高功率設(shè)計(jì),上下開關(guān)都使用NMOS晶體管是有利的。

但是將NMOS管用于上部開關(guān)有一個(gè)問題:NMOS管需要高于橋電源電壓的柵極電壓。如果使用PMOS管,低于電源電壓的柵極電壓是足夠的。為了避免額外的電源電壓,并且由于電流相當(dāng)?shù)停虼撕线m的PMOS管的成本不高。

最后我決定使用PMOS管作為頂部開關(guān),NMOS管作為底部開關(guān)。

2、H橋驅(qū)動(dòng)電路信號(hào)生成

這里為了避免設(shè)計(jì)安全,即使微控制器代碼中的錯(cuò)誤就永遠(yuǎn)不會(huì)導(dǎo)致嚴(yán)重情況發(fā)生。因此需要注意以下2件事情:

1、使用一些邏輯門用于控制信號(hào)(啟動(dòng)/方向)轉(zhuǎn)換為打開左上/右上或者右上/左下的內(nèi)部信號(hào),

2、為了避免在方向信號(hào)變化期間發(fā)生短暫的直通,最好在晶體管的導(dǎo)通信號(hào)中引入延遲,而且讓關(guān)斷信號(hào)盡快通過,因此引入一個(gè)短暫的時(shí)期,在極性切換期間沒有晶體管導(dǎo)通。

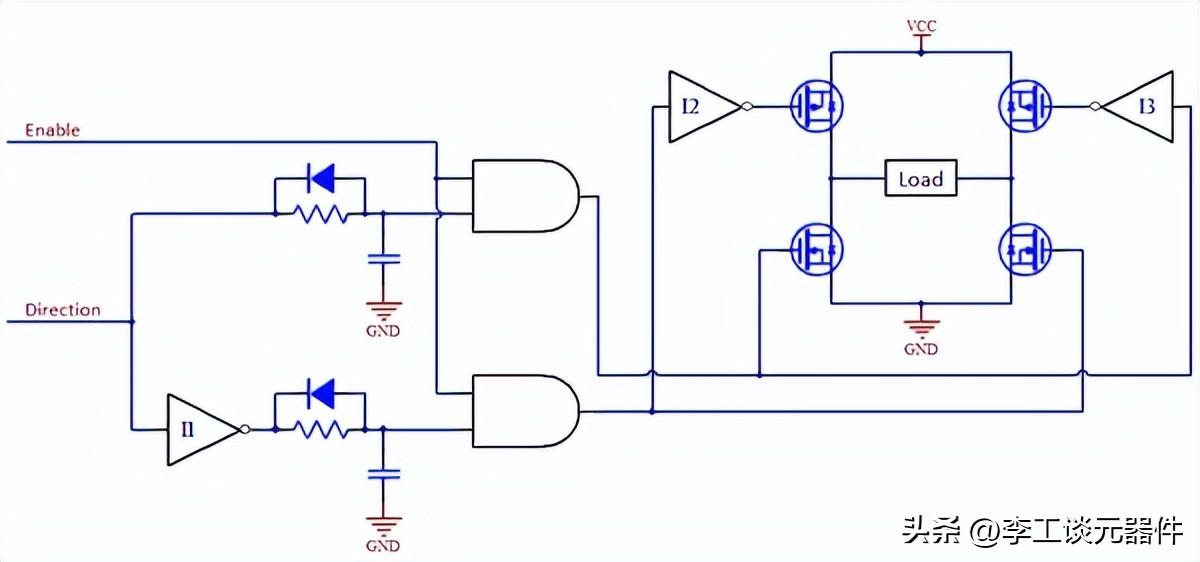

下圖顯示了一種概念性解決方案,實(shí)現(xiàn)了啟用/方向控制信號(hào)和柵極信號(hào)之間的切換,并在晶體管即將導(dǎo)通時(shí)引入了延遲。

H橋的柵極驅(qū)動(dòng)信號(hào)如何生成的電路圖

H橋的柵極驅(qū)動(dòng)信號(hào)生成原理

兩個(gè)ADN 門允許使能信號(hào)斷開控制信號(hào)與MOS管柵極的連接,二極管/電阻組合使電容的充電速度比放電速度慢,因此當(dāng)晶體管即將導(dǎo)通時(shí),柵極驅(qū)動(dòng)信號(hào)到達(dá)晶體管所需的時(shí)間比晶體管即將截止的時(shí)間更長(zhǎng)。

通過讓來自與門的柵極控制信號(hào)對(duì)角地控制晶體管,來自與門之一的電平變化打開或者由門控制的兩個(gè)晶體管。僅使用2個(gè)延遲電路就可以控制4個(gè)晶體管的時(shí)序。

反相器I2和I3需要將與門的邏輯電平轉(zhuǎn)換為適合驅(qū)動(dòng)晶體管的電壓。

四、詳細(xì)設(shè)計(jì)

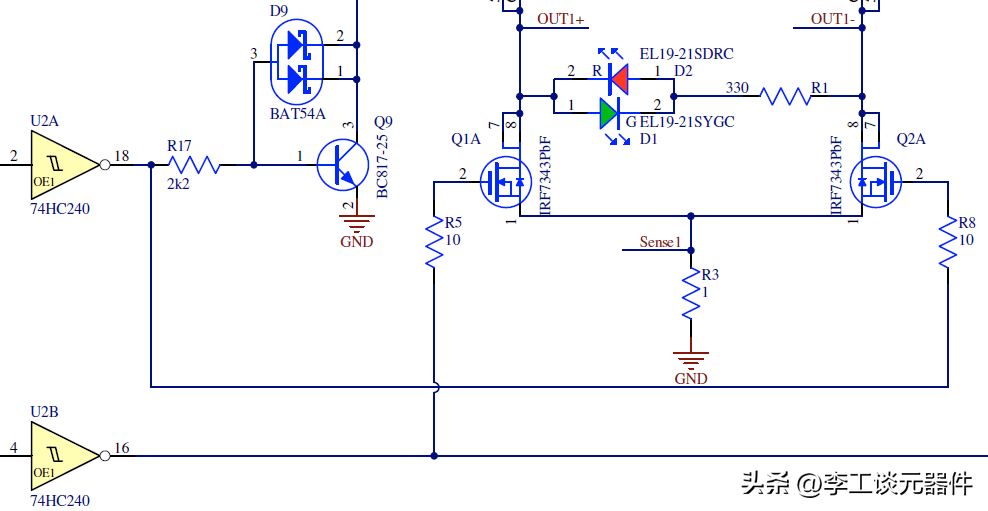

1、設(shè)計(jì)原理圖(評(píng)論區(qū)留言或者私聊獲取PDF文檔)

完整的(雙)H橋的示意圖

2、邏輯門的選擇

下圖的與門需要有施密特觸發(fā)器輸入,因此與門是由相對(duì)緩慢變化的電壓驅(qū)動(dòng)的。使用或非門會(huì)使使能信號(hào)處于低電平狀態(tài),但這并不是缺點(diǎn)。使用或非門的一個(gè)優(yōu)點(diǎn)是反相器 I1 可以通過或非門實(shí)現(xiàn)。然后單個(gè)邏輯IC就可以滿足H橋的要求。

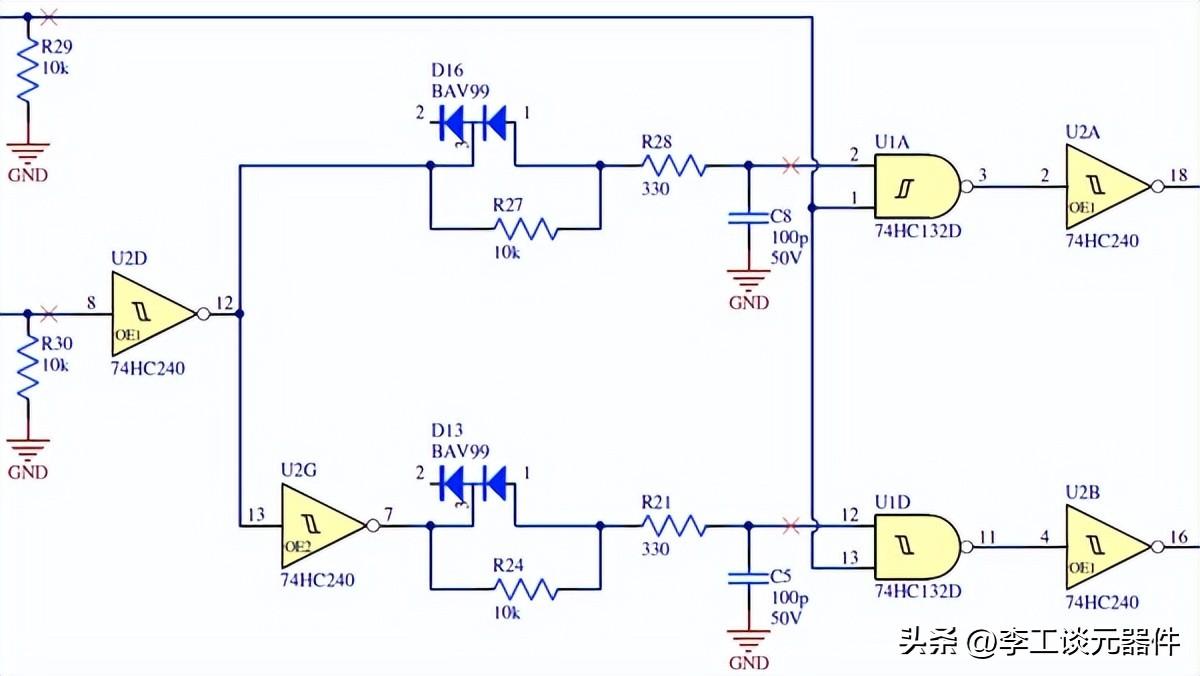

這里需要使用2個(gè)用于H橋的邏輯IC來提供所需的NAND門和4個(gè)反相器。'240 系列邏輯電路中有八進(jìn)制反相器可用,連同'32 四路與非門,有足夠的門用于兩個(gè)橋。所以最后還是在同一塊板上構(gòu)造了2座H橋。下圖顯示了最終的設(shè)計(jì)。

邏輯門和不對(duì)稱時(shí)序電路的示意圖

可以使用幾個(gè)不同的邏輯系列,因?yàn)槲蚁胍哂蠧MOS輸入電平的NAND門,這也意味著施密特觸發(fā)器輸入將以電源電壓的一半進(jìn)行切換,同時(shí)我還希望反相器具有CMOS輸出用來驅(qū)動(dòng)NFET高達(dá)5V。

因此NAND門可以是 HC或者AC系列,而反相器可以是HC、HCT、或者AC等。

最后 2個(gè)地方都是使用的HC,將HCT用于反相器用來適應(yīng)方向信號(hào)上的TTL電平并不好,因?yàn)閱⒂眯盘?hào)無論如何都必須有CMOS電平。

3、其他輸入級(jí)選擇

這里我在輸入信號(hào)上放置了下拉電路,將它們保持在有效且安全的邏輯電平,防止某些輸入有時(shí)沒有連接。CMOS輸入具有非常高的阻抗,不然很容易拾取噪聲。

為了限制電容充電時(shí)的電流浪涌,在二極管/電阻對(duì)桑串聯(lián)了一個(gè)額外的330Ω電阻,另一個(gè)電容和電阻的值先手工計(jì)算大致計(jì)算確定,然后進(jìn)行模擬,在電路完成后進(jìn)行微調(diào),保證沒有擊穿。

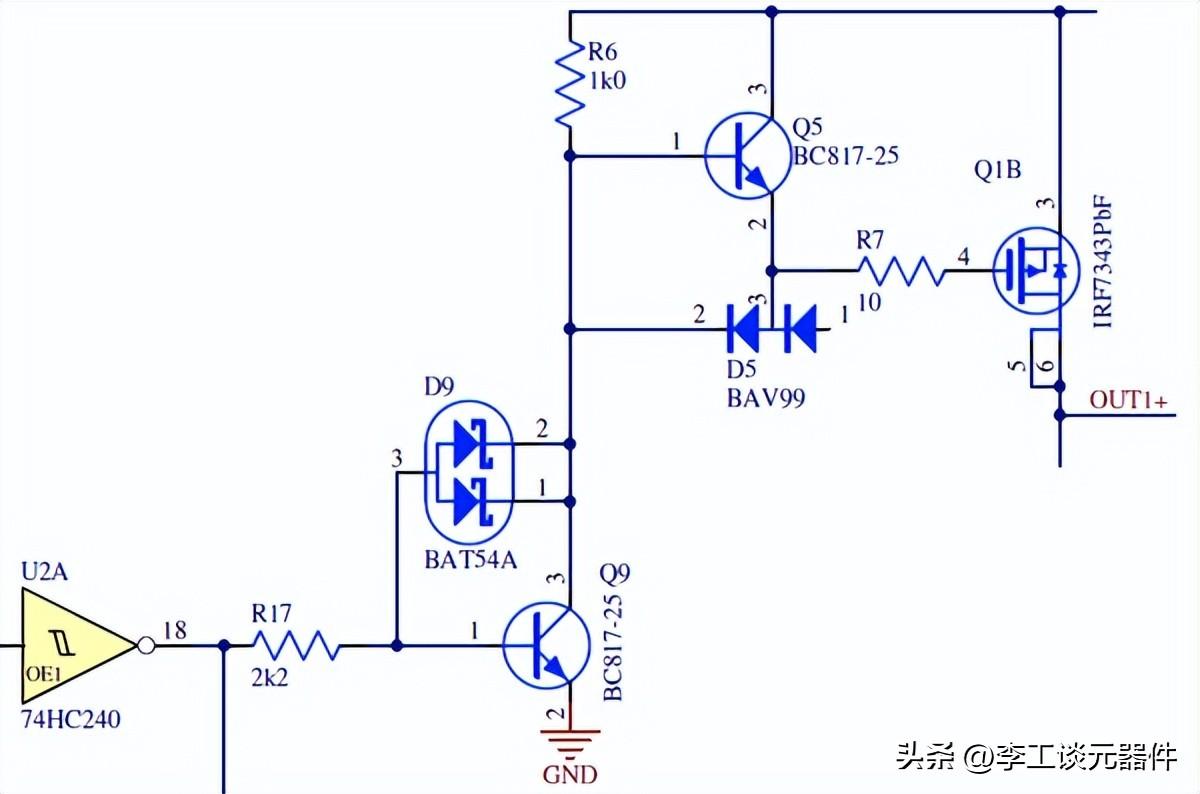

4、高側(cè)驅(qū)動(dòng)器

高側(cè)PMOS晶體管的驅(qū)動(dòng)電路需要反轉(zhuǎn)信號(hào)并增加電機(jī)電源電壓的擺幅,該電壓至少為7V,必須能夠相對(duì)地對(duì)FET的柵極電容進(jìn)行充電和放電。當(dāng)較低的NMOS管快速拉動(dòng)漏極電壓時(shí),即使寄生柵極電容將其拉低,PFET也會(huì)保持關(guān)閉狀態(tài)向下。

高側(cè)驅(qū)動(dòng)器

上圖顯示了完整的驅(qū)動(dòng)電路。反轉(zhuǎn)和電平移位由NPN晶體管Q9處理。該晶體管的關(guān)閉速度非常慢。因?yàn)槿绻麤]有從基極到集電極的肖特基二極管防止飽和,就會(huì)處于飽和狀態(tài)。這和LSTTL邏輯內(nèi)部用于加速切換的技術(shù)相同。

Q5作射極跟隨器連接。并在PMOS晶體管關(guān)閉時(shí)向電源軌提供所需的低組狼。僅依靠R6將柵極拉高會(huì)顯著拉高晶體管關(guān)閉的時(shí)間,但是這里更重要的是。當(dāng)快速發(fā)生變化時(shí),電阻無法將柵極保持在高電平。

由于較低的 NMOS 導(dǎo)通,PMOS 晶體管的漏極處出現(xiàn)壓降(大的負(fù) dV/dt)。 當(dāng) PMOS 導(dǎo)通時(shí),二極管 D5 提供將柵極拉低的路徑。這里使用 PNP 射極跟隨器來稍微加快開啟速度。

小柵極電阻 R7 可限制柵極電流浪涌并降低柵極電路中出現(xiàn)振鈴的風(fēng)險(xiǎn)。

5、電路其余部分

這里顯示了電橋電路的其他部分

其他電路

驅(qū)動(dòng)NMOS管要簡(jiǎn)單一點(diǎn),將普通的柵極電阻(R8)連接在反相器的輸出和柵極之間就可以。

這里在NMOS管的源極引線中添加了一個(gè)電流檢測(cè)電阻。方便測(cè)量電流并且驗(yàn)證是否發(fā)生擊穿。選擇1Ω作為獲得示波器測(cè)量的合適電壓和最小化損耗之間的折中方案。

在0.2 A 電流下,我們得到 0.2 V 壓降,與 6 或 7 V 電源電壓相比,這相對(duì)較小。測(cè)試完成后,可以用 0 Ω電阻替換 1 歐姆電阻。

對(duì)于 MOSFET,選擇了 IRF7343,是采用單個(gè) SO8 封裝的 NMOS/PMOS 組合,是價(jià)格、可用性和導(dǎo)通電阻的綜合選擇。

這里還在H橋輸出上添加了LED,可以直觀地指示電路的狀態(tài)。但是對(duì)于成品來說,最好不要使用LED。

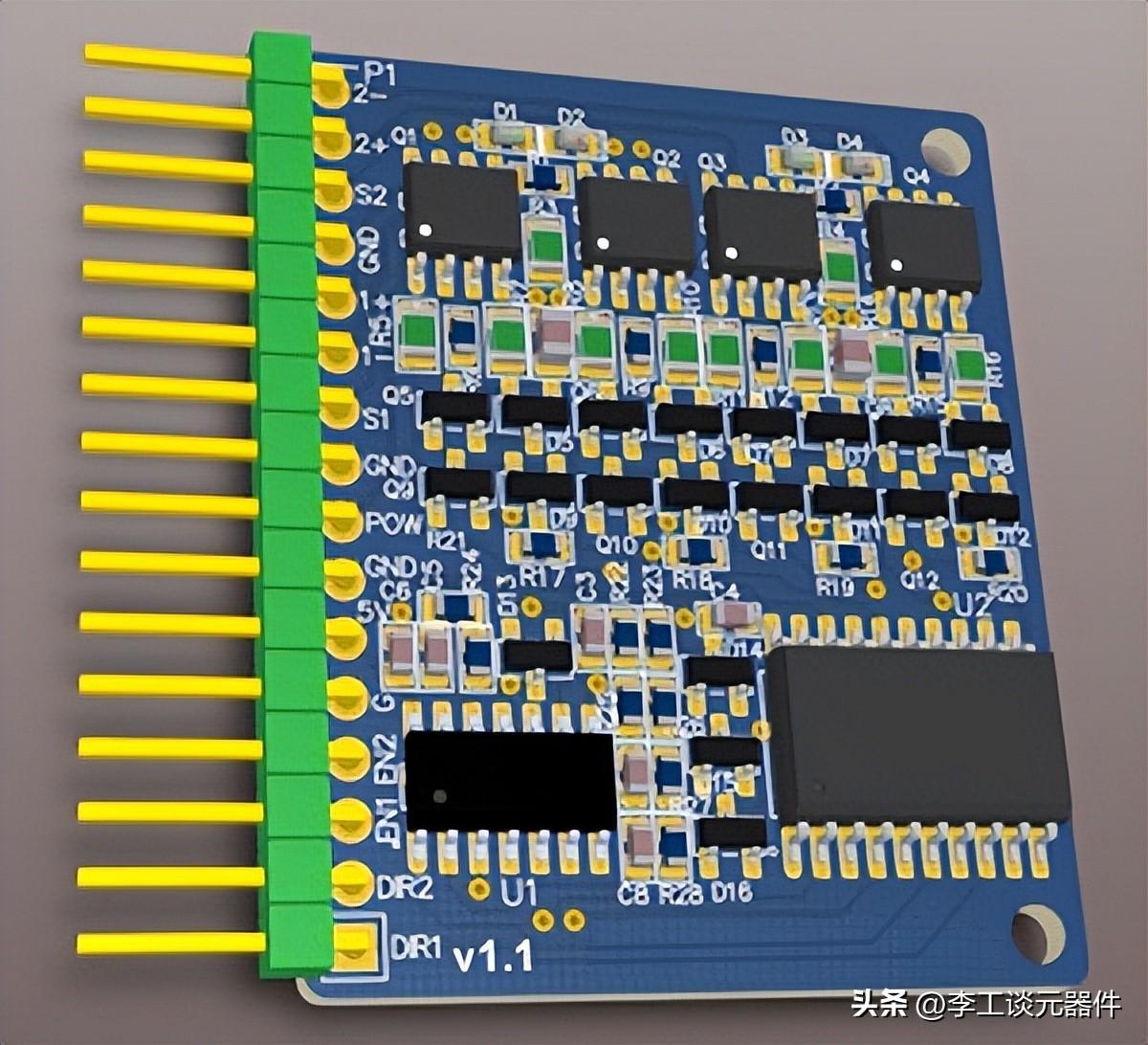

五、H橋電路PCB設(shè)計(jì)成品圖

最后決定將雙H橋電路放在雙面PCB上,將所有外部信號(hào)拉到單排排針,而不是設(shè)計(jì)一個(gè)包含H橋、微控制器、電源等完整的PCB,這樣可以最大程度低減少工作量,從而完成項(xiàng)目的H橋部分。如果有必要的化,可以始終將H橋與電路板上的其他電路集成在一起。

下面為最終的成品圖。

H橋電路PCB設(shè)計(jì)成品圖

評(píng)論