D型觸發器的電路和操作

D型觸發器是基本的數字存儲器元件。在這里,我們檢查它們的輸入輸出行為和內部電路。

本文引用地址:http://www.104case.com/article/202404/457625.htm邏輯門是所有數字技術的組成部分。然而,只有組合邏輯電路是不可能實現現代世界龐大的計算功能的。在完全由組合邏輯組成的電路中,輸出僅取決于輸入的當前狀態。所有信號通過互連的邏輯門直接從輸入移動到輸出。

為了實現我們與當今數字技術相關的先進計算和信號處理,我們需要組合邏輯和數字存儲器。換句話說,我們需要時序邏輯。雖然組合邏輯允許我們構建有用的設備,如加法器、多路復用器和編碼器,但正是時序邏輯讓我們進入微處理器領域。

在時序邏輯電路中,輸出取決于輸入信號的序列——包括當前狀態和歷史。這允許創建具有存儲器的數字設備,例如鎖存器和觸發器。然而,盡管這兩種電路類型都起到數字存儲設備的作用,但它們之間有一個重要的區別:

鎖存器是電平觸發的,這意味著當“使能”輸入處于活動狀態時(例如,在時鐘信號的邏輯高脈沖期間),它會對輸入信號做出響應。

觸發器是邊緣觸發的,這意味著當“使能”輸入改變狀態時,它對輸入信號做出響應——例如,在時鐘信號的上升沿。

在實際應用中,通常更希望有一個只在特定事件發生時對輸入狀態敏感的存儲設備。因此,觸發器的應用要廣泛得多。

在我看來,D型觸發器是最重要的觸發器——我甚至稱之為最重要的數字存儲器子電路。在這篇文章中,我們將了解它的電學行為和內部結構。

什么是D型觸發器?

D型觸發器以其單個數據輸入而命名,它正是做存儲器單元需要做的事情——它在控制信號的有效轉換時刻將輸入邏輯電平存儲為輸出電壓,而在所有其他時間只保留輸出電壓。

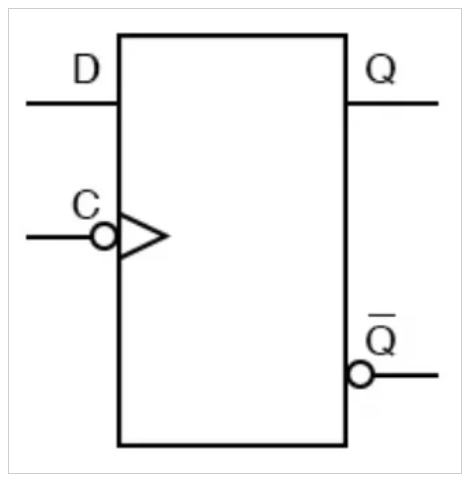

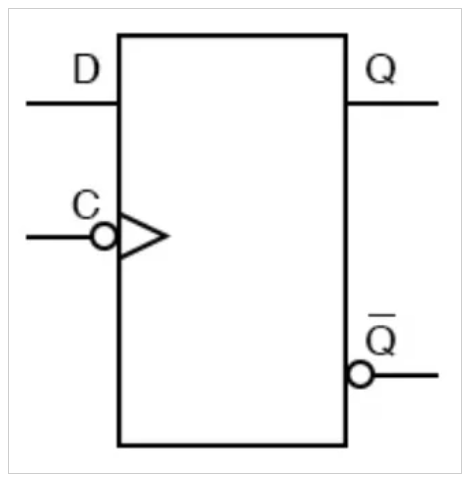

圖1顯示了一個基本的D型觸發器。如您所見,它有四個終端:

數據輸入(D)。

時鐘或控制輸入(C)。

一個輸出(Q)。

輸出的反相版本(Q?)。

基本D型觸發器的電路符號。

圖1。基本D型觸發器的電路符號。端子是數據輸入端(D)、時鐘或控制輸入端(C)、輸出端(Q)和輸出端的反相版本(Q?)。圖片由Tony R.Kuphaldt提供

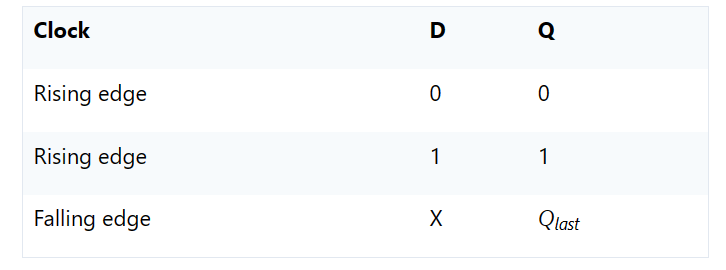

表1描述了響應時鐘信號的上升沿的D型觸發器的操作。

表1。D型觸發器的真值表。

下降沿行中的X表示D的邏輯電平無關。Q僅受上升沿處的輸入狀態的影響。在時鐘信號的上升沿,對數據輸入進行采樣并將其傳遞到Q輸出。通過查看圖2中的時序圖,我們可以在時域中看到這一點。

D型觸發器的時序圖。

圖2:D型觸發器的時序圖。圖片(經修改)由Tony R.Kuphaldt提供

由同一時鐘信號的上升沿或下降沿控制的八個D型觸發器可以用作一字節(8位)寄存器。當與解碼電路相結合時,一個字節寄存器的集合起到存儲器組的作用。

為了理解D型觸發器的內部邏輯門結構,讓我們檢查以下功能塊:

D鎖存器。

脈沖檢測器。

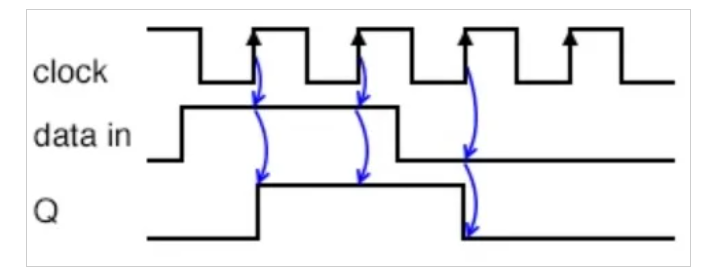

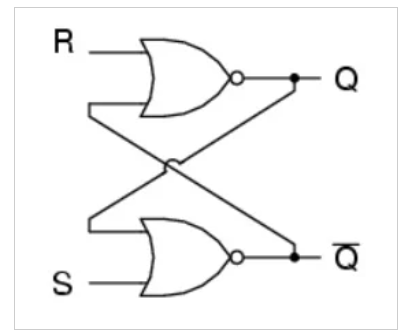

置位-復位(S-R)鎖存器是時序邏輯的基礎子電路。這種通過反饋實現存儲器的鎖存器可以由NOR門或NAND門構建。圖3顯示了實現為兩個交叉耦合NOR門的S-R鎖存器。

使用兩個NOR門實現的S-R鎖存器。

圖3。S-R鎖存器實現為兩個交叉耦合的NOR門。圖片由Tony R.Kuphaldt提供

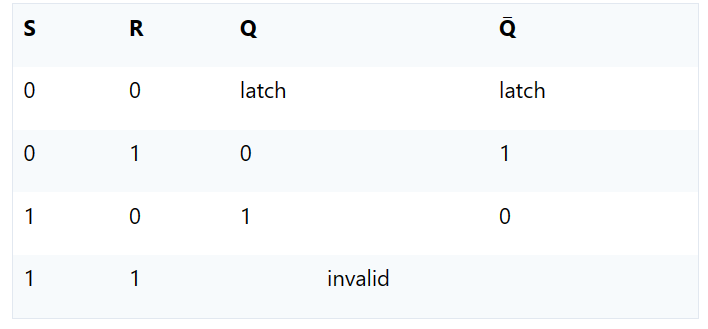

將輸出信號反饋到輸入端子允許S-R鎖存器保持先前的輸出狀態。下面的真值表指定了鎖存器的輸入輸出行為。

表2。S-R鎖存真值表。

要理解這種行為,請考慮以下事件序列:

首先,假設s為高,R為低。因此Q將是高的。

現在將S驅動至邏輯低。兩個輸入現在都是低電平,而Q仍然是高電平——它被“鎖存”,這意味著它保留了以前的狀態。

現在將R驅動至邏輯高電平。在R邏輯為高且S邏輯為低的情況下,Q將為低。

現在將R驅動至邏輯低。再一次,兩個輸入都是低的,但這次Q是低的。

相同的輸入組合在步驟4中產生與在步驟2中不同的輸出狀態。這是因為電路同時受到當前輸入狀態和先前輸出狀態的影響。

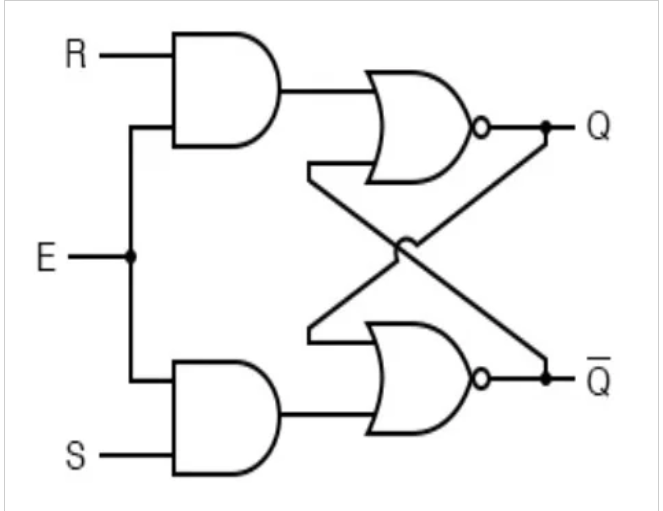

為了使S-R鎖存器更有用,我們需要額外的電路,使我們能夠確定鎖存器何時會或不會對其輸入狀態做出響應。圖4顯示了一個“門控”S-R鎖存器,即具有啟用/禁用信號的S-R鎖閂器。控制信號標記為E,表示“啟用”

門控S-R鎖存器。

圖4。門控S-R鎖存器。圖片由Tony R.Kuphaldt提供

有了這個附加,我們現在有了一個電平觸發的鎖存器——當E為低時,鎖存器的作用就好像S和R為低一樣。換言之,E上的邏輯低將鎖存器置于其保持先前輸出模式,而與S和R輸入的真實狀態無關。

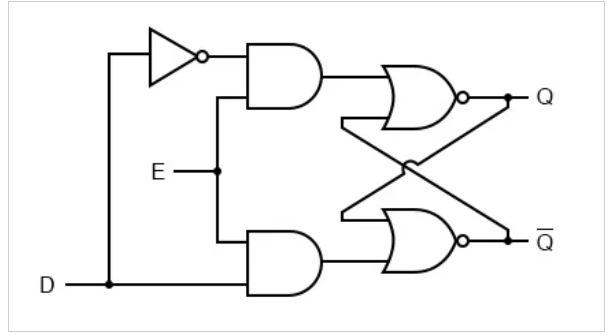

從技術上講,我們不需要同時使用設置和重置輸入來存儲單個內存。簡單地存儲一個輸入信號的邏輯電平的存儲器單元具有更直觀的意義。這就是為什么我們有D鎖存器(圖5)。

一個D鎖存器。

圖5。一個D鎖存器。圖片由Tony R.Kuphaldt提供

如圖所示,D鎖存器簡單地是門控S-R鎖存器,其中S輸入被重命名為D,并且R輸入總是D的倒數。這種布置使得S=R=1(無效)狀態和S=R=0(鎖存器)狀態不可能。如表3所示,Q跟隨D,并且鎖存模式僅通過E信號實現。

表3。D鎖存器的真值表。

脈沖檢測器

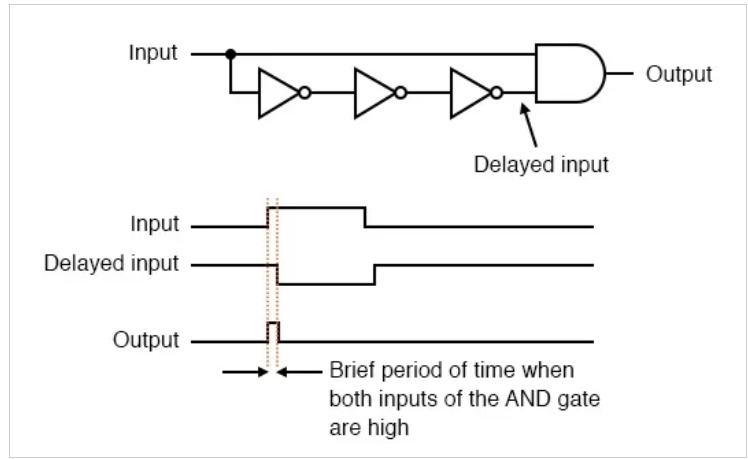

為了將電平觸發的D鎖存器轉換為邊緣觸發的D型觸發器,我們需要一個脈沖檢測器——一種將寬脈沖轉換為與脈沖的上升沿或下降沿對齊的非常窄的脈沖的電路。圖6中的圖表描述了一種實現脈沖檢測器的方法。這里,多個串聯的反相器會產生短延遲。AND門使用主輸入和延遲輸入來創建窄脈沖。

使用串聯的多個逆變器構建的脈沖檢測器。

圖6。使用串聯的多個逆變器構建的脈沖檢測器。圖片由Tony R.Kuphaldt提供

如果我們在將D鎖存器的E信號饋送到AND門之前將其通過脈沖檢測器,那么我們將有一個D型觸發器,它的作用就好像它只在E信號的上升沿或下降沿時刻對輸入做出響應一樣。實際上,觸發器仍然是電平觸發的,但現在感興趣的電平是脈沖檢測器輸出的激活狀態。這種活躍狀態總是非常短暫的。

總結

D型觸發器是最先進的數字技術的重要組成部分。在我們結束之前,我應該指出,上面描述的結構并不是創建一個結構的唯一方法。例如,上升沿觸發的D型觸發器可以由連接在一起的三個S-R鎖存器制成。無論哪種方式,電路在設計和操作上都保持相當簡單。

評論