釋放開源評估平臺的潛力,制作超聲發射子系統的原型

摘要

本文引用地址:http://www.104case.com/article/202311/453343.htm本文討論了開發先進超聲設備所面臨的挑戰。利用現有評估平臺既可降低系統開發成本,也可縮短超聲系統發射模塊的特性測試時間。本文介紹了如何同步多個通道的分步過程,這是波束控制的一個關鍵概念,也是醫學成像所特有的概念。

引言

在任何新技術開發過程中,在將新型號或下一代超聲設備商業化之前,制造商都會經歷硬件開發和測試以及系統集成和驗證等階段。開發高通道數成像超聲子系統預計需要多年的努力。此外,在對系統考慮因素知之甚少的情況下貿然開始波束引導或發射子系統的硬件原型制作,可能會導致硬件原型需要多次修改,帶來高昂的成本。現在,開發人員可以使用一個完整系統(原型板和開源軟件)來模擬超聲設備子系統的操作,從而降低超聲設備制造商的開發成本并加快上市時間。

基于Arduino的TxDAC?評估板和開源Mbed軟件

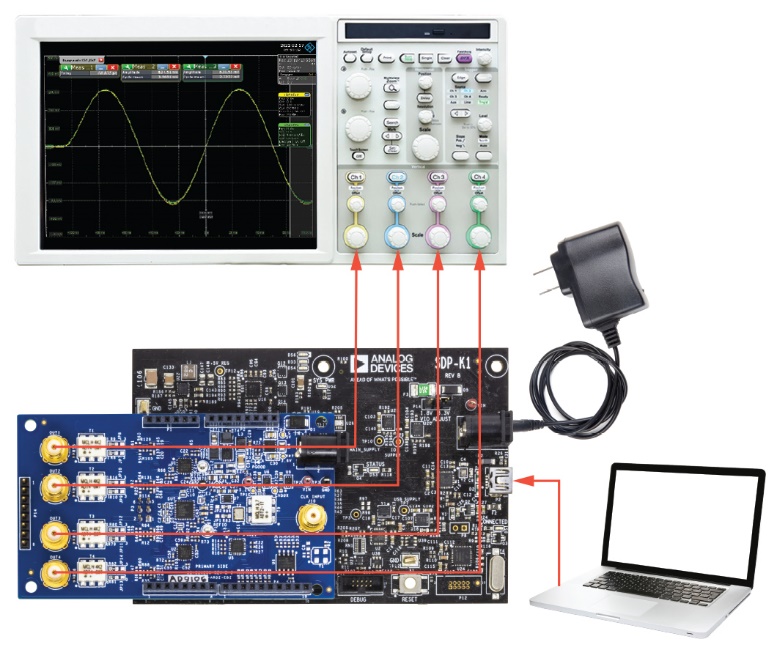

圖1.支持Mbed的AD9106評估平臺。

AD9106-ARDZ-EBZ評估平臺兼容基于Arm?且支持Mbed的電路板(如SDP-K1),并且可以連接到Arduino Uno接頭。該評估設置只能由USB供電,無需高頻波形發生器來提供時鐘輸入。該評估板默認使用板載156.25 MHz晶振作為時鐘源,但提供了外部時鐘選項。DAC輸出可以通過變壓器耦合,或使用板載放大器進行評估,這是唯一需要7 VDC至12 VDC 30 W AC-DC適配器的情況。參見圖1。

除硬件之外,評估板網頁上還提供了示例開源代碼,可用作開發目標應用固件的起點。評估板和示例源代碼可以根據需要加以定制,以便與其他Mbed平臺配合使用。新的評估系統可以輕松集成到現有系統中,因而簡化了原型制作。

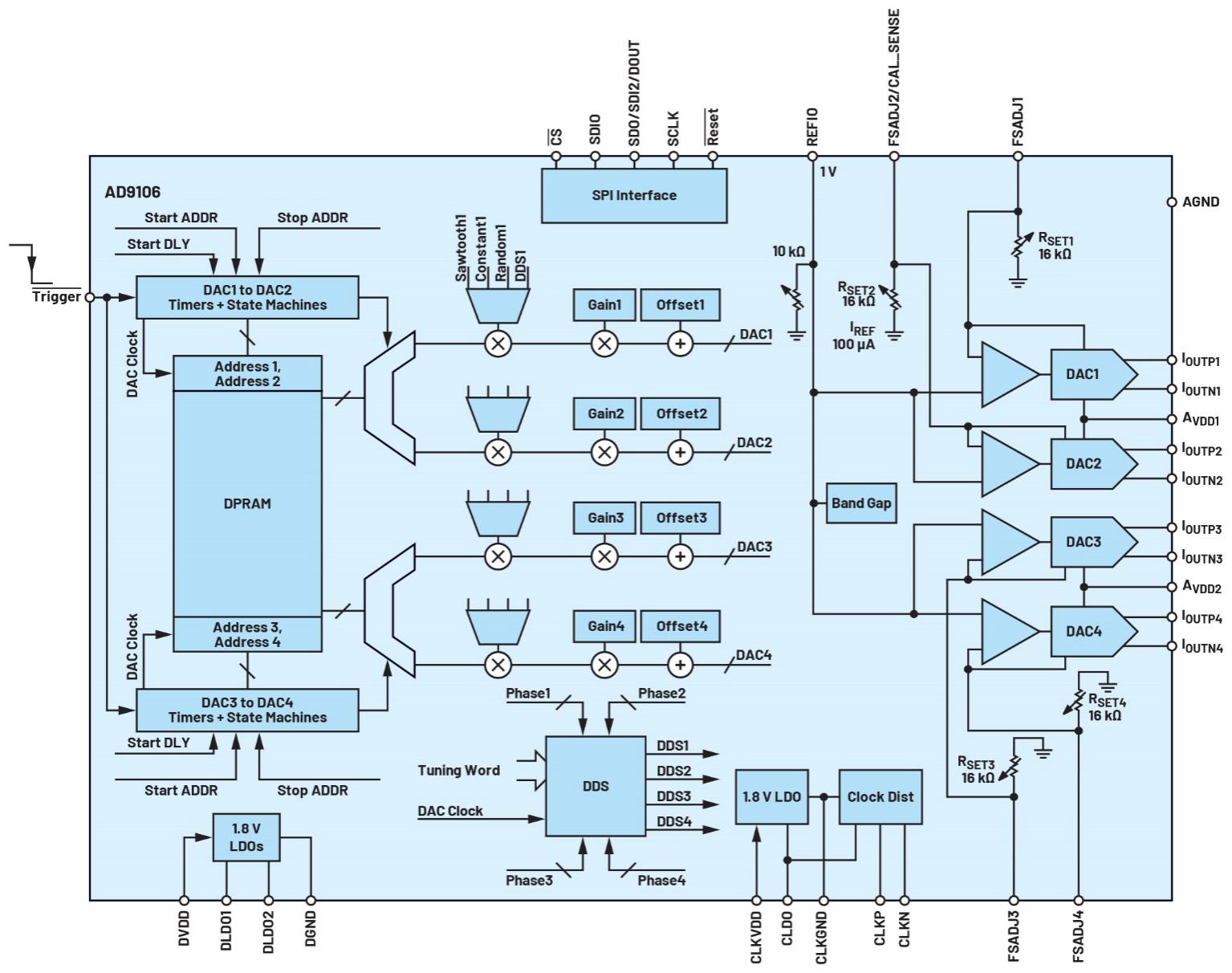

圖2.AD9106功能框圖。

評估板安裝有四通道、低功耗、12位、180 MSPS、TxDAC AD9106和波形發生器。該DAC的高采樣速率非常適合1 MHz至40 MHz范圍內的超聲工作頻率,外部成像設備通常使用1 MHz至15 MHz的頻率,而靜脈內心血管設備使用高達40 MHz的頻率。此外,AD9106高度集成,具有用于生成復雜波形的片內模式存儲器,以及使用24位調諧字、支持10.8 Hz/LSB頻率分辨率的直接數字頻率合成器(DDS)。該器件也是高度可編程的,四個DAC通道中的每個通道的模式周期、啟動延遲、增益和偏移都可以獨立改變。此外,它具有低功耗特性(在3.3 V、4 mA輸出和180 MSPS下,每通道功耗78.8 mW,總計315.25 mW),這是超聲設備等大型多通道系統的一個重要考慮因素。

提高超聲設備的精度和圖像分辨率

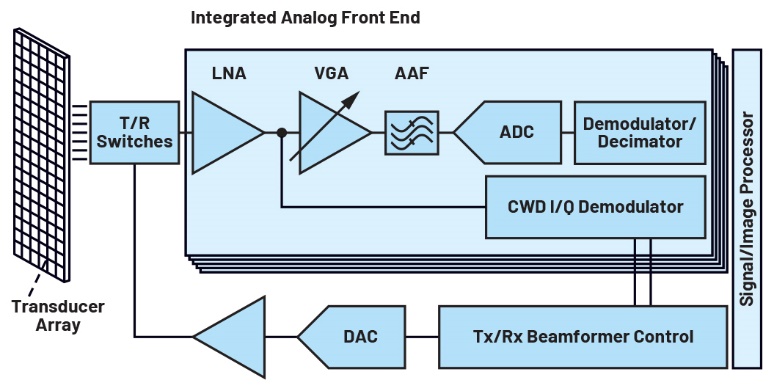

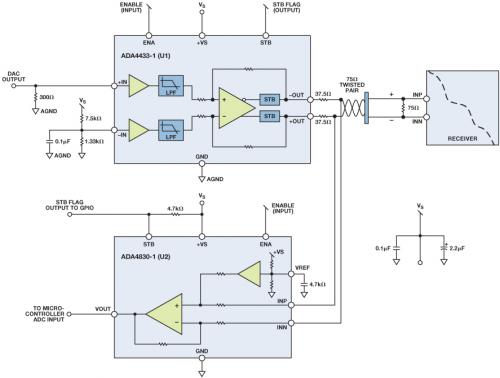

圖3.醫療超聲前端信號鏈。

推車式超聲系統在圖像質量或分辨率方面優于手持設備,主要是因為通道數量差異巨大。然而,通道數量可能因制造商而異。成本和功耗是超聲設備等大型系統的重要考慮因素,因此業界使用了一些技術來盡量減小這兩個因素。在圖3所示的典型超聲信號鏈中,如果我們考慮到每個發射器路徑(DAC + 高壓放大器,驅動探頭尖端處換能器陣列中的一個元件)都對應一個接收器路徑(集成模擬前端),那么通道數的確定相對簡單。根據這個假設,我們可以說超聲系統中的通道數介于16到256之間。高端系統(其中大部分推車式)中的通道數為64或更多。對于便攜式、中低端系統,16至64個通道更為常見。

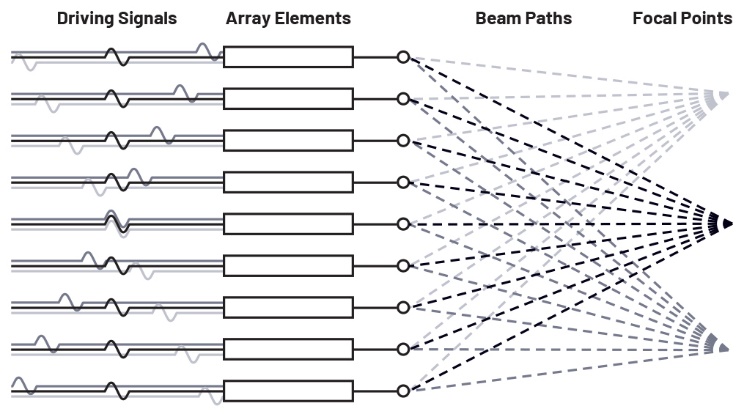

圖4.波束引導和聚焦。

在超聲系統的發射器路徑中,聲能或聲波束掃過身體。聲波由探頭前端處的壓電換能器元件從電信號轉換而來。如圖4所示,每個電信號或發射器信號的相位和幅度均經過編程,引導入射能量束沿著一條線進入身體。從器官組織反射的聲波被換能器元件再次轉換為電能。目標的位置或距離將根據換能器陣列中元件之間的時間延遲顯示在屏幕上。因此,為了顯示人體內部的準確圖像,同步或者說能夠控制發射器信號之間的延遲至關重要。

多芯片同步的要求

為了成功同步多個DDS DAC(如AD9106),必須控制差分時鐘輸入(CLKP和CLKN)和TRIGGER引腳的下降沿。

圖5.建議時鐘分配布局(左)和次優布局(右)。

為了滿足同步的第一個要求,PCB布局應采用謹慎的時鐘分配做法。參見圖5。這將充分減少REF CLK邊沿之間的相位差(它會導致DDS輸出處出現成比例的相位差)。

模式生成由AD9106的TRIGGER引腳的下降沿觸發,因此同步的下一個要求是確保TRIGGER邊沿一致。圖5中的布局技術也可應用于從控制器的數字輸出布線到每個AD9106器件的TRIGGER PCB走線。

利用AD9106-ARDZ-EBZ評估多芯片同步

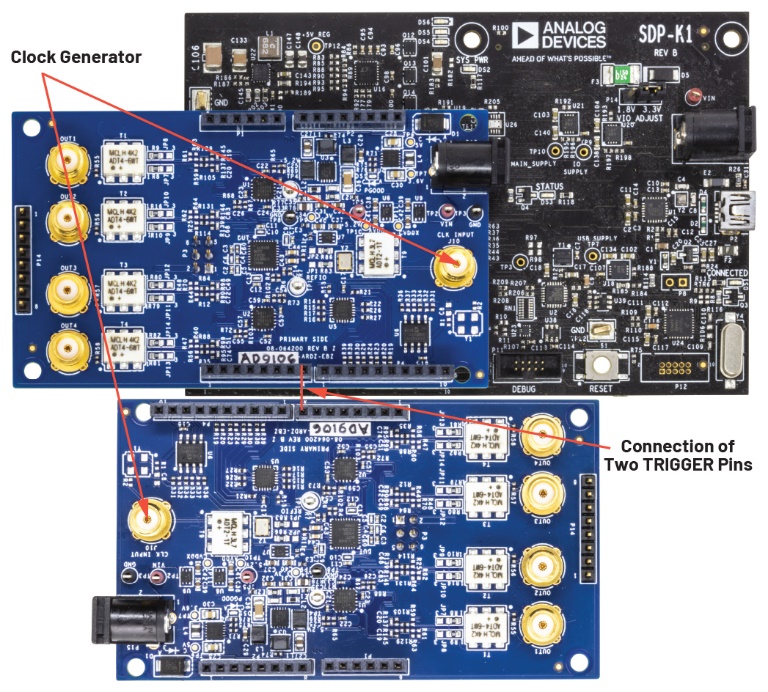

為了評估多個AD9106 DAC的同步,可以使用兩個AD9106評估板和一個SDP-K1控制器板。

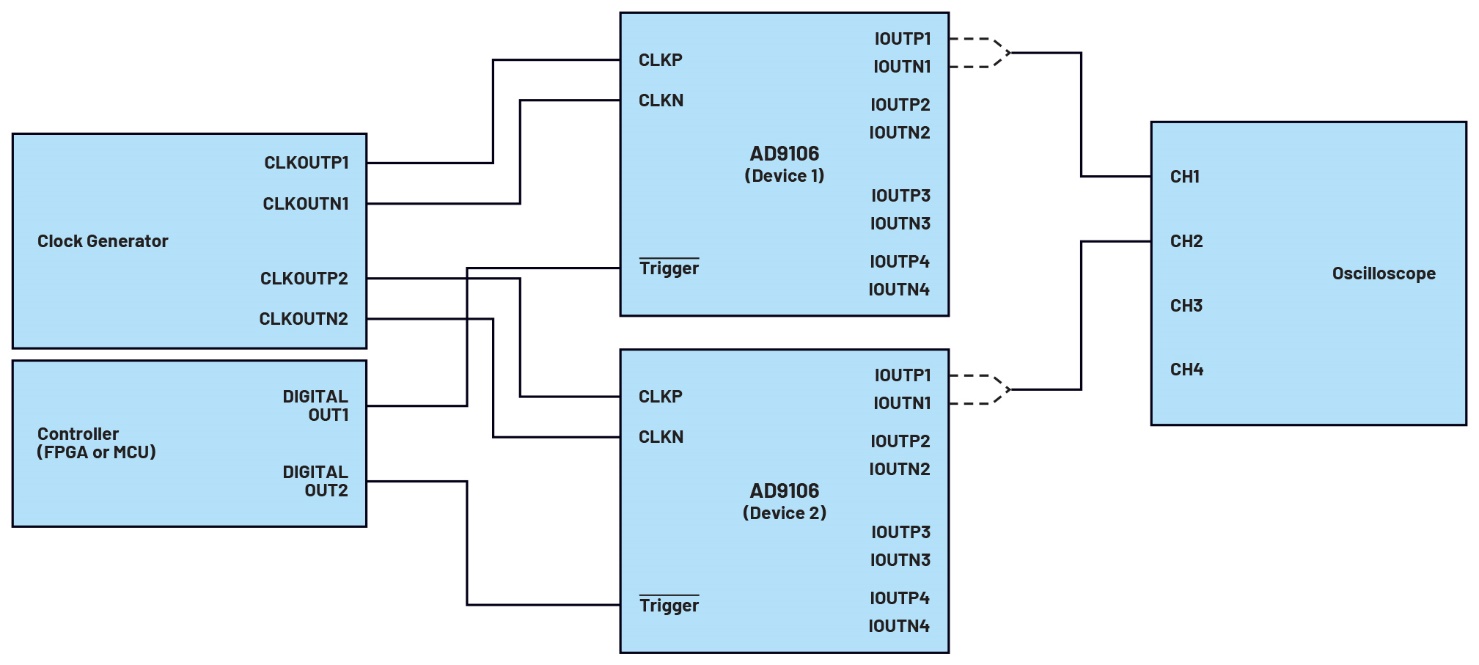

圖6.多個AD9106器件同步的系統示意圖(簡化示意圖,未顯示所有連接)。

材料

兩個AD9106-ARDZ-EBZ板

用于電路板與PC連接的USB電纜

SDP-K1

一個12 V壁式電源適配器

信號發生器

可變長度SMA端接電纜

一個SMA端接T型分路器

母對母Arduino連接器導線

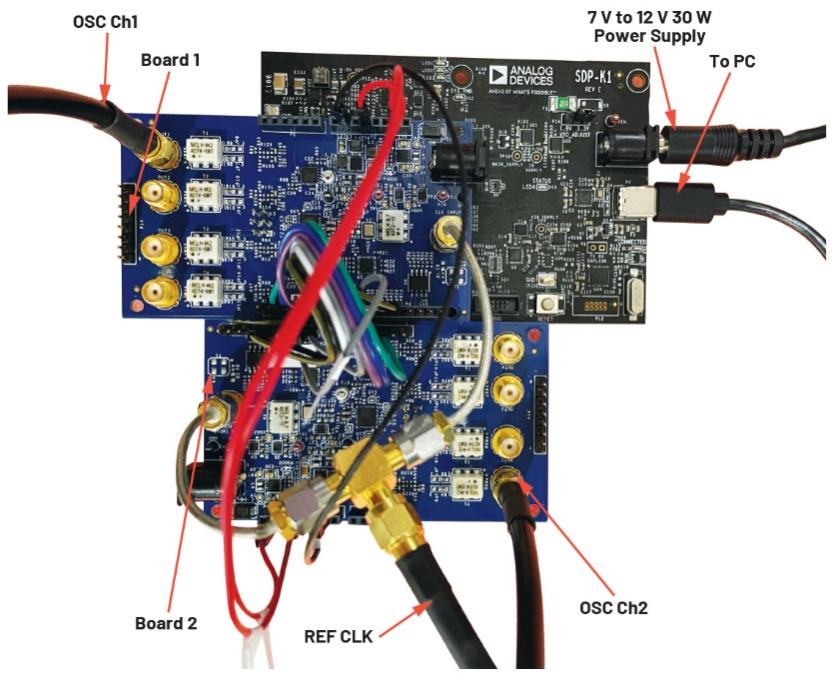

硬件設置

連接三個電路板之前,配置兩個AD9106-ARDZ-EBZ板,使DAC輸出連接到板載放大器,并且DAC時鐘由連接到J10的外部源提供。關于JP1和JP2的正確連接,請參閱Eval-AD9106 Wiki用戶指南中的圖14b。另外,請設置其中一個AD9106-ARDZ-EBZ板,使板上器件的CSB引腳連接到交替GPIO引腳(安裝R39而不是R38)。確保SDP-K1的VIO_ADJUST設置為3.3 V。

然后將高頻波形發生器的輸出連接到分離式SMA端接T形分路器,它可以連接不同長度的SMA端接同軸電纜。

圖7.為實現同步而建議采用的時鐘輸入和TRIGGER引腳連接。

接下來應設置圖7所示每個板的時鐘輸入和TRIGGER引腳的連接,然后設置表1中的其余連接。將板1安裝到SDP-K1 Arduino Uno端口,然后將板2放置在與板1成180°的位置,以使兩個板的TRIGGER引腳并排放置。這是TRIG2到SDP-K1數字輸出的最短連接,由此TRIG1和TRIG2路徑大致相等。

圖8.實際設置。

應用了所有連接的實際設置如圖8所示。表1總結了板對板連接。

表1.SDP-K1和兩個AD9106-ARDZ-EBZ板的板對板連接

| SDP-K1 Arduino Uno Connectors SDP-K1 Arduino Uno連接器 | Connected Nets on AD9106-ARDZ-EBZ AD9106-ARDZ-EBZ上的相連網絡 | ||

| Pin No. 引腳編號 | Pin Functions 引腳功能 | Board 1 板1 | Board 2 板2 |

| P2.1 P2.1 | NC NC | ||

| P2.2 P2.2 | IO_PWR_SUPPLY IO_PWR_SUPPLY | IOREF IOREF | IOREF IOREF |

| P2.3 P2.3 | MAIN_RESET MAIN_RESET | RESET RESET | RESET RESET |

| P2.4 P2.4 | SDRAM_&_ARDUINO_ PWR_SUPPLY (3.3 V) SDRAM_&_ARDUINO_ PWR_SUPPLY (3.3 V) | 3.3 V 3.3 V | 3.3 V 3.3 V |

| P2.5 P2.5 | +5V_CON +5V_CON | 5 V 5 V | 5 V 5 V |

| P2.6 P2.6 | GND GND | GND GND | GND GND |

| P2.7 P2.7 | GND GND | GND GND | GND GND |

| P5.1 P5.1 | ARDUINO_GPIOO/RX ARDUINO_GPIOO/RX | VIN VIN | VIN VIN |

| P5.2 P5.2 | TX + 1 TX + 1 | ||

| P5.3 P5.3 | GPIO2 GPIO2 | EN_CVDDX EN_CVDDX | EN_CVDDX EN_CVDDX |

| P5.4 P5.4 | GPIO3/PWM GPIO3/PWM | ||

| P5.5 P5.5 | GPIO4 GPIO4 | SHDN_N_LT3472 SHDN_N_LT3472 | SHDN_N_LT3472 SHDN_N_LT3472 |

| P5.6 P5.6 | GPIOS/PWM GPIOS/PWM | ||

| P5.7 P5.7 | GPIO6/PWM GPIO6/PWM | ||

| P5.8 P5.8 | GPIO7 GPIO7 | TRIGGERB TRIGGERB | TRIGGERB TRIGGERB |

| P4.1 P4.1 | GPIO8 GPIO8 | RESETB RESETB | RESETB RESETB |

| P4.2 P4.2 | GPIO9/PWM GPIO9/PWM | SPI_CSB_ALT SPI_CSB_ALT | |

| P4.3 P4.3 | GP1010/PWM/CS GP1010/PWM/CS | SPI_CSB_DFLT SPI_CSB_DFLT | |

| P4.4 P4.4 | GPIO11/PWM/MOSI GPIO11/PWM/MOSI | STD_SPI_MOSI STD_SPI_MOSI | STD_SPI_MOSI STD_SPI_MOSI |

| P4.5 P4.5 | GPIO12/MISO GPIO12/MISO | STD_SPI_MISO STD_SPI_MISO | STD_SPI_MISO STD_SPI_MISO |

| P4.6 P4.6 | GPIO13/SCK GPIO13/SCK | STD_SPI_SCK STD_SPI_SCK | STD_SPI_SCK STD_SPI_SCK |

| P4.7 P4.7 | GND GND | GND GND | GND GND |

| P4.8 P4.8 | AREF AREF | ||

| P4.9 P4.9 | SDA SDA | ||

| P4.10 P4.10 | SCL SCL | ||

軟件

我們提供了在Mbed開源軟件上開發的示例源代碼。對這些源代碼的詳細說明參見wiki頁面,開發者稍加修改即可通過SPI對兩個評估板上的每個器件進行獨立編程。寄存器值以及代碼的其他部分可以輕松定制,具體而言是示例3中的寄存器值(DDS生成的正弦波,具有不同的啟動延遲和數字增益設置。修改代碼后,使用Mbed在線編譯器編譯程序。然后將生成的二進制文件拖放到SDP-K1驅動器中。同樣的過程也適用于其他應用。

說明

如圖6的簡化圖所示,器件間的輸出同步是通過測量多個器件的同一DAC輸出通道(即通道1)之間的延遲來實現的。相對于TRIG1(控制器板到板1)改變TRIG2(控制器板到板2)的連接器長度,以及相對于時鐘1(時鐘發生器到板1)改變時鐘2(時鐘發生器到板2)的連接器長度,這兩種情況對同步的影響可以使用示波器進行觀察。

結果

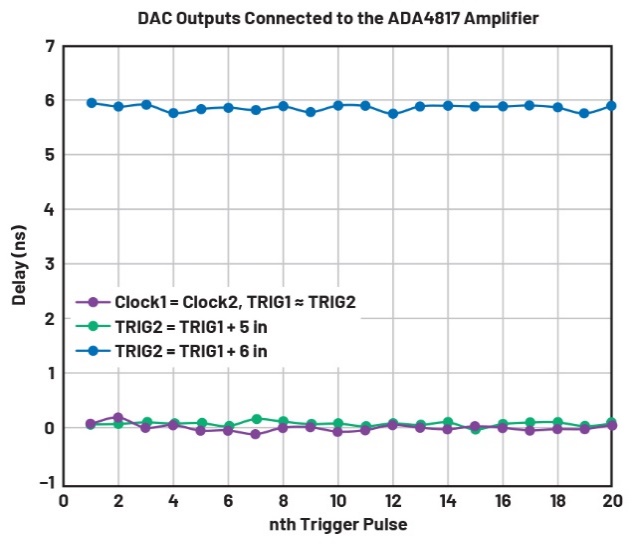

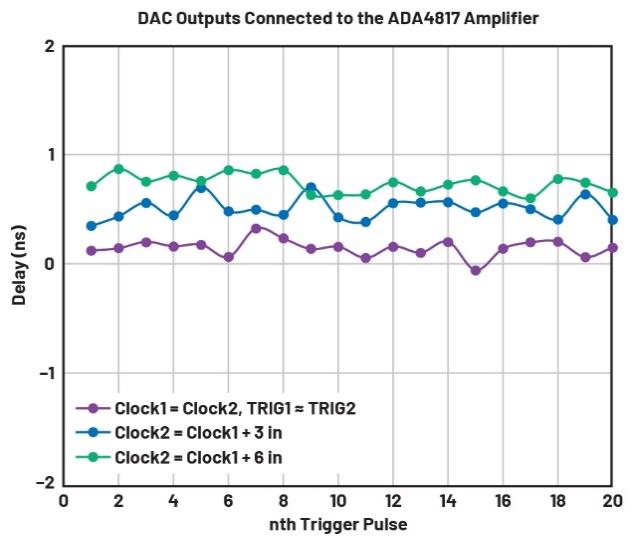

圖9記錄了改變觸發連接器長度時的測量結果,而圖10記錄了改變時鐘連接器長度時的測量結果。

圖9.不同TRIG2連接器長度下板1和板2的OUT 1之間的延遲。

如果TRIGGER引腳所連接的數字輸出具有與STM32F469NI(SDP-K1上的微控制器)類似的驅動特性,那么TRIGGER走線容差只要在5英寸以內,就能維持器件間同步。

圖10.不同時鐘2連接器長度下板1和板2的OUT 1之間的延遲。

匹配的時鐘輸入走線將導致最短的器件到器件的輸出延遲,但根據特定系統中可容忍的延遲,可以相應地調整時鐘走線長度容差。

結語

在超聲設備制造中,利用AD9106評估平臺提供的設計靈活性和定制優勢可以縮短開發流程和上市時間。無需設計新的發射子系統原型即可評估多個發射DAC(如AD9106)的同步。通過使用兩個AD9106-ARDZ-EBZ板、一個SDP-K1控制器板并對示例Mbed代碼進行少量修改,就能實現對同步的評估。

(來源:ADI公司,作者:Sunshine Grace Cabatan,硬件工程師,Melissa Lorenz Lacanlale,應用工程師

評論