西安紫光國芯新一代多層陣列SeDRAM技術

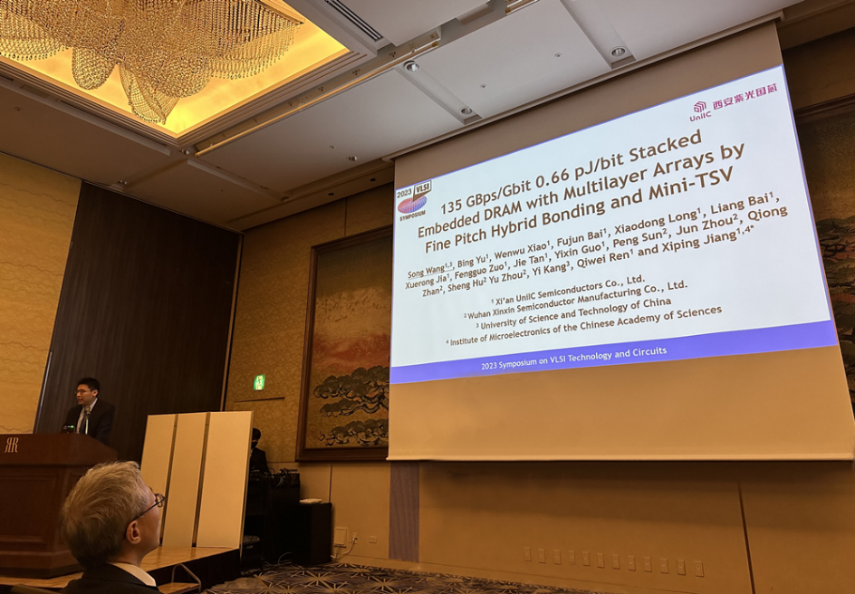

編者按:近日,西安紫光國芯半導體股份有限公司(以下簡稱“西安紫光國芯”)在VLSI 2023技術與電路研討會上(2023 Symposium on VLSI Technology and Circuits)公開發表了技術論文——《基于小間距混合鍵合和mini-TSV的135GBps/Gbit 0.66 pJ/bit 嵌入式多層陣列 DRAM》(135 GBps/Gbit 0.66 pJ/bit Stacked Embedded DRAM with Multilayer Arrays by Fine Pitch H

本年度 VLSI 會議共收到全球投稿 632 篇,在最終錄取的212 篇中,僅有2篇來自中國內地企業,其中1篇便是來自西安紫光國芯的嵌入式多層陣列DRAM論文。

本文引用地址:http://www.104case.com/article/202308/449513.htm

論文第一作者西安紫光國芯副總裁王嵩代表公司作論文報告

本次VLSI 2023上,西安紫光國芯發布的新一代多層陣列SeDRAM,相較于上一代單層陣列結構,新一代技術平臺主要采用了低溫混合鍵合技術(Hybrid Bonding,HB)和mini-TSV堆積技術。該技術平臺每Gbit由2048個數據接口組成,每個接口數據速度達541Mbps,最終實現業界領先的135GBps/Gbit 帶寬和0.66 pJ/bit 能效,為疊加更多層 DRAM 陣列結構提供先進有效的解決方案。

嵌入式多層陣列SeDRAM示意圖

論文通訊作者西安紫光國芯總經理江喜平表示,“2020年IEDM我們發布了第一代SeDRAM技術,之后我們實現了多款產品的大規模量產。這次發布的新一代多層陣列SeDRAM技術,實現了更小的電容電阻、更大的帶寬和容量,可廣泛應用于近存計算、大數據處理和高性能計算等領域。”

西安紫光國芯異質集成嵌入式DRAM(SeDRAM)基于混合鍵合技術實現了邏輯單元和 DRAM陣列三維集成,多項研發成果已先后在IEDM 2020、CICC 2021、ISSCC 2022等多個期刊和會議上公開發表和作專題報告。

評論