基于FPGA的8K分屏器設(shè)計

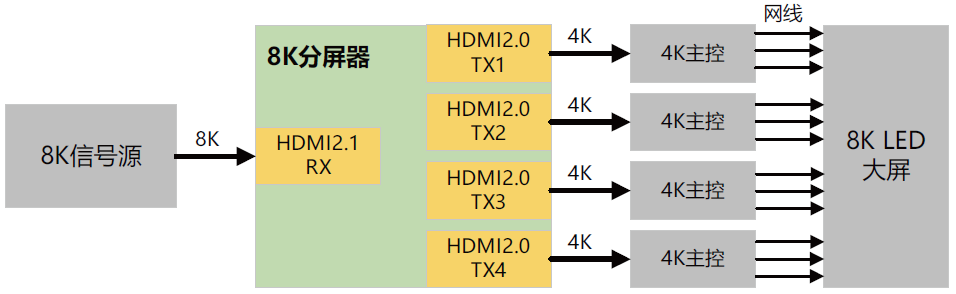

目前主流的LED 主控最大只能支持4k、60 Hz 信號輸入,但是目前8k LED 大屏技術(shù)已經(jīng)成熟,且已經(jīng)慢慢進(jìn)入商用。如圖1 所示,8k LED 大屏的主控一般由4臺4k主控拼接而成,但是前端8K 信號源目前已普遍采用HDMI2.1接口單線傳輸8K 信號,為了滿足8kLED大屏顯示系統(tǒng)需要,8K 分屏器應(yīng)運而生。8k 分屏器可以將8k信號按“田”字型分割成4 路4k 信號輸出,正好可以分別對接4臺4k主控,從而實現(xiàn)8k LED 大屏顯示。此分屏器可廣泛應(yīng)用于各種8k 大屏顯示系統(tǒng)。

本文引用地址:http://www.104case.com/article/202307/449094.htm本文設(shè)計的8k 分屏器采用FPGA 純硬件邏輯實現(xiàn),用戶操作十分簡單,接上電源和5根HDMI 線之后上電即可使用,無需遙控或按鍵操作。

圖1 8K LED大屏系統(tǒng)框圖

1 硬件設(shè)計

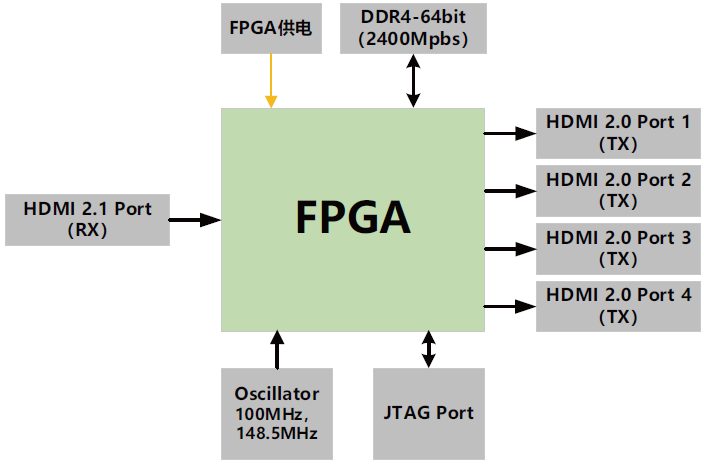

8k分屏器主芯片為FPGA芯片,芯片自帶速率高達(dá)12.5 Gbit/s 的通用高速收發(fā)器,擁有DDR4 PHY 和DDR4硬核控制器,DDR4最大傳輸速率2 400 Mbit/s。硬件層面,如圖2 所示,HDMI2.1 輸入接口的高速信號接到FPGA高速收發(fā)器的接收通道,4 路HDMI2.0 輸出接口的高速信號接到FPGA 高速收發(fā)器的發(fā)送通道,HDMI2.1 TX 和HDMI2.0 RX 的接口協(xié)議由FPGA 內(nèi)部可編程邏輯實現(xiàn)。電路板上有64 bit DDR4 芯片(速率2 400 Mbit/s),用于緩存和切割接收的8K 視頻信號。板上還提供用于HDMI接口IP 的100 MHz和148.5 MHz固定晶振,以及一個JTAG 接口用于FPGA 配置文件下載和調(diào)試。

圖2 電路硬件框圖

2 FPGA邏輯設(shè)計

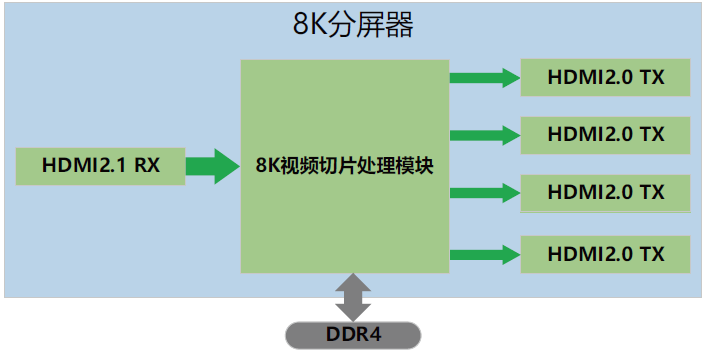

FPGA 設(shè)計框圖如圖3 所示,HDMI2.1、8k 視頻信號進(jìn)入FPGA 芯片之后,首先經(jīng)過高速收發(fā)器的接收通道將高速串行信號轉(zhuǎn)換成低速并行信號,然后經(jīng)過HDMI2.1 RX IP 處理后輸出接收的視頻信號,視頻信號隨后進(jìn)入8k 視頻切片處理模塊,經(jīng)過此模塊處理后輸出4 路4k 信號,輸出的4 路4k 信號分別進(jìn)入4 個HDMI2.0 TX IP,TX IP 將數(shù)據(jù)按HDMI2.0 標(biāo)準(zhǔn)打包后輸出到高速收發(fā)器的發(fā)送通道,此發(fā)送通道將低速并行信號轉(zhuǎn)換成高速串行信號輸出,輸出的信號直接接到HDMI2.0 輸出接口。

圖3 FPGA邏輯設(shè)計框圖

3 結(jié)束語

本文本文設(shè)計了一款8k 分屏器,支持一路HDMI2.1、8k、60 Hz 信號輸入,四路HDMI2.0、 4k、60 Hz信號輸出,此分屏器使用簡單,工作穩(wěn)定,可用于各種8k 大屏顯示系統(tǒng)。

(本文來源于《電子產(chǎn)品世界》雜志2023年7月期)

評論