生成與模擬電壓的平方根成反比的脈沖寬度

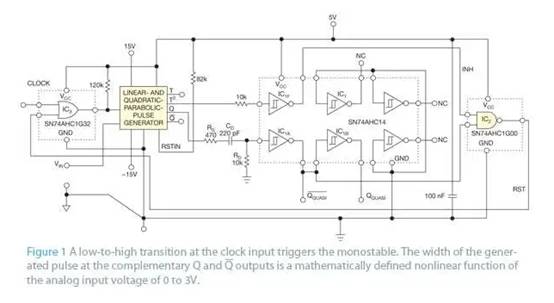

盡管單穩(wěn)態(tài)僅需進(jìn)行此修改即可發(fā)揮作用,但圖 1中IC 1、 IC 2和 IC 3的邏輯電路 增加了另一個功能。添加的邏輯可確保發(fā)生器忽略進(jìn)入單穩(wěn)態(tài)繁忙狀態(tài)的下一個觸發(fā)脈沖。

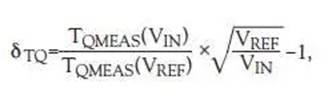

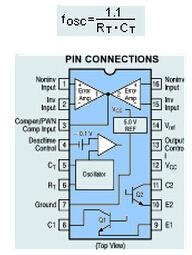

本文引用地址:http://www.104case.com/article/202303/444917.htm圖 1中的電路 是一種邊沿觸發(fā)單穩(wěn)態(tài)電路,它基于先前設(shè)計的邊沿觸發(fā)拋物線脈沖發(fā)生器。該電路通過將級聯(lián)中個積分器的輸入端(包括 IC 3 和 S 2 (在原始設(shè)計中))與參考電壓源 V REF斷開,并將其連接到輸入電壓端子,對早期發(fā)生器進(jìn)行了簡單但重要的修改在圖 1中。

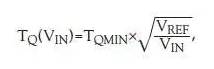

該電路中 outputQ 的輸出脈沖寬度為

在哪里

τ IL 和 τ IQ分別是包含的 IC 2D和 IC 2C 的級聯(lián)中個和第二個積分器的時間常數(shù)。

盡管單穩(wěn)態(tài)僅需進(jìn)行此修改即可發(fā)揮作用,但圖 1中IC 1、 IC 2和 IC 3的邏輯電路 增加了另一個功能。添加的邏輯可確保發(fā)生器忽略進(jìn)入單穩(wěn)態(tài)繁忙狀態(tài)的下一個觸發(fā)脈沖。

這樣,發(fā)生器的積分電容器可以放電接近 0V,誤差不超過 0.4%,即使在相對較高的觸發(fā)頻率下,超過 1/[T Q (V IN )] 的值。因此,給定輸入的輸出脈沖電壓具有恒定寬度,即使觸發(fā)周期接近或小于輸出脈沖的寬度。

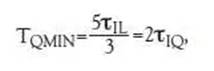

由 IC 1 和 IC 2組成的子電路 產(chǎn)生一個 RST(復(fù)位)信號,其后沿決定單穩(wěn)態(tài)一個工作周期的結(jié)束。該電路中的 RST 信號禁止在 Q 輸出的低到高轉(zhuǎn)換和 RST 信號的高到低轉(zhuǎn)換的間隔內(nèi)重新觸發(fā)單穩(wěn)態(tài)。為此,觸發(fā)信號的時鐘在 IC 3 中與 RST信號 (圖2 ).

因此,緊接在 RST 脈沖的后沿之后啟用下一個有效觸發(fā)。RST 脈沖的前沿大致發(fā)生在二次拋物線電壓 V OQ達(dá)到其峰值電壓 V PEAK的一半時。RST 脈沖的后沿相對于 V OQ降至 V PEAK /2以下的瞬間延遲. IC 1A 輸入端的R S /C D /R D網(wǎng)絡(luò)的輔助時間常數(shù) (R D +R S )C D定義了此延遲。

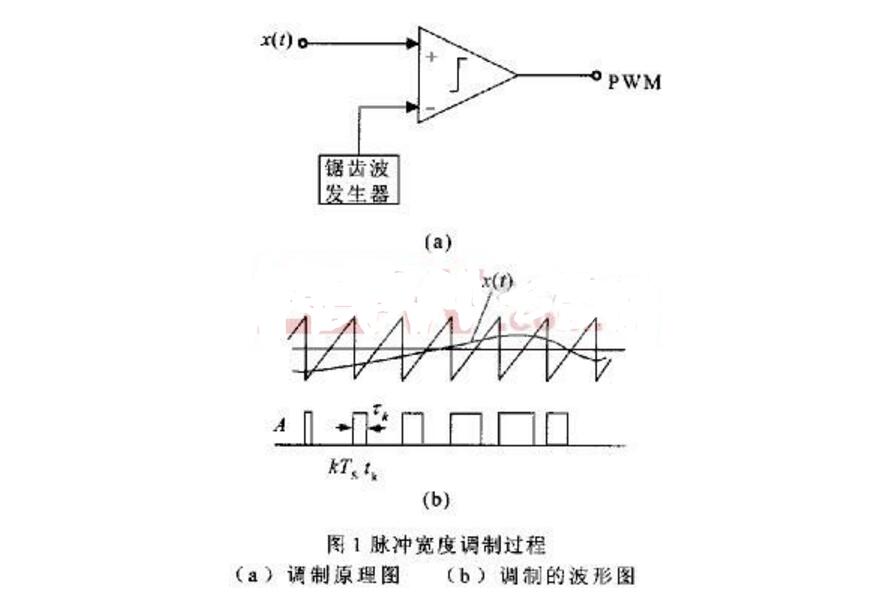

實驗評估表明,輸出脈沖寬度的相對誤差,

是負(fù)的,對于大約 200 到 3000 mV 的輸入電壓不超過 ?8×10 ?4,參考電壓為 3000 mV,的 sIC 1 設(shè)置。

然后誤差幅度上升,在輸入電壓為 99.925 mV 時達(dá)到值 δ TQ =?2.337×10 -3 。通過進(jìn)一步降低輸入電壓,負(fù)誤差幅度減小并且 在輸入電壓為 9.915 mV 時為 δ TQ = ?1.113×10 -3 。輸入電壓為3.08 mV時,相對誤差為正,δ TQ ≈2.9×10 -3。進(jìn)一步降低輸入電壓會導(dǎo)致正誤差迅速上升,在輸入電壓為 1.065 mV 時達(dá)到 3%。但是請注意,輸入電壓跨度幾乎是 3000:1。觸發(fā)頻率為 2 或 200 Hz。

在 2kHz、200kHz 和 2MHz 的觸發(fā)頻率下,您可以獲得幾乎相同的脈沖寬度。由于觸發(fā)頻率變化引起的脈沖寬度的相對變化與 δ TQ 值相當(dāng)或更低。輸入電壓等于參考電壓的滿量程輸入實現(xiàn)了 445.44 微秒的測量脈沖寬度。

借助 V OQ 輸出,您還可以將該電路用作精密二次拋物線時基發(fā)生器;輸入電壓控制發(fā)生器的速度。

評論