AVR單片機IO口結構和上拉和下拉電阻的作用

五、AVR單片機IO口(千呼萬喚始出來)

本文引用地址:http://www.104case.com/article/201811/394646.htm端口引腳配置

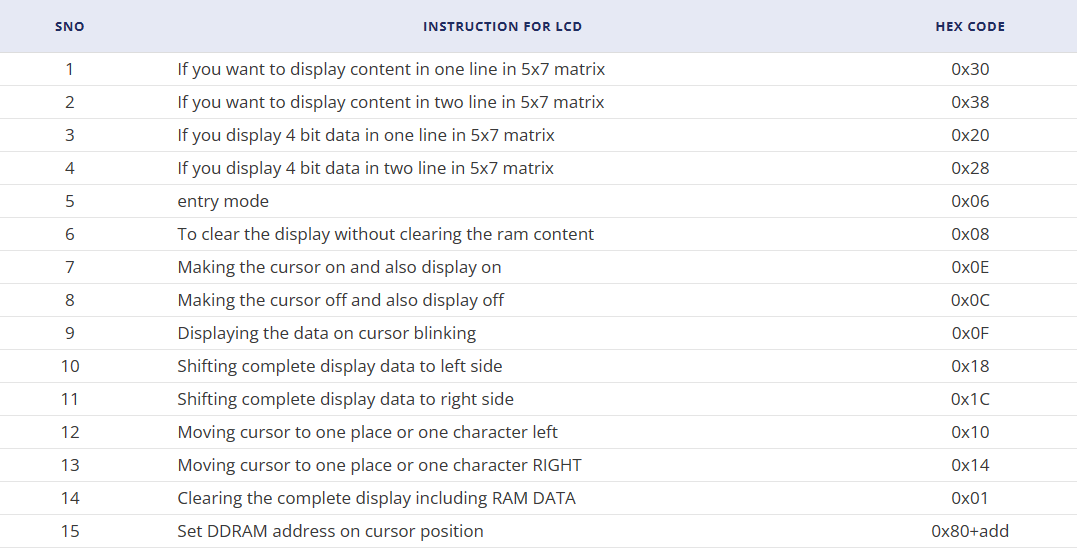

DDxn PORTxn PUD (in SFIOR) I/O 上拉電阻 說明

0 0 X 輸入 No 高阻態 (Hi-Z)

0 1 0 輸入Yes 被外部電路拉低時將輸出電流

0 1 1 輸入 No 高阻態(Hi-Z)

1 0 X 輸出 No 輸出低電平 ( 漏電流)

1 1 X 輸出 No 輸出高電平 ( 源電流)

//////////////////////////////////////////

輸入狀態:

一、上拉輸入狀態:

1、在IO口線懸空時讀入PINxn的值為1,狀態穩定

2、在IO口線外接輸入信號時讀入PINxn的值隨外部信號高低電平變化而變化

二、高阻輸入狀態:

1、在IO口線懸空時讀入PINxn的值為0,且極易受到干撓,狀態很不穩定

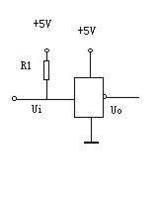

2、外接上拉電阻,在IO口線外接輸入信號時讀入PINxn的值隨外部信號高低電平變化而變化(等同于內接上拉電阻)

輸出狀態:

在輸出狀態下,PORTxn=0則輸出為低電平,PORTxn=1則輸出為高電平

1、輸出低電平,IO口線懸空時讀入PINxn的值為0

2、輸出低電平,IO口線連接VCC或強上拉(指上拉阻值很小,相當于直接連接VCC,能提供足夠的上拉電流)時讀入PINxn的值為1

3、輸出高電平,IO口線懸空時讀入PINxn的值為1

4、輸出高電平,IO口線連接GND或強下拉(指下拉阻值很小,相當于直接連接GND,能吸收足夠的下拉電流)時讀入PINxn的值為0

由于無論如何配置DDRxn,我們都可以讀取PINxn值,綜上所述,我們在讀取PINxn的值時,要想獲得正確且穩定的值,

應該選擇在內部上拉輸入或高阻輸入且外部上拉這兩種方式中進行。當然在選擇內部上拉輸入且外部也上拉的方式也是

可以的,只是內部和外部都加上拉(重復上拉)沒有什么意義。

還有一點就是我們在讀取軟件賦予的電平時,讀PINxn值之前,要插入一個NOP。

也就是說在IO口輸出邏輯電平之后再讀入這個輸出的值中間應插入一個NOP。

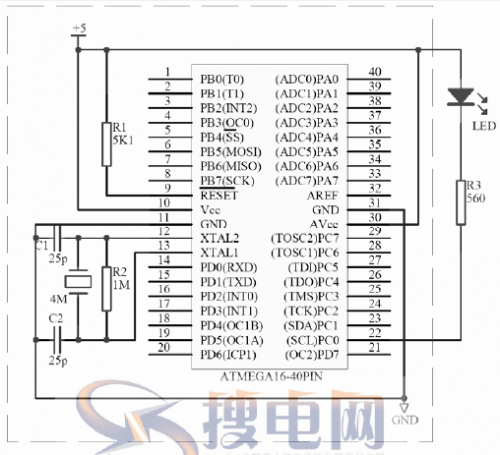

AVR的真正雙向IO結構就復雜多了,單是控制端口的寄存器也有4個

PORTx.DDRx,PINx,SFIOR(PUD位),不過功能也強勁多了

作為通用數字I/O 使用時,所有AVR I/O 端口都具有真正的讀- 修改- 寫功能。

這意味著用SBI 或CBI 指令改變某些管腳的方向( 或者是端口電平、禁止/ 使能上拉電阻) 時不會無意地改變其他管腳的方向( 或者是端口電平、禁止/ 使能上拉電阻)。

輸出緩沖器具有對稱的驅動能力,可以輸出或吸收大電流,直接驅動LED。

所有的端口引腳都具有與電壓無關的上拉電阻。

并有保護二極管與VCC 和地相連。

* (很多數字器件都有保護二極管,在低功耗應用時要考慮保護二極管的電流倒灌的影響)

每個端口都有三個I/O 存儲器地址:

數據寄存器 –PORTx

數據方向寄存器–DDRx

端口輸入引腳 –PINx。

數據寄存器PORTx和數據方向寄存器DDRx為讀/ 寫寄存器,而端口輸入引腳PINx為只讀寄存器。

但是需要特別注意的是,對PINx 寄存器某一位寫入邏輯"1“ 將造成數據寄存器相應位的數據發生"0“ 與“1“ 的交替變化。

當寄存器MCUCR 的上拉禁止位PUD置位時所有端口引腳的上拉電阻都被禁止。

在( 高阻態) 三態({DDxn, PORTxn} = 0b00) 輸出高電平({DDxn, PORTxn} = 0b11) 兩種狀態之間進行切換時,

上拉電阻使能({DDxn, PORTxn} = 0b01) 或輸出低電平({DDxn,PORTxn} = 0b10) 這兩種模式必然會有一個發生。

通常,上拉電阻使能是完全可以接受的,因為高阻環境不在意是強高電平輸出還是上拉輸出。

如果使用情況不是這樣子,可以通過置位SFIOR 寄存器的PUD 來禁止所有端口的上拉電阻。

在上拉輸入和輸出低電平之間切換也有同樣的問題。

用戶必須選擇高阻態({DDxn,PORTxn} = 0b00) 或輸出高電平({DDxn, PORTxn} = 0b10) 作為中間步驟。

評論