亞閾值數字標準單元庫設計

作者 史興榮 何進 張九柏 張子驥 賀雅娟 電子科技大學電子科學與工程學院(成都 610054)

本文引用地址:http://www.104case.com/article/201810/393368.htm史興榮 (1990-),男,碩士研究生,研究方向:低功耗數字集成電路設計

賀雅娟 (1978-),女,副教授,研究方向:專用集成電路與系統、超低壓超低功耗數字集成電路設計等。

摘要:基于對0.18 μm標準CMOS工藝的研究,本文設計了一套完備的電源電壓為0.4 V的亞閾值數字標準單元庫。設計流程包括工藝研究與方案設計、單元設計與物理實現、庫文件的提取以及單元庫驗證。提出了傳統溝道寬度調節與溝長偏置相結合的尺寸調整策略,有效增強PMOS管驅動并減小漏電流,提升庫單元穩定性。利用ISCAS基準測試電路完成亞閾值標準單元庫的驗證,0.4 V電壓下,相同設計,基于亞閾值數字標準單元庫的設計的相比于基于商用庫的設計,能耗減小20%以上,數據延時也有所減小,即亞閾值標準單元庫性能明顯優于商用庫相比。

0 引言

隨著集成電路工藝技術的不斷發展,工藝線寬不斷減小以追求高集成度與高速度,帶來的最大問題就是功率密度的不斷增大,功耗過高問題逐漸成為限制集成電路發展的重要原因。近年來興起的無線傳感網絡、醫療電子和便攜式消費電子等熱門領域,對功耗要求越來越高,低功耗技術成為工業界和學術界研究的焦點。

在CMOS數字電路中,系統功耗包含動態功耗和靜態功耗,動態功耗與供電電壓的平方成正比,靜態功耗與供電電壓成正比,因此降低供電電壓是降低功耗最有效的方法,1970年以來,極低電壓設計技術的研究被廣泛展開。其中亞閾值電路設計技術,通過將系統電源電壓降低至器件亞閾值區域以獲得極低的系統總功耗,屬于系統級低功耗技術,能達到更好的降低功耗的效果,因此成為目前研究的熱點。

大規模數字集成電路是基于標準單元庫或者門陣列完成設計,要實現大規模亞閾值數字電路的實現,我就需要建立亞閾值數字標準單元庫與亞閾值SRAM,針對亞閾值電壓,對基本的邏輯門(與門、或門、非門、選擇器、加法器等)以及SRAM單元進行設計和優化,使其在亞閾值下達到最優性能,進而提升整體電路性能。

本文基于0.18 μm標準工藝,首先分析了亞閾值下NMOS和PMOS失配增大的問題,并基于數字標準單元庫設計流程與亞閾值單元庫設計設計方法的研究,提出了傳統溝道寬度調節與溝長偏置相結合的尺寸調整策略,在此基礎上設計了一套電源電壓為0.4 V的定制化亞閾值數字標準單元庫,基于該亞閾值數字標準單元庫完成數字集成電路的設計,并以ISCAS基準測試電路為載體對該亞閾值庫與原商用庫在0.4 V電壓下重新特征化的單元庫進行了對比,驗證了該亞閾值數字標準單元庫的完備性與功能正確性,并且在功耗和性能方面相比原商用庫有很大改善。

1 標準單元庫設計流程

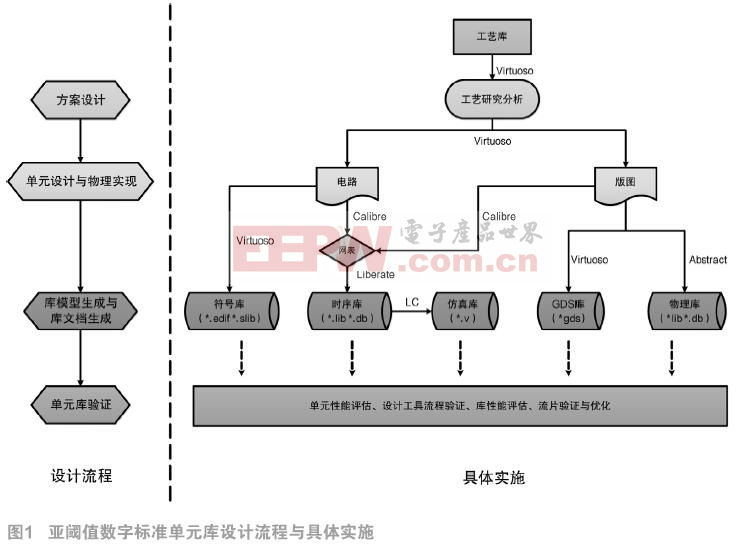

數字標準單元庫的設計就是基于Foundry提供的工藝庫,定制完成基本邏輯單元的電路和版圖設計,并提取相應的時序和物理信息形成文件,供綜合工具和物理實現工具調用以完成數字集成電路的設計和分析。設計流程包括工藝研究分析、單元電路和版圖設計、單元庫建模和庫文檔生成、和單元庫評估驗證。

圖1所示是本次亞閾值數字標準單元庫設計的流程及具體實施示意圖,在電路設計前,首先了解和研究該工藝的基本特性,包括晶體管電流電壓特性、器件的漏極電流等參數隨溝道長度和溝道寬度的變化情況,以及PMOS和NMOS的驅動強弱等,這些基于Virtuoso完成。其次,基于Virtuoso平臺完成工藝研究分析以及電路圖版圖的設計,并基于Calibre完成單元電路網表的提取。然后,利用Liberate基于單元網表完成時序庫建模,基于版圖用Abstract完成物理庫建模,用Library Compiler完成仿真庫文件的生成,以及符號庫、時序庫和物理庫文件的格式轉換。最后,用綜合和布局布線工具實現基準電路的設計,完成亞閾值庫的驗證工作。

2 理論研究與工藝分析

2.1 最小能量點理論

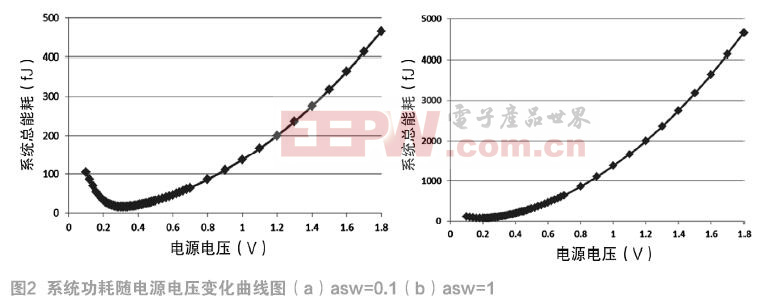

亞閾值電路的理論基礎就是最小能量點理論,電路總能耗包含動態能耗和動態能耗,動態能耗隨著供電電壓的減小呈平方關系減小,靜態能耗與時鐘周期、漏電流和供電電壓成正比,隨著電源電壓的減小,尤其是在器件閾值電壓下,時鐘周期呈指數上升,導致漏電能耗迅速增大。由此,對于特定工藝下的電路,隨著電源電壓的減小,動態能耗不斷減小,而靜態能耗先增大,存在某一特定電源電壓值,使得總能耗最小,即最小能量點,且最小能量點對應的電源電壓一般在亞閾區。

為驗證最小能量點理論及確定亞閾值標準單元庫的電源電壓,針對所涉及的工藝,設計了驗證電路。驗證電路包含10條50級的反相器鏈,通過給定10條鏈路不同的輸入來控制開關活動性的大小,大小可以設定為0.1、0.2、……、1.0。如圖2所示,分別是開關活動因子asw等于0.1和1時不同電壓下的系統總功耗隨電源電壓變化曲線,可以看出,最小能耗點分布在電源電壓為0.2 V~0.4 V范圍內。本設計中,考慮到系統穩定性及數字單元庫的適用范圍,電源電壓設定為0.4 V。

2.2 晶體管電流電壓特性

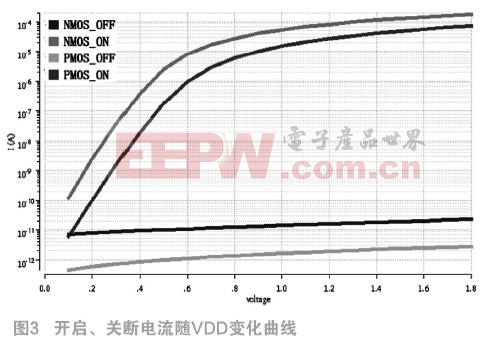

NMOS和PMOS的驅動能力是不一樣的,即存在不匹配,在標準電壓下(即超閾值電壓),NMOS的驅動能力約為PMOS驅動能力的兩倍,這得益于電子遷移率為空穴遷移率兩倍多,在建立標準單元庫時,單元設計時就要考慮到NMOS/PMOS失配,通過尺寸調節來實現單元的上拉下拉匹配。但是在亞閾值電壓下,由MOS模型分析可知,NMOS/PMOS失配會增大,因此將商用標準單元庫運用到低壓電路中,電路性能會嚴重下降,會出現噪聲容限下降,抗工藝波動能力下降,甚至邏輯誤判導致電路無法正常工作等。

對相同尺寸的NMOS管和PMOS管進行仿真,晶體管的開啟電流和關斷電流隨電源電壓的變化曲線,如圖3所示,隨著電源電壓的不斷減小,NMOS管和PMOS管的開啟電流和關斷電流都不斷減小,但是NMOS與PMOS的開啟電流之比卻在不斷增大,在電壓為0.4 V時,大尺寸管PMOS/NMOS開啟電流比已接近于7,而對于最小尺寸管,甚至高達20,即PMOS和NMOS存在嚴重的不匹配,這給我們標準單元設計時上拉下拉平衡造成很大困難。

2.3 反短溝道效應

隨著工藝尺寸的不斷減小,亞閾值電壓下,晶體管電流表現出明顯的反短溝道效應,隨著溝道長度L的變化,晶體管的開啟電流表現出先增大后減小的變化趨勢,即存在最優溝道長度。針對本工藝,通過對NMOS管和PMOS管的仿真發現,NMOS管開啟電流不存在反短溝道效應,而PMOS管開啟電流存在明顯的反短溝道效應,即開啟電流I_on隨著溝道長度LP的增大先增大后減小,如圖4所示,可以看出NMOS管開啟電流在LP=200 nm時達到最大。進一步研究發現,最優溝道長度與溝道寬度相關,且增大LP存在面積和漏電流增大的不良影響,因此在實際庫單元設計時,我們將NMOS的溝道長度取值為180 nm,即最小溝道長度,PMOS的溝道長度取值為190 nm,即溝道增量約為最小溝道長度的5%。

3 亞閾值庫的設計

3.1 單元類型選擇與結構設計

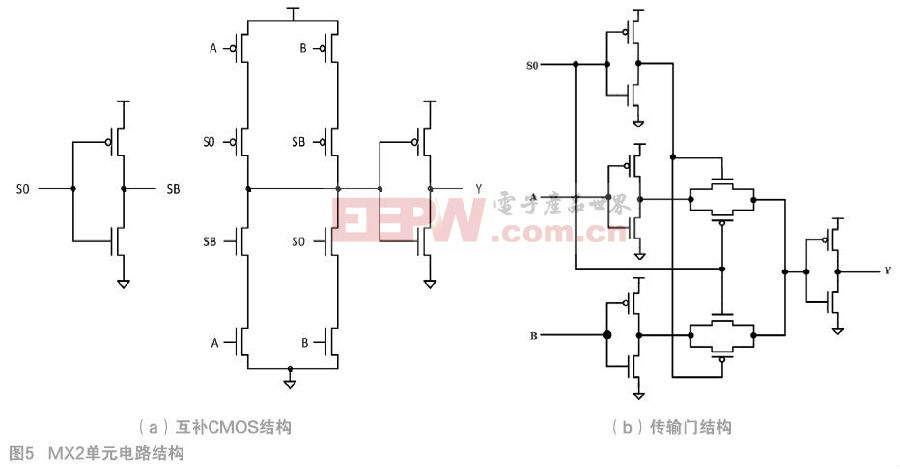

標準單元庫設計中,庫單元的和數量影響著綜合工具在映射和優化過程的有效應,庫單元種類越豐富,電路的優化就越充分。對于亞閾值標準單元庫,由于電源電壓較低,有些復雜單元不能工作,有些單元能工作但是穩定性大幅度下降,為保證功能正常且具有足夠的穩定性,則需要對這些單元進行選擇。選用扇入比較小的邏輯單元,剔除NAND4、NOR4等扇入大的邏輯,而時序優化單元較復雜且功耗較大也需要剔除,觸發器和鎖存器必不可少,但是其種類可以簡化,時鐘樹邏輯單元和物理實現單元必不可少。每種邏輯又包含多種不同驅動能力,也設計了低功耗單元,對于OR2、NOR2等穩定性差的單元,為保證單元穩定性沒有設計低功耗單元。

對于INV、NAND2、NOR2等簡單的庫單元,直接采用傳統的靜態互補CMOS結構,而對于MX、XOR、XNOR、DFF和LATCH等比較復雜單元,傳統互補CMOS結構在亞閾值電壓下穩定性不足。因此需要改變結構,采用在低壓下性能更好的傳輸門結構設計。以二選一選擇單元MX2為例說明傳輸門結構的優勢,圖5所示是MX2單元電路結構(a)互補CMOS結構(b)傳輸門結構。在互補CMOS結構中,有兩個PMOS串聯的結構,PMOS在低壓下驅動很小,相同晶體管尺寸會導致單元穩定性較差,且單元延時較大。傳輸門結構MX2單元由傳輸門和反相器構成,沒有PMOS串聯或NMOS串聯結構,能夠工作在較低電壓,穩定性更高。傳輸門速度由NMOS管決定,延時更小,且可以采用最小尺寸晶體管完成設計,功耗小。

3.2 單元尺寸設計策略

標準單元尺寸設計,就是希望找到最優的尺寸組合,以使電路在功能正確的前提下,實現延時、功耗和面積的兼顧。基于前面第三章對工藝的分析可知,本工藝庫PMOS管存在明顯的電流反短溝道效應,即隨著柵極長度L的增大電流先更大后減小,存在最優L值,所以采用傳統柵極寬度W調節策略與柵極長度L偏置相結合的尺寸調節策略:

(1)針對PMOS存在電流反短溝道效應,進一步仿真發現最優L值與晶體管柵極寬度W相關,但變化比較小,因此為簡化單元仿真量,PMOS管的柵極長度統一設定為190 nm,NMOS管的柵極長度統一設定為180 nm。

(2)根據0.4V電壓下的NMOS/PMOS驅動比,和具體單元的結構分析,以上拉網絡和下拉網絡的匹配為目標,確定PMOS和NMOS的柵極寬度W的大致范圍。

(3)通過分析單元的功耗、延時和面積等參數,確定單元的優化目標函數為f(P, D)=Pi*D,P是單元功耗,由于功耗與面積正相關,也包含了對面積的考慮,D為單元延時,延時為上升下降延時的平均值,考慮了上拉網絡和下拉網絡的平衡以及單元穩定性。i為調節系數,用于調節單元功耗和單元延時的比重,此處i取值為1。調整單元中各晶體管柵極寬度W,使得目標函數達到最優,確定出單元的最優尺寸。

4 亞閾值庫的評估驗證

4.1 單元庫穩定性評估

靜態噪聲容限是衡量單元穩定性的重要參數,測量不同邏輯單元的靜態噪聲容限,來評估我們設計的亞閾值庫的單元穩定性。圖6所示是不同邏輯單元的靜態噪聲容限,可以看出由于其PMOS管串聯的結構特性,庫中NOR2單元的靜態噪聲容限最小,為142 mV,占電源電壓的35.5%,證明我們的庫單元可以工作在很低電壓下,單元庫具有很好的穩定性。

4.2 單元庫的驗證

本次為了驗證所建立的亞閾值單元庫的功能和性能,采用ISCAS85和ISCAS89基準測試電路,選取了典型的五個電路,其中C7552選自ISCAS85是純組合邏輯電路,其余四個電路選自ISCAS89是時序電路。同時對標準單元的單元庫在0.4 V電壓下進行重新特征化,記為商用0.4 V庫,用于和亞閾值庫對比。分別基于亞閾值庫和商用0.4 V庫,完成上述所選基準測試電路的設計,仿真對比結果如表1所示,表1中顯示,基于亞閾值庫的設計在延時和功耗方面都要明顯優于商用0.4 V庫,動態功耗和靜態功耗都減小了20%以上,且延時也有所減小,因此電路的功耗延時積PDP減小超過37%。即基于亞閾值單元庫的電路性能提升,且功耗大幅度下降,驗證了亞閾值單元庫的完備性和良好的性能,及其低功耗特性。

5 結束語

基于對0.18μm標準CMOS工藝最小能耗點的研究,以及對亞閾值電壓下NMOS和PMOS電流電壓特性和PMOS的反短溝道效應的研究,提出了溝道寬度調節和PMOS溝長調制結合的尺寸設計策略,根據數字標準單元庫設計流程建立了一套完備的亞閾值數字標準單元庫。亞閾值庫單元的噪聲容限在電源電壓的35%以上,并采用ISCAS基準電路完成單元庫的驗證。0.4 V電壓下,與商用單元庫相比,亞閾值單元庫功耗減小了20%以上,且性能有所改善。驗證了亞閾值標準單元庫單元的穩定性,以及單元庫的低功耗特性。

參考文獻:

[1]Calhoun B H, Wang A, Chandrakasan A. Modeling and sizing for minimum energy operation in subthreshold circuits[J]. IEEE J. Solid-State Circuits, 2005, 40(9): 1778-1786.

[2]Qian Xie, Jun Xu, Yuan Taur. Review and critique of analytic models of MOSFET short-channel effects in subthreshold[J]. IEEE Transactions on electron devices, 2012, 59(6): 1569-1579.

[3]Alioto M. Ultra-Low Power VLSI Circuit Design Demystified and Explained: A Tutorial[J]. IEEE Trans. Circuits Syst. I, Reg. Papers, 2012, 59(1): 3-29.

[4]Gupta K, Raychowdhury A, Roy K. Digital computation in subthreshold region for ultra-low-power operation: A device-circuit-architecture codesign perspective[J]. Proceedings of the IEEE, 2010, 98(2):160-190.

[5]Liu Bo, Ashouei M, Standard cell sizing for subthreshold operation[C]. Proceeding of the 49th Design Automation Conference. San Francisco, USA, 2012: 425-128.

[6]Gibiluka M, Moreira M. A standard cell characterization flow for non-standard voltage supplies[C]. 29th Symposium on Integrated Circuits and Systems Design. Belo Horizonte, Brazil, 2016

本文來源于《電子產品世界》2018年第11期第38頁,歡迎您寫論文時引用,并注明出處。

評論