邏輯門(mén)電路的傳播速度

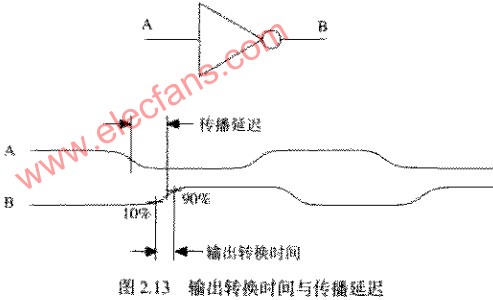

理論上的數(shù)字邏輯設(shè)計(jì)重點(diǎn)關(guān)注的是邏輯門(mén)電路的傳播延遲。相比之下,高頻電子工程中的許多實(shí)際的問(wèn)題通常只取決于一個(gè)更細(xì)微的指標(biāo):最小輸出轉(zhuǎn)換時(shí)間。圖2.13舉例說(shuō)明了這一差別。

本文引用地址:http://www.104case.com/article/201809/388876.htm

較快的轉(zhuǎn)換時(shí)間會(huì)導(dǎo)致返回電流,串?dāng)_和振鈴等等與傳播延遲無(wú)關(guān)的問(wèn)題成倍地增加。如果邏輯產(chǎn)品系列的最小轉(zhuǎn)換時(shí)間比傳播延遲快得多,那么系統(tǒng)設(shè)計(jì)時(shí)會(huì)面臨不必要的麻煩,因?yàn)橄鄳?yīng)器件封裝,電路板布局設(shè)計(jì)和連接器都必須適應(yīng)器件的快速轉(zhuǎn)換時(shí)間,而小的傳播延遲只有利于邏輯時(shí)序。假設(shè)有兩種邏輯產(chǎn)品系列具有相同的最大傳播延遲參數(shù)值。其中輸出轉(zhuǎn)換時(shí)間最慢的將會(huì)更便宜,而且更好用。

許多邏輯產(chǎn)品系列有多種速度-功率組合可以選用。TTL系列包括LS和S等種類。所有CMOS系列都表現(xiàn)出引人注目的功率-速度關(guān)系:從而使任何CMOS系統(tǒng)的功耗與它的時(shí)鐘速率成正比。ECL系列產(chǎn)品可以在近乎兩倍于MECL 10KH系列的速度下工作,但是也消耗了兩倍的功率。

制商更強(qiáng)調(diào)速度和功率的折衷,因?yàn)檫@樣可以使數(shù)據(jù)手冊(cè)看上去更體面。他們經(jīng)常不標(biāo)出器件最小轉(zhuǎn)換時(shí)間。這一個(gè)參數(shù)非常難于控制,除非制造過(guò)程中嵌入特殊的電路以減緩輸出轉(zhuǎn)換的速率。

這種限定轉(zhuǎn)換時(shí)間的電路已經(jīng)逐漸地開(kāi)始進(jìn)入一些邏輯系列產(chǎn)品,自從1971年MECL 10K系列產(chǎn)品出現(xiàn)以來(lái),所有ECL系列都已經(jīng)內(nèi)置了邊沿減緩的電路。出現(xiàn)于1990年的FCT系列產(chǎn)品是第一個(gè)內(nèi)置了邊沿減緩機(jī)制的CMOS電路。從那以后,其他的制造商也采用了這種方法。

這快的轉(zhuǎn)換時(shí)間分別通過(guò)兩種特定方式導(dǎo)致問(wèn)題的產(chǎn)生:由電壓突變產(chǎn)生的影響和由電流突變產(chǎn)生的影響。

評(píng)論