基于可逆邏輯電路的脈沖分配器設計

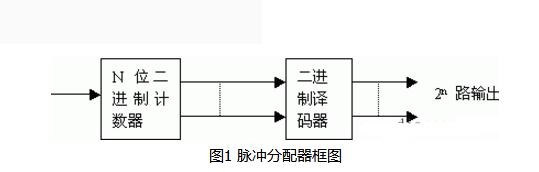

可逆扭環計數器和譯碼器共同組成脈沖分配器,譯碼器主要由與門構成,而可逆邏輯電路中沒有相應的與門,必須用常用可逆邏輯門構造,Toffoli門可以完成此功能,兩輸入的與門要三輸入的Toffoli門構成。另外,不可逆脈沖分配器的扇入扇出需要進行重新設計,每個扇入或者扇出的節點要用Fevnman門對信號進行復制。本文引用地址:http://www.104case.com/article/201809/388701.htm

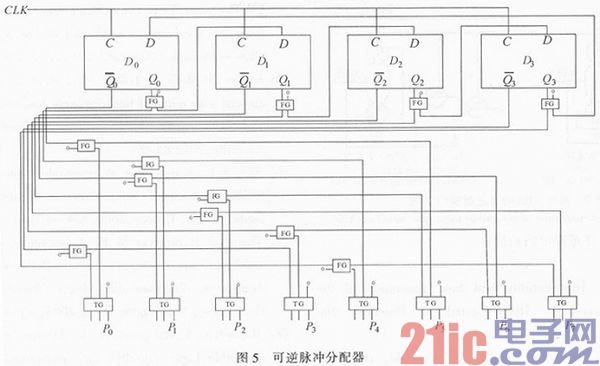

結合圖2所示的可逆扭環計數器和圖4所示的可逆扭環計數器,構建的量子可逆脈沖分配器如圖5所示。

3 仿真結果分析和物理實現

由圖5可以看出,本文所設計的量子可逆脈沖分配器所用量子門數為32,量子代價為96,垃圾位24。

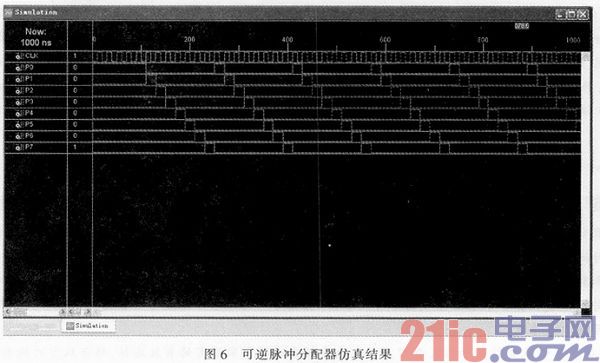

可逆脈沖分配器的結構在實驗中用VHDL進行描述封裝,代碼通過Xilinx ISE9.li下載到Spanan-6 LX FPGA芯片上進行運行仿真,目標器件為XC6SLX9。可逆脈沖分配器的仿真結果如圖6所示。

由圖6可以看出,本文設計的可逆脈沖分配器可以實現8節拍脈沖輸出功能,并且無冒險與競爭現象。

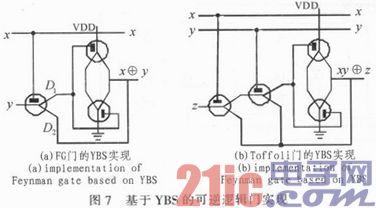

目前已經提出了多種可逆邏輯電路的物理構建方法,如利用低功耗CMOS晶體管構建可逆邏輯門,而利用電子波導Y-分支開關)Y-Branch Switch YBS)構建可逆邏輯門可以用更少的能量改變開關狀態,它的打開和關閉是通過改變電子傳輸兩個方向中的一個,而不是切換當前的開關,在正常情況下,YBS的一次開關動作大約散失0.6meV的熱量,一個信息位丟失所損耗的能量為KT*Ln2,大約等價為18meV,利用YBS作為基本單元構建可逆邏輯門會更加節能。如圖7所示,為利用YBS作為基本單元構建的FG門和Toffoli門,由于所有的可逆邏輯電路都能有Toffo li門實現,所以可逆脈沖分配器可以由圖7所示的可逆邏輯門設計物理電路。

4 結論

文中提出了一種可逆時序電路的設計方法,以不可逆脈沖分配器為例,將其轉化為可逆脈沖分配器,分析了所設計的可逆脈沖發生器的有關性能指標并對其功能進行了仿真。另外提出了可逆脈沖分配器的物理實現方法。結果表明,設計的可逆脈沖分配器能完成脈沖輸出的功能。此方法還可以用于其它可逆時序邏輯電路的設計。

評論