電源要求和電源解決方案的FPGA

自動翻譯,供參考

本文引用地址:http://www.104case.com/article/201808/387005.htm電源要求和電源解決方案的FPGA

現場可編程門陣列(FPGA)被發現在眾多的原型和低到中等批量產品的心臟。 FPGA的主要優點是在開發過程中的靈活性,簡單的升級路徑,更快地將產品推向市場,并且成本相對較低。一個主要缺點是復雜,用FPGA往往結合了先進的系統級芯片(SoC)。

這種復雜性使得電源上的苛刻要求。為了應對這些挑戰,電源需要幾個輸出和開關穩壓器的效率和線性穩壓器的清潔電力的組合。

本文介紹的FPGA的特殊電源要求,說明了如何設計這些聰明的芯片的電源,然后回顧了一系列的針對FPGA應用的電源模塊。

計算系統電源

供電的FPGA看起來像一個完整的系統供電。電源設計工程師面臨的3到15的電壓軌供給(有時甚至更多)的挑戰;而這僅僅是開始。 FPGA是通常制造的使用需要低核心電壓的最新晶片制造技術,但是電源也必須供電多個導軌特種塊和電路,提供多個電壓電平,對于高功率模塊供給額外的電流,和滿足噪聲敏感元件的要求。

只是為了讓事情變得更加復雜,甚至FPGA的同一制造商可以差別很大,使其成為重要的是,工程師選擇每個芯片的最佳電源。這樣的選擇取決于多種因素,諸如電壓和功率需求為每個導軌,導軌'排序要求,以及系統的電源管理的需要。

在設計一個FPGA電源的第一步驟是確定各個電壓軌和他們的要求。 FPGA供應商通常會提供一個“銷單”,用于指定每個供電引腳連接到設備的電壓軌的電壓電平。例如,表1顯示了一些電壓軌Altera的Stratix IV GX FPGA。

Type | Voltage Value | Voltage Name | Description | Share/Isolate |

FGPA voltages | 0.9 V | VCC | FPGA core power | Share |

0.9 V | VCCD_PLL | PLL digital power | Share/isolate | |

1.2 V - 3.0 V | VCCIO | I/O supply voltage, banks 1-8 | Share | |

½ VCCIO | VREF | Input reference voltage, banks 1-8 | Share | |

1.5 V | VCCPT | Programmable power technology | Share/isolate | |

1.8 V / 2.5 V / 3.0 V | VCCPGM | Configuration pin power | Share | |

2.5 V | VCCCLKIN | Differential clock input power | Share | |

2.5 V | VCCA_PLL | PLL analog power | Share/isolate | |

2.5 V | VCCAUX | Auxiliary power | Share/isolate | |

2.5 V | VCCBAT | Battery back up, connect to battery | Isolate | |

2.5 V / 3.0 V | VCCPD | I/O pre-driver power | Share | |

Transceiver voltages | 0.9 V | VCCHIP | Transceiver hard IP digital power | Share |

1.1 V | VCCR | Transceiver receiver analog power | Share/isolate | |

1.1 V | VCCT | Transceiver transmitter analog power | Share/isolate | |

1.1 V | VCCL_GXB | Transceiver clock power | Share/isolate | |

1.4 V / 1.5 V | VCCH_GXB | Transceiver transmit output buffer power | Share/isolate | |

2.5 V / 3.0 V | VCCA | Transceiver high voltage power | Share/isolate |

表1:電壓軌了Altera的Stratix IV GX的一個子集。 (Altera公司提供)

從表1可以看出,FPGA的軌道在根據塊被供電在幾個不同的電壓運行。要求通常包括核心(供電的內部邏輯陣列),I / O(驅動所述I / O緩沖器可以在銀行被分組,從一個不同的電壓的每個操作),鎖相環(PLL)(供電中的PLL核心),以及收發器(供給收發器,接收器和發射器中的數字和模擬電路)。

一旦個人電壓軌已經確定,下一步是計算的電流消耗依次在每個軌道上。目前抽簽共享軌應在分析被添加到鐵路上來,總該鐵路。 FPGA廠商通常提供的在線計算器用于這一目的。接著,工程師應當加起來所有構成FPGA的,以便準確地估計整個芯片的功耗的元件的功率消耗。

計算的功率消耗后,下一步驟是檢查規范電壓變化容限和最大電壓紋波為每個軌道。這些參數通常可以在FPGA中的數據表中找到。

負載調節規范確定的范圍內(以mV)以內的電壓調節器的輸出可能偏離了負載的變化。一個典型的規范負載調整為±5 mV時,如果電源是由開關型DC-DC電壓轉換器導出(“開關穩壓器”)。這僅僅是一個,如果在1.2 V指定的電壓軌0.4%的偏差

電壓紋波從峰到峰測量以mV,其大小依賴于的電壓調節器提供所分析的特定軌道的設計。輸出濾波嚴重影響電壓 - (電流)紋波性能。 (見技術專區的文章“電容的選擇是關鍵,以良好的電壓調節器設計”。)大多數FPGA承受高達2%或軌電壓,這是非常現代的開關穩壓器的能力范圍之內的好電壓紋波。

開關或線性穩壓器?

在FPGA電源設計過程的下一步驟是確定是否一個特定的軌道應該由一個開關調節器或線性調節器提供動力。特別需要注意的是針對提供噪聲敏感的電路,如PLL和收發器電路的模擬電源軌。這些軌噪聲過大可能會危及電路的性能。

線性穩壓器提供無波動功率,具有快速的響應,更簡單易用,并采取比開關設備的空間更小。它們是噪聲敏感的PLL和收發器軌道一個不錯的選擇。主要的缺點是缺乏效率的,尤其是當輸出電壓比輸入低了很多。

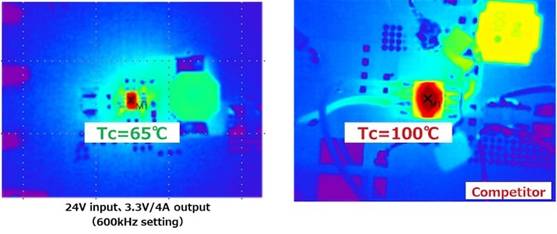

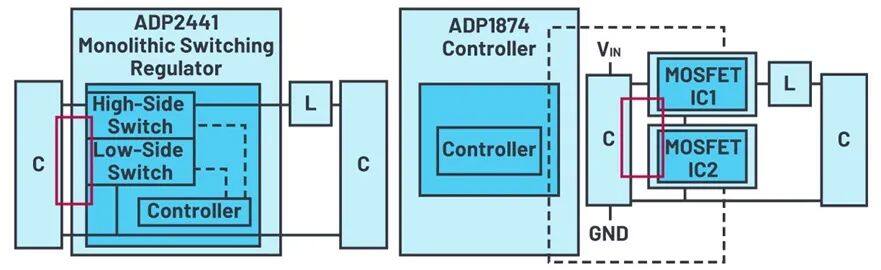

開關穩壓器的高電源軌,他們的更高的效率低于噪音更重要的是更好的選擇。它們是數字核心邏輯和I供電不錯的選擇/ FPGA中,其中電流的要求可以很容易地運行到幾十安培的O操作。的開關穩壓器的缺點是,它比較復雜,體積較大,并且需要更多的外部元件。 (見技術專區的文章“了解優勢和線性穩壓器的缺點”。)

由此產生的電源可以有點復雜,包括在“權力樹”(圖2)幾個開關穩壓器和線性穩壓器。

評論