教你在電路板設(shè)計(jì)中通過傳輸線抑制EMI

做好PCB設(shè)計(jì)絕對(duì)是一名電源新手成功向高手進(jìn)階的證明之一,如果能在做好PCB設(shè)計(jì)的同時(shí)控制好電路板中的EMI,那么更是證明了設(shè)計(jì)者的實(shí)力。那么如何在高速PCB的設(shè)計(jì)過程中對(duì)EMI進(jìn)行有效的控制呢?本文就將從傳輸線參數(shù)的角度來為大家進(jìn)行分析。

本文引用地址:http://www.104case.com/article/201808/386341.htm對(duì)于PCB板來說,PCB上的每一條走線都可以有用三個(gè)基本的分布參數(shù)來對(duì)它進(jìn)行描述,即電阻、電容、電感。在EMI和阻抗的控制中,電感和電容的作用很大。

電容是電路系統(tǒng)存儲(chǔ)系統(tǒng)電能的元件。任何相鄰的兩條傳輸線之間,兩層PCB導(dǎo)電層之間以及電壓層和周圍的地平面之間都可以組成電容。在這些所有的電容中,傳輸線和它的回流電流之間組成的電容數(shù)值最大,也數(shù)量最多,因?yàn)槿魏蔚膫鬏斁€,它都會(huì)在它的周圍通過某種導(dǎo)電物質(zhì)形成回流。

根據(jù)電容的公式:C=εs/(4kπd),他們之間形成的電容的大小和傳輸線到參考平面的距離成反比,和傳輸線的直徑(橫截面積)成正比。我們都知道,如果電容的數(shù)值越大,那么他們之間存儲(chǔ)的電場(chǎng)能量也越多,換句話說,他往外部泄露系統(tǒng)能量的比率將更少,那么這個(gè)系統(tǒng)產(chǎn)生的EMI就會(huì)得到一定的抑制作用。

電感是電路系統(tǒng)中存儲(chǔ)周圍磁場(chǎng)能量的元件。磁場(chǎng)是由流過導(dǎo)體的電流產(chǎn)生的感生場(chǎng)。電感的數(shù)值表示它存儲(chǔ)導(dǎo)體周圍磁場(chǎng)的能力,如果磁場(chǎng)減弱,感抗就會(huì)變小,感抗變大的時(shí)候,磁場(chǎng)就會(huì)增大,那么對(duì)外的磁能量輻射也會(huì)變大,即EMI值越大。所以系統(tǒng)的電感越小,那么就能對(duì)EMI進(jìn)行抑制。在低頻情況下,如果導(dǎo)體變短,厚度變大,變寬的時(shí)候,導(dǎo)體的電感就會(huì)變小,而在高頻情況下,磁場(chǎng)的大小則和導(dǎo)線及其回流構(gòu)成的閉環(huán)面積的函數(shù),如果把導(dǎo)線與其回路靠近,由于回流和本身電流大小相等(在最佳回流狀態(tài))方向相反,所以兩者產(chǎn)生的磁場(chǎng)就會(huì)相互抵消,降低了導(dǎo)體的感應(yīng)電感,所以,保持導(dǎo)體上電流和其最佳回流路徑,能夠一定程度的減小EMI。

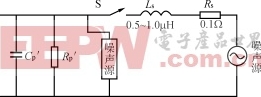

而在一個(gè)實(shí)際電路中,導(dǎo)線的電容和電感是融合為一體的,如果只分析電容或者只考慮電感都有些片面,所以我們引入阻抗。阻抗是傳輸線上輸入電壓對(duì)輸入電流的比率值(Z0=V/I)。導(dǎo)線和回路之間的阻抗是導(dǎo)線及其回路之間電感和電容的函數(shù),阻抗ZO等于(L/C)1/2。

通過前面的分析和阻抗ZO的公式,從抑制EMI角度上來說,希望阻抗越小越好。當(dāng)阻抗比較小即電容較大和電感較小的時(shí)候只要保持電路的正常布線,使電流保持最佳回流路徑,就可以使EMI控制在最小。而當(dāng)電容變小,電感變大,將會(huì)使系統(tǒng)屏蔽電磁場(chǎng)能量的能力下降,外泄電磁場(chǎng)能量增加,EMI變大。

通過以上的介紹可以看到,如果想要保持高速PCB當(dāng)中的EMI抗性,就需要對(duì)電容進(jìn)行部分的調(diào)整,以便于讓電流保持最佳的回流路徑,從而達(dá)到對(duì)EMI電磁干擾進(jìn)行最大程度抑制的效果。當(dāng)然這也是站在只以EMI抑制為目的角度來進(jìn)行的,在實(shí)際操作中要考慮的因素則要更多。

評(píng)論