從技術層級分析典型的嵌入式系統設計是什么樣的?

3、相關外部設備的選擇:

在確定操作系統和處理器之后,就可以確定相關的外部設備,如FLASH,RAM,串口等等。在MVB系統中,MVB控制器MVBC(MulTIfuncTIon Vehicle Bus Controller)是一個MVB電路和實際的物理設備之間的接口控制器,它的主要功能是實現MVB總線信號與數據幀的編解碼,糾錯等功能,是本系統中要實現的關鍵的硬件模塊。由于系統規模,上市時間等方面的要求,系統暫時不考慮ASIC實現,因此在MVB系統中用FPGA來實現這個關鍵模塊,FPGA 是ASIC最靈活和最合算的替代方案。考慮到系統需求與FPGA資源,成本,供貨情況等因素,最終選擇了Altera公司的Cyclone系列FPGA, 其開發工具是Quartus II。

4、MVB系統架構

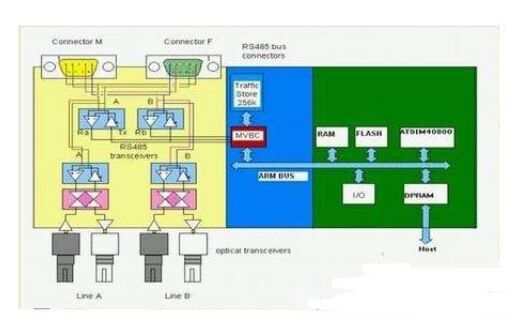

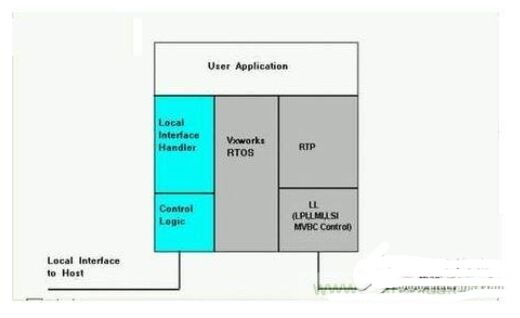

由以上的需求分析和選型,完整的系統硬件架構和軟件架構如圖2圖3所示

圖2:MVB系統的硬件架構。

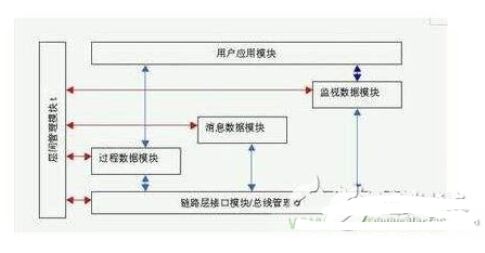

圖3:MVB系統的軟件架構。

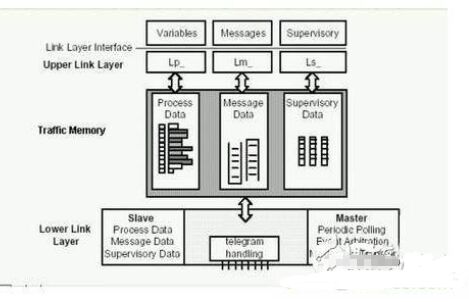

其中,處理器和 MVBC通過Traffic Memory(TM)進行通訊數據交換,所有軟件和MVBC要交換的控制信息和數據都可以在TM地址空間中找到,這個地址空間對處理器和MVBC都是可訪問的。其示意圖4如下

圖4:Traffic Memory。

三、步驟3:詳細的軟硬件設計和RTL代碼、軟件代碼開發

在系統架構確定的基礎上,詳細的軟硬件設計就可以開始了。

1、硬件設計

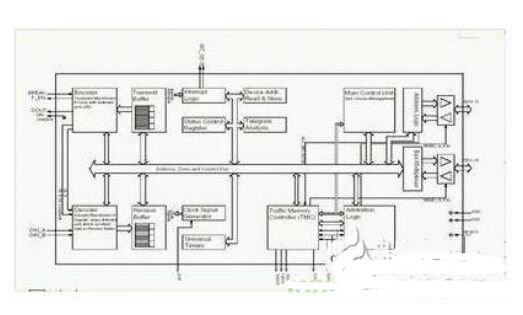

硬件設計設計包括了MVB控制器的FPGA設計和MVB總線系統的板級設計,其中關鍵的MVB控制器的設計如圖5

圖5:MVB控制器的框圖

如圖所示,MVB控制器包含以下功能模塊:

編碼器:產生曼徹斯特編碼,傳送數據幀

發送緩沖區:作為要發送的數據和CRC檢測值的緩沖區

譯碼器:接收、曼徹斯特譯碼,數據提取、數據錯誤檢測

接收緩沖區:作為接收端數據和CRC結果的緩沖區

報文分析單元:檢測主幀和從幀超時,幀誤檢測、錯誤狀態報告

狀態控制寄存器:MVBC配置

主控單元:支持MVBC作為主設備或者從設備工作,支持隊列消息傳送

設備地址讀取和儲存單元:硬件定義的設備地址可以被不同的值覆蓋

地址邏輯:把CPU對MVBC內部寄存器進行訪問的輸入地址進行解析;產生MVBC訪問TM的輸出地址

總線復用、轉換單元:處理MVBC內部的數據傳送

中斷邏輯:支持16種中斷源;

通用定時器:兩個定時輸出信號,可提供給系統同步使用

時鐘產生電路:產生所有MVBC工作的時鐘和計數器

2、軟件設計

由于在MVB系統中,過程數據,消息數據,監視數據是三種不同的通訊機制,因此,MVB系統軟件的模塊設計如圖6。

四、軟硬件的聯調和集成

下面,以一個簡單的例子來說明MVB系統的軟硬件的集成和驗證。

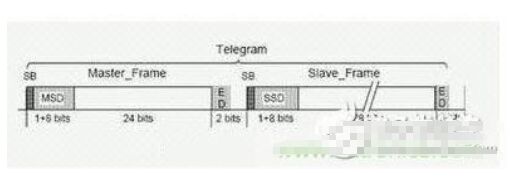

過程數據在MVB系統中是周期性發送的數據,其在本系統中的通訊機制如下:對于發送方,用戶應用模塊將一個端口的過程變量發送給過程數據處理模塊,過程數據處理模塊按照邏輯端口的設置定時通過鏈路層接口模塊更新Traffic Memory當中的相應邏輯端口的數據,此時發送方軟件的任務完成。發送方的MVBC硬件接收總線管理器BA定時發出的主幀,通過譯碼器解碼得到相應的邏輯端口的值,通過查詢Traffic Memory相關的邏輯端口發送設置后將MVBC自動設置為發送狀態,將邏輯端口的數據作為過程數據從幀通過編碼器發出,如圖7所示:

圖7:過程數據通訊示例。

對于接收方,其接收過程與發送方相逆,接收方的MVBC硬件接收總線管理器BA定時發出的主幀,通過譯碼器解碼得到相應的邏輯端口的值,通過查詢 Traffic Memory相關的邏輯端口接收設置后將MVBC自動設置為接收狀態將,在收到發送方發出的從幀后更新相應邏輯端口在Traffic Memory的數據并發出中斷信號從而完成硬件的接收過程。接收方的軟件可以用中斷或定時查詢的方式通過過程數據處理模塊得到更新后的邏輯端口的過程數據

五、系統的測試

在本系統中,系統的測試即包括了軟件的測試,也包括了硬件,FGPA的測試,在本文中不再贅述。

結束語

上述的MVB系統現已運行在列車控制系統中,成功實現對列車的運行控制、機車控制、車輛控制、狀態監測、故障診斷。當然,如有需要,本文中的MVB系統可以轉化成為ASIC設計,從而成為一個SOC的嵌入式系統。

評論