數(shù)電模電基礎(chǔ)知識(shí)之搞懂?dāng)?shù)電技術(shù)

一、集成門電路

本文引用地址:http://www.104case.com/article/201808/384937.htm數(shù)字集成電路按其內(nèi)部有源器件的不同可以分為兩大類:一類為雙極型晶體管集成電路(TTL電路);另一類為單極型集成電路(MOS管組成的電路)。

1.TTL集成邏輯門電路

(1)TTL與非門

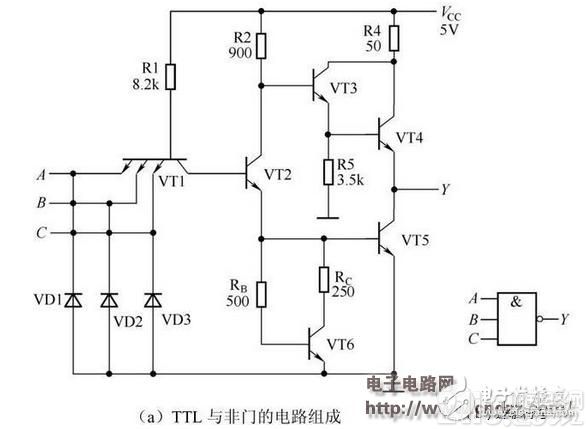

CT74S肖特基系列TTL與非門的電路組成如圖2-19(a)所示,它由輸入級(jí)、中間級(jí)、輸出級(jí)3個(gè)部分組成。

圖2-19 TTL與非門電路圖

輸入級(jí):由多發(fā)射極管VT1和電阻R1組成,多發(fā)射極管的3個(gè)發(fā)射結(jié)為3個(gè)PN結(jié)。其作用是對(duì)輸入變量A、B、C實(shí)現(xiàn)邏輯與,所以它相當(dāng)于一個(gè)與門。

中間級(jí):由VT2、R2和VT6、RB、RC組成,VT2集電極和發(fā)射極同時(shí)輸出兩個(gè)邏輯電平相反的信號(hào),用以驅(qū)動(dòng)VT3和VT5。

輸出級(jí):由VT3、VT4、VT5和R4、R5組成,它采用了達(dá)林頓結(jié)構(gòu),VT3和VT4組成復(fù)合管降低了輸出高電平時(shí)的輸出電阻,提高了帶負(fù)載能力。

TTL 與非門的邏輯符號(hào)如圖 2-19(b)所示;邏輯表達(dá)式為:

對(duì)圖2-19所示電路,如果高電平用1表示,低電平用0表示,則可列出圖2-19所示的真值表,如表2-1所示。

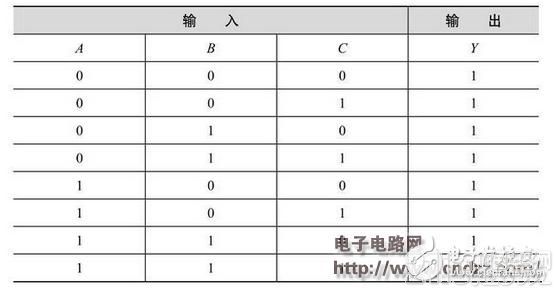

表2-1 TTL與非門真值表

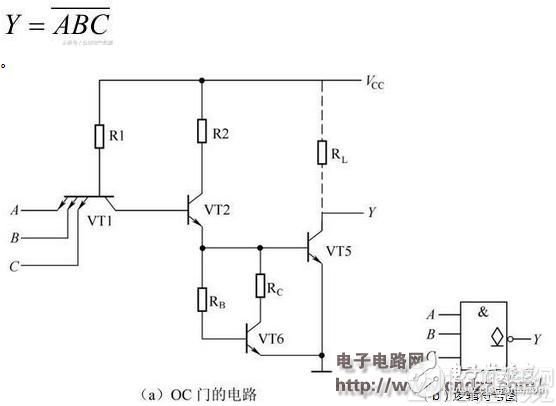

(2)集電極開路與非門(OC門)

① 工作原理。

集電極開路與非門也叫 OC 門,能使門電路輸出的電壓高于電路的高電平電壓值,且門電路的輸出端可以并聯(lián)以實(shí)現(xiàn)邏輯與功能,即線與(一般的TTL門電路不能線與)。

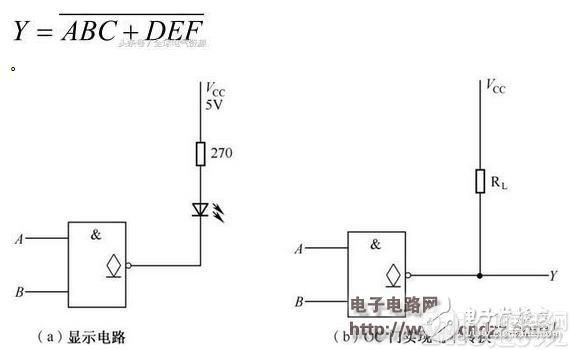

OC門的電路如圖2-20(a)所示,邏輯符號(hào)如圖2-20(b)所示,邏輯表達(dá)式為:

圖2-20 集電極開路與非門及邏輯符號(hào)

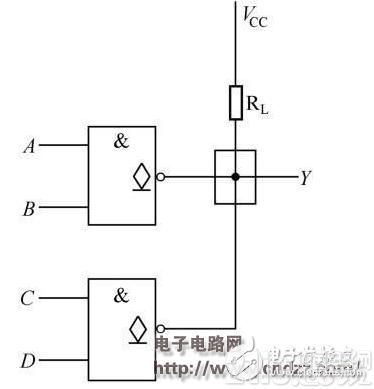

② OC 門的應(yīng)用。

OC門可以實(shí)現(xiàn)線與,如圖2-21所示,邏輯表達(dá)式為

;驅(qū)動(dòng)顯示器、實(shí)現(xiàn)電平轉(zhuǎn)換,如圖2-22所示。

圖2-21 用OC門實(shí)現(xiàn)線與

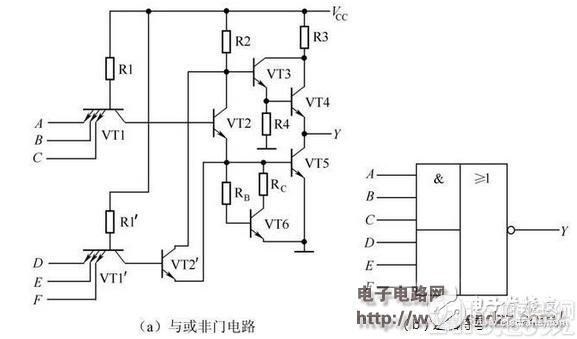

(3)與或非門

與或非門電路如圖2-23(a)所示,邏輯符號(hào)如圖2-23(b)所示,邏輯表達(dá)式為:

圖2-22 驅(qū)動(dòng)顯示器、實(shí)現(xiàn)電平轉(zhuǎn)換

圖2-23 與或非門及邏輯符號(hào)

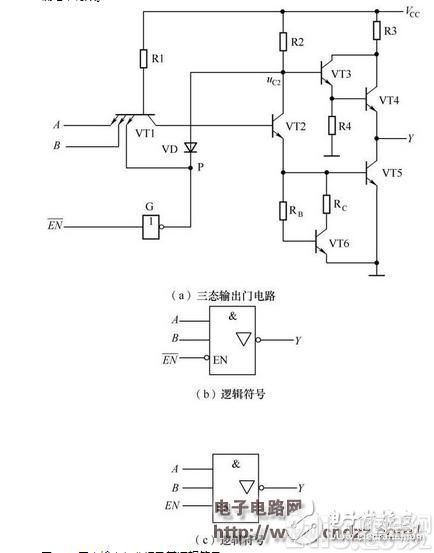

(4)三態(tài)輸出門

三態(tài)輸出門是指不僅可輸出高電平、低電平兩個(gè)狀態(tài),而且還可輸出高阻狀態(tài)的門電路,如圖2-24所示,

為控制端。

當(dāng)

=0時(shí),G輸出P=1,VD截止,輸出Y=

,三態(tài)門處于工作狀態(tài)。

低電平有效。

圖2-24 三態(tài)輸出與非門及其邏輯符號(hào)

當(dāng)

=1時(shí),G輸出P=0,VD導(dǎo)通,輸出高阻狀態(tài)。

2.CMOS集成邏輯門

和 TTL 數(shù)字集成電路相比,CMOS 電路的突出特點(diǎn)是微功耗、高抗干擾能力。

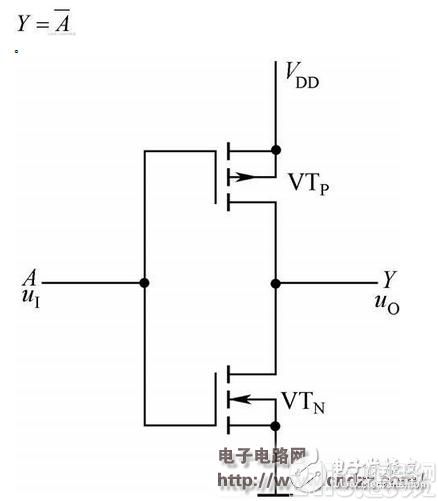

(1)CMOS反相器

由兩個(gè)場(chǎng)效應(yīng)管組成互補(bǔ)工作狀態(tài),如圖 2-25 所示。邏輯表達(dá)式為:

圖2-25 CMOS 反相器

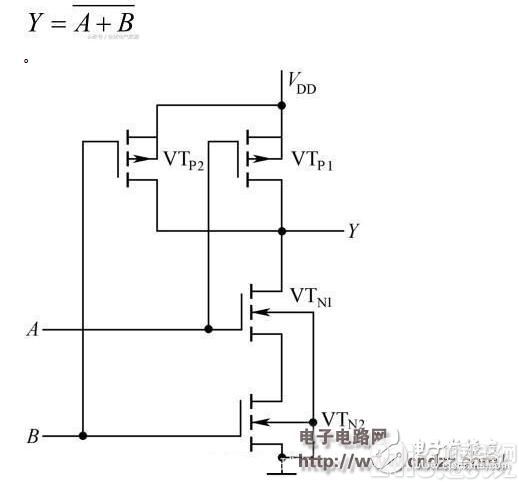

(2)CMOS與非門

如圖2-26所示,兩個(gè)串聯(lián)的增強(qiáng)型NMOS管VTN1和VTN2為驅(qū)動(dòng)管,兩個(gè)并聯(lián)的增強(qiáng)型PMOS管VTP1和VTP2為負(fù)載管,組成CMOS與非門,邏輯表達(dá)式為:

。

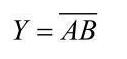

(3)CMOS或非門

如圖2-27所示,兩個(gè)并聯(lián)的增強(qiáng)型NMOS管VTN1和VTN2為驅(qū)動(dòng)管,兩個(gè)串聯(lián)的增強(qiáng)型PMOS管VTP1和VTP2為負(fù)載管,組成CMOS或非門,邏輯表達(dá)式為:

圖2-26 CMOS 與非門

圖2-27 CMOS 或非門

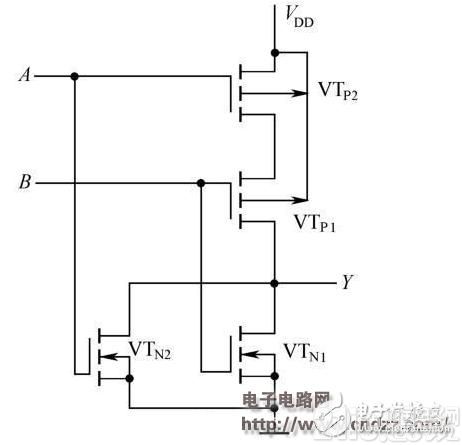

(4)CMOS傳輸門

將兩個(gè)參數(shù)對(duì)稱一致的增強(qiáng)型NMOS管VTN和PMOS管VTP并聯(lián)可構(gòu)成CMOS傳輸門,電路和邏輯符號(hào)如圖2-28所示。

圖2-28 CMOS 傳輸門及邏輯符號(hào)

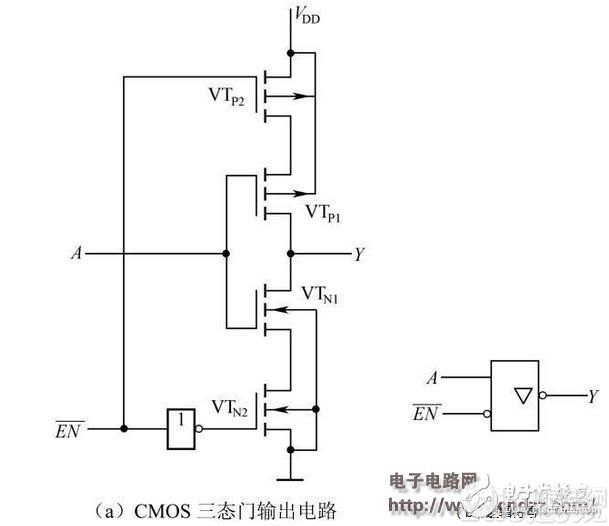

(5)CMOS三態(tài)門

圖 2-29(a)所示為低電平控制的三態(tài)門輸出,圖 2-29(b)為邏輯符號(hào)。

圖2-29 CMOS 三態(tài)門輸出及邏輯符號(hào)

當(dāng)

時(shí),VTP2和VTN2導(dǎo)通,VTN1和VTP1組成的CMOS反相器工作,所以

。

當(dāng)

,VTP2和VTN2同時(shí)截止,輸出Y對(duì)地和對(duì)電源VDD都呈高阻狀態(tài)。

評(píng)論