AHB總線協議

1. 簡介

本文引用地址:http://www.104case.com/article/201807/383796.htmAHB總線規范是AMBA總線規范的一部分,AMBA總線規范是ARM公司提出的總線規范,被大多數SoC設計采用,它規定了AHB (Advanced High-performance Bus)、ASB (Advanced System Bus)、APB (Advanced Peripheral Bus)。AHB用于高性能、高時鐘頻率的系統結構,典型的應用如ARM核與系統內部的高速RAM、NAND FLASH、DMA、Bridge的連接。APB用于連接外部設備,對性能要求不高,而考慮低功耗問題。ASB是AHB的一種替代方案。

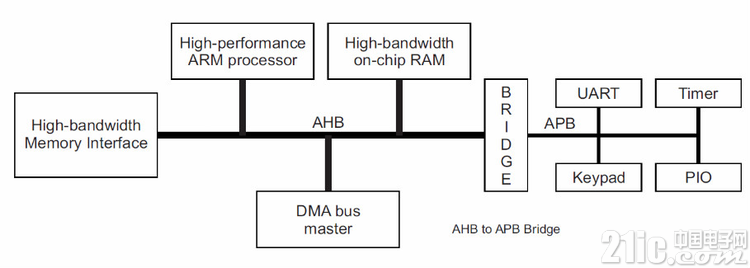

1.1 AHB總線的架構

AHB總線的強大之處在于它可以將微控制器(CPU)、高帶寬的片上RAM、高帶寬的外部存儲器接口、DMA總線master、各種擁有AHB接口的控制器等等連接起來構成一個獨立的完整的SOC系統,不僅如此,還可以通過AHB-APB橋來連接APB總線系統。AHB可以成為一個完整獨立的SOC芯片的骨架。

下圖是一個典型的AHB系統總線的結構示意圖

1.2 AHB基本特性

Burst傳輸

Split事務處理

單周期master移交

單一時鐘沿操作

無三態

更寬的數據總線配置(64/128)

流水線操作

可支持多個總線主設備(最多16個)

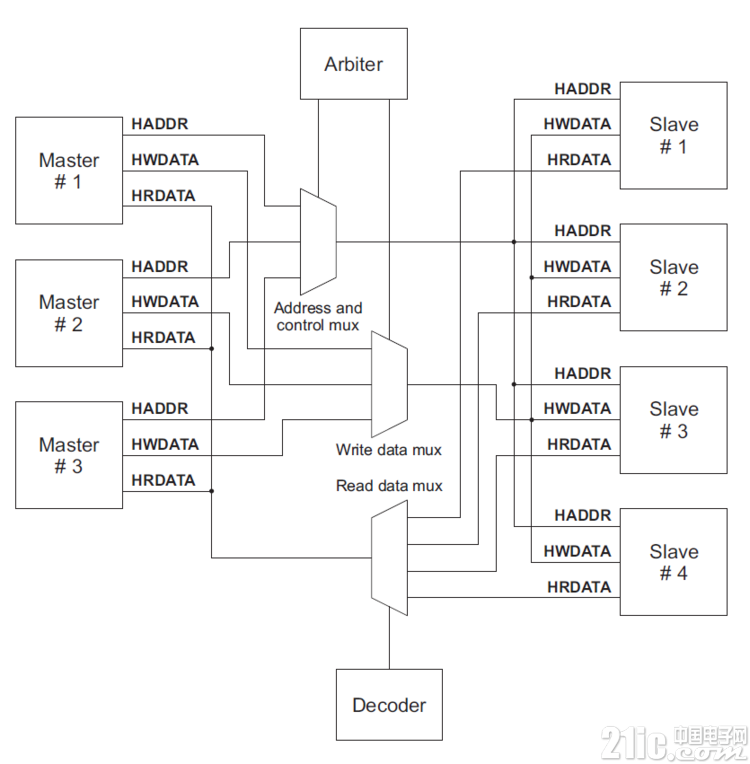

2. AHB總線的組成

AHB總線由Master、Slave和Infrastructure構成。Infrastructure由arbiter、數據多路、地址控制多路、譯碼器構成。

主設備Master

發起一次讀/寫操作

某一時刻只允許一個主設備使用總線

從設備Slave

響應一次讀/寫操作

通過地址映射來選擇使用哪一個從設備

仲裁器arbiter

允許某一個主設備控制總線

譯碼器decoder

通過地址譯碼決定選擇哪一個從設備

總線可以分為三組

寫數據總線(HWDATA)

讀數據總線(HRDATA)

地址控制總線(HADDR)

3. 信號描述

| Name | Source | To | Description |

| HCLK | clock source | 各module | 總線時鐘,上升沿采樣 |

| HRESETn | reset controller | 各module | 總線復位,低電平有效 |

| HADDR[31:0] | Master | decoder mux to slave arbiter | 32位系統地址總線 |

| HTRANS[1:0] | Master | mux to slave | 當前傳輸類型NONSEQ, SEQ, IDLE, BUSY |

| HWRITE | Master | mux to slave | 1為寫,0為讀 |

| HSIZE[2:0] | Master | mux to slave | 每一個transfer傳輸的數據大小,以字節為單位,最高支持1024位 |

| HBURST[2:0] | Master | mux to slave | burst類型,支持4、8、16 burst,incrementing/wrapping |

| HPROT[3:0] | Master | mux to slave | 保護控制信號,需要slave帶保護功能,一般不用 |

| HWDATA[31:0] | Master | mux to slave | 寫數據總線,Master到Slave |

| HRDATA[31:0] | Slave | mux to master | 讀數據總線,Slave到Master |

| HREADY | Slave | mux to master arbiter | 高:Slave指出傳輸結束 低:Slave需延長傳輸周期 |

| HRESP[1:0] | Slave | mux to master arbiter | Slave發給Master的總線傳輸狀態OKAY, ERROR, RETRY, SPLIT |

| HSELx | Decoder | slave | slave選擇信號 |

AHB仲裁信號

| Name | Source | To | Description |

| HBUSREQx | Master | arbiter | master給仲裁器的請求獲得總線使用權的請求信號,最多支持16個master |

| HLOCKx | Master | arbiter | 如果一個master希望自己在傳輸期間不希望丟掉總線,則需要向仲裁器發送這個鎖定信號 |

| HGRANTx | arbiter | master | 授權信號,當前bus master x的優先級最高。當HREADY和HGRANTx同時為高時,master獲取系統總線的權利 |

| HMASTER [3:0] | arbiter | 具有split功能的slave | 仲裁器為每一個master分配的ID,指出哪個主設備正在進行傳輸,提供進行split的信息 |

| HMASTLOCK | arbiter | 具有split功能的slave | 表示當前的master正在執行Locked操作。這個信號和HMASTER有這相同的時序 |

| HSPLITx[15:0] | slave | arbiter | 從設備用這個信號告訴仲裁器哪個主設備運行重新嘗試一次split傳輸,每一位對應一個主設備 |

4. 總線操作

有需要占用總線的Master向arbiter發出請求,arbiter授權給指定的master。任一時間周期只有一個master可以接入總線,對其指定的slave進行讀寫操作。

獲得授權的總線開始AHB傳輸,首先發出地址和控制信號,提供地址信息、傳輸方向、帶寬和burst類型。總線統一規劃slave的地址,譯碼器根據地址和控制信號確定哪個slave與master進行數據通信。數據傳輸通過數據總線完成。為避免出現三態總線,AHB將讀寫總線分開,寫數據總線用于從master到slave的數據傳輸,讀數據總線用于從slave到master的數據傳輸。每筆傳輸包括一個地址和控制周期,一個或多個數據周期。地址和控制周期不能被擴展,因此slave必須在一個周期內采樣地址信號。數據周期可以通過HREADY信號擴展,但HREADY為低時給傳輸加入一個等待狀態以使slave獲得額外的時間來提供或采樣數據,另外slave通過響應信號HRESP反映傳輸狀態。

一般情況下master完成完整的burst傳輸,arbiter才會授權給其他的master接入總線,然而為避免過大的判決延遲,arbiter也可能打斷burst傳輸。在這種情況下master必須再次接入總線以進行中斷的burst剩余部分的傳輸。

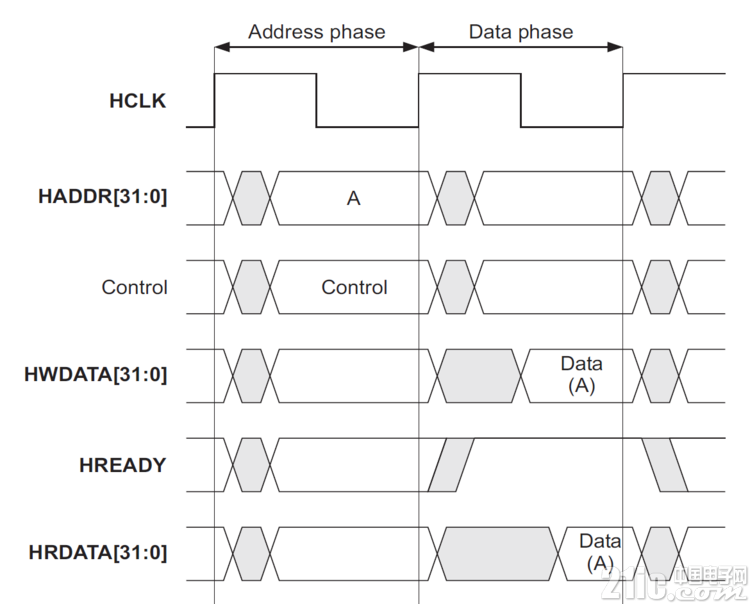

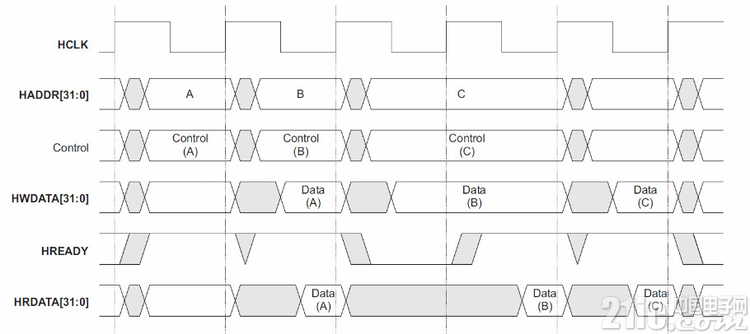

5. 基本傳輸

一筆傳輸由如下兩部分組成:

地址階段:一個周期

數據階段:一個或多個周期,由HBURST信號決定需要幾個有效周期,可以由HREADY發出請求延長一個周期。

5.1 沒有等待狀態的single transfer

第一個周期的上升沿,master驅動地址和控制信號;

第二個周期的上升沿,slave采樣地址和控制信號,并將HREADY拉高;

如果是寫操作,master會在第二個周期的上升沿傳輸要寫入的數據;

如果是讀操作,slave會在HREADY信號拉高后將讀取的數據寫入總線;

第三個周期的上升沿,

如果是寫操作,master獲取HREADY高信號,表明slave已成功接收數據,操作成功;

如果是讀操作,master獲取HREADY高信號,表明此時的讀數據有效并且接收下來,操作成功。

需要注意,HREADY信號在數據有效期間必須為高,并且延續到第三個周期的上升沿之后,確保master的正確采樣。

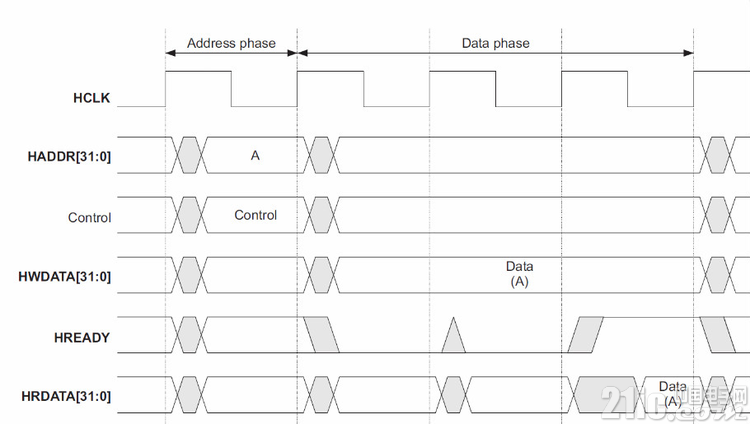

5.2 slave插入等待狀態的single transfer

slave可以及時處理master請求,但也可能存在slave太慢不能立即處理的情況。這時需要讓master稍微等一等,需要slave插入一些等待的狀態。如下圖所示,HREADY信號在第二和第三周期拉低,意在告訴master,slave不能立即處理,需要master等待2個周期。在這里需要注意2點:

如果是寫操作,master需要在等待期間保持寫數據不變,直到本次傳輸完成;

如果是讀操作,slave不需要一開始就給出數據,僅當HREADY拉高后才給出有效數據。

5.3 多個single transfer的pipeline操作

評論