千兆以太網MAC的FPGA實現與設計

作者 包海燕 孟歡 電子科技大學微電子與固體電子學院(四川 成都 610054)

本文引用地址:http://www.104case.com/article/201805/380765.htm包海燕(1993-),女,碩士生,研究方向:數字IC設計;孟歡,女,碩士生,研究方向:數字IC設計。

摘要:在數字系統互聯設計中,高速串行I/O技術取代傳統的并行I/O技術成為當前發展的趨勢,與傳統并行接口技術相比,串行方案提供了更大的帶寬、更遠的距離、更低的成本和更高的能力。以太網作為一種高速的串行傳輸方式,是當前最基本、最流行的局域網組網技術,為了適應各種新開展的業務如流視頻等,其速率也在不斷提高。GMII是標準的吉比特以太網接口,位于MAC層和物理層之間。因此,可以基于FPGA平臺,實現GMII接口協議,完成數據在MAC和物理層間的通信。

1 GMII接口協議簡介

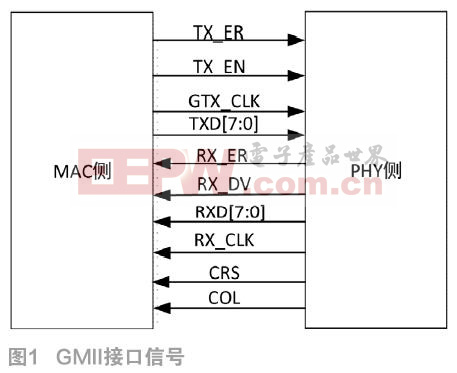

MII (Media Independent Interface(介質無關接口)或稱為媒體獨立接口,是IEEE-802.3定義的以太網行業標準。以太網中包括有一個數據接口以及一個MAC和PHY之間的管理接口[1]。數據接口包括兩條獨立的信道,這兩條信道分別用于發送和接收數據,它們都獨自擁有數據信號、時鐘信號以及控制信號。GMII是千兆以太網的MII的接口,該數據接口總共需要16個信號,接口信號如圖1所示。

GMII采用8位接口數據,工作時鐘125 MHz,因此傳輸速率可達1000 Mbps。同時兼容MII所規定的10/100 Mbps工作方式。MII接口主要分為四個部分,分別是MAC層到物理層的發送數據接口、物理層到MAC層的接收數據接口、物理層到MAC層的狀態指示接口、MAC層和物理層的控制和狀態信息接口(MDIO)。具體的信號說明如表1所示。

2 設計方案

Xilinx提供的千兆以太網開發套件為Virtex-5 ML505/ML506開發板,該開發板支持10/100 M、1/10 G以太網,是學習和研發高速連接設備的理想平臺。Xilinx提供了可參數化的10/1 Gbps以太網物理層控制器功能的LogiCORE解決方案[2]。該核設計用來同最新的Virtex-5、Virtex-4和Virtex-II Pro平臺FPGA一起工作,并可以無縫集成到Xilinx設計流程中。

以太網系統的兩個主要模塊是媒體接入控制(MAC)和物理層PHY,MAC由數據拆裝和媒體訪問管理兩個模塊組成,完成數據幀的封裝、解封、發送和接收功能。PHY對發送的數據按照物理層的編碼規則將數據編碼,再進行數模轉換變成模擬信號把數據送出去。接收數據則與之相反。

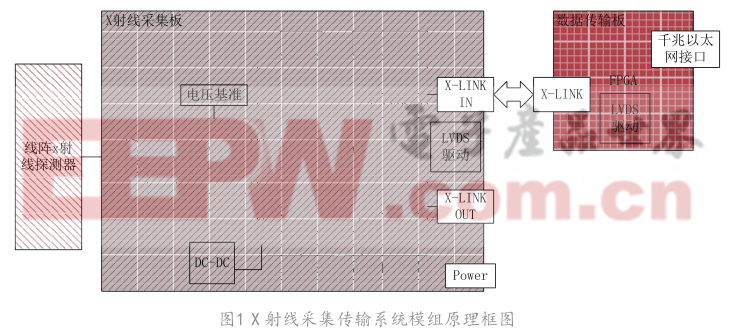

2.1 電路架構

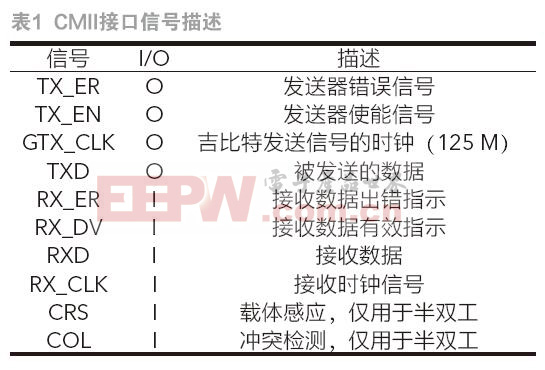

該以太網控制器主要進行MAC子層、MAC層與上層協議的接口以及MAC層與PHY接口的GMII的FPGA設計,總體結構框圖如圖2所示。整個系統分為待發送數據的產生模塊、發送模塊、CRC編碼生成模塊、物理層編解碼模塊、接收及校驗模塊、GMII管理模塊等部分。發送模塊和接收模塊主要提供MAC幀的發送和接收功能,其主要操作有MAC幀的封裝與解包以及錯誤檢測,它直接提供了到外部物理層芯片的并行數據接口[3]。在實現中物理層處理直接利用商用的千兆PHY芯片,在仿真過程中利用物理層IP_CORE來實現,所以本文重要關注在MAC控制器的開發上。

2.2 MAC協議介紹

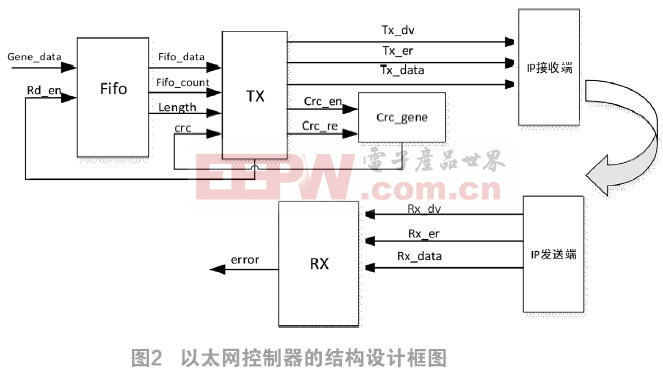

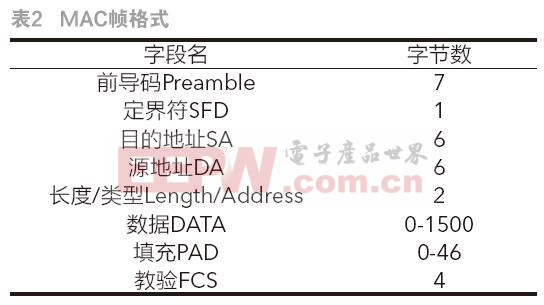

MAC控制模塊是由數據拆裝和媒體訪問管理兩個模塊組成,完成數據幀的封裝、解封、發送和接收功能。幀格式如表2所示。

前導碼的作用是讓物理層信號與接收幀時序達到永久同步。長度類型表明后面發送數據的長度,當實際數據的長度不夠時,需要補0填充。類型0X0800代表IP協議數據,16進制0x809b代表Appletalk協議數據等,本文發送的是IP協議數據。幀結尾的數據是根據CRC電路計算生成的校驗碼。

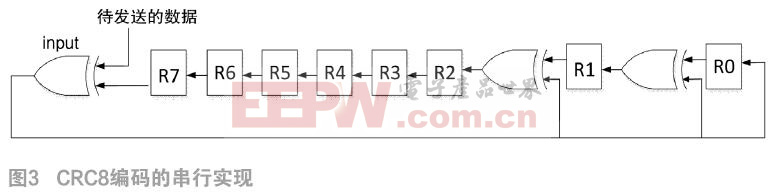

2.3 以太網的FCS處理

校驗位的FCS即為循環冗余碼CRC,它的編碼詳細過程是,根據數據流M的長度和特性,選擇長度為n次的特征多項式,在數據流M之后添加n個0,作為被除數除以由特征多項式構成的(n+1)bit的二進制數列P,得到商Q以及除數R,除數R為n bit,將R作為冗余碼添加在M之后發送出去。Crc8編碼的串行算法實現電路如圖3所示[4]:

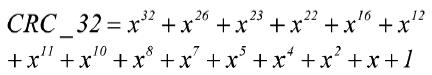

編碼前先將所有寄存器初始化,之后將待發送的信息序列依次在input端輸入編碼器,信息序列全部輸入之后,寄存器中的值就是所要求的余數,即CRC校驗碼。本文使用的是crc32多項式,多項式的表達式如下所示,需要編碼的數據段從目的字段開始到數據字段結束,利用同樣的類似的電路,即可利用verilog實現冗余碼編碼。

3 電路實現與仿真

3.1 MAC發送端-數據成幀

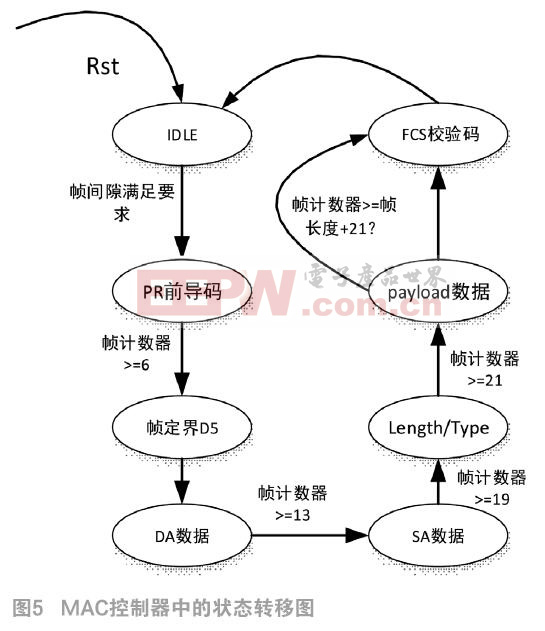

以太網的發送方式是按照一個幀一個幀來發送的,網絡設備和組件在接收一個幀以后,需要一段短暫的時間來恢復并為接收下一幀做準備。幀間隙是幀與幀之間需要的時間余量,以太網的最小幀間隙為96 bit(12 byte)。所以在開始發送時,要判斷是否滿足幀間隙。根據GMII接口的傳輸時序如圖4,設計圖5所示的狀態機,通過對每個狀態中,對字節進行計數實現狀態的跳轉。

在數據傳輸過程中,MAC發送模塊將上層協議需要發送的數據經過以太網協議進行封裝將數據發送給PHY層,發送模塊還可將從主機接收到的幀頭以及幀尾標志信號,與主機接口從外部存儲單元獲取的發送數據按照標準協議進行封裝,將數據以8位數據寬度的格式在信道空閑時發送給PHY層,再通過PHY芯片將數據進行數模轉換發送到網絡中去。

在物理層部分,利用ISE平臺生成Etherent 1000 BASE-X PCS/PMA IP CORE來接收MAC層的數據,該核支持內部或外部GMII,可實現與MAC或定制邏輯的鏈接。IP核內的主要組成部分為PMA和PCS,其中PMA為物理層的媒介層,PCS為物理層編碼模塊,可以進行8 B/10 B編解碼,64 B/66 B編解碼,COMMA字符檢測,將接收的數據對齊到合適的字邊界,偽隨機序列的生成和檢測,時鐘修正和通道綁定等[5]。

3.2 MAC接收端-數據提取

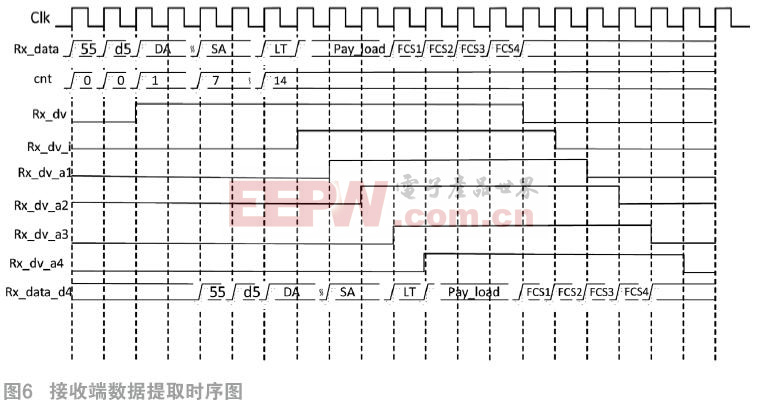

MAC端接收到傳回的數據后,需要對接收到的數據進行檢測,首先提取出pay_load數據和冗余檢驗碼crc_cmp。當發送數據包的長度不確定時,不能通過計數器來提取對應的數據和校驗碼,可行的操作如圖6的時序圖所示。

在接收端如果檢測到前導碼的第一個字節55時,計數器開始計數,當計數到14時,下一個時鐘,便是發送來的實際數據,產生Rx_dv_i信號,直到接收到四個字節的校驗碼時拉低,并將Rx_dv_i延遲四拍得到Rx_dv_a4信號,同時將Rx_data也延遲四拍,則在Rx_dv為高電平且Rx_dv_a4為高電平,取Rx_data_d4上的數據,即為pay_load數據,在Rx_dv為低電平,Rx_dv_a3為高電平時,Rx_data_a4為校驗碼。采用這種方案,在不確發送數據的個數情況下,可以分別提取出pay_load數據和fcs校驗碼數據。

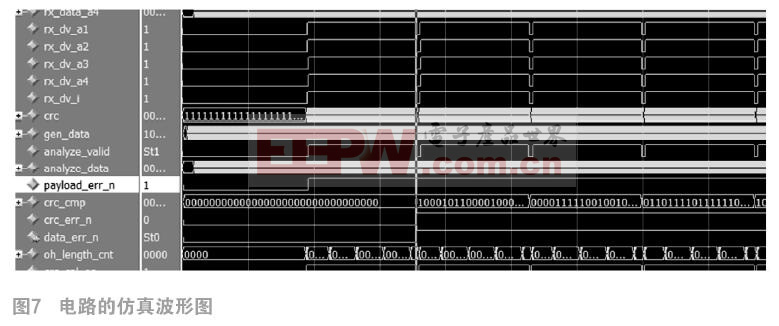

3.3 電路功能仿真

提取到相應的數據后,先將發送端的數據和接收到的數據進行比較,如果不同,產生data_error信號的低電平,指示出錯,同時將接收到的數據送入CRC編碼電路,來產生校驗碼rx_crc,將發送端的校驗碼crc_cmp與rx_crc進行比較,如果不同,產生crc_error的低電平信號。最終電路的錯誤指示信號error由data_error和crc_error相與產生。

設計完成以后,利用modelsim軟件對電路進行了仿真,仿真波形如圖7所示:可以看到三個錯誤標志信號error,在開始工作后均為高電平,表明該電路成功完成了在MAC和PHY之間的數據傳輸。

4 結論

高速串行傳輸技術是FPGA未來的三大應用領域之一,本文從以太網傳輸的總體結構和基本協議出發,設計了千兆以太網傳輸系統的方案,以MAC+PHY為核心,完成了網絡架構中物理層和數據鏈路層的基本功能。通過仿真驗證了數據在數據鏈路層和物理層之間準確無誤的傳輸,穩定性好,靈活性高,本系統還可以用來傳輸圖像和大數據信息。

參考文獻:

[1]曹云鵬.以太網MAC層協議研究與FPGA實現[D].蘭州:蘭州大學,2011.

[2]王春華.Xilinx可編程邏輯器件設計與開發(基礎篇).[M]北京:人民郵電出版社,2011.

[3]劉民.嵌入式千兆以太網絡圖像傳輸系統設計[D].大連:大連理工大學,2012.

[4]陳玉泉.一種并行CRC算法的實現方法[P].廈門:廈門大學,2005.

[5]王長清.基于FPGA的千兆以太網通信板卡的設計與實現[D].河南:河南師范學報,2011.

本文來源于《電子產品世界》2018年第6期第67頁,歡迎您寫論文時引用,并注明出處。

評論