手把手教你如何選擇合適的微控制器?

系統(tǒng)性能并不等價(jià)于計(jì)算能力。較低的功耗、豐富的片內(nèi)外設(shè)以及實(shí)時(shí)的信號(hào)處理能力對(duì)于大部分嵌入式應(yīng)用來(lái)說(shuō)是最為重要的。傳統(tǒng)的8位、16位單片機(jī)已經(jīng)很好的處理了這類(lèi)問(wèn)題,但是隨著當(dāng)今嵌入式設(shè)計(jì)不斷增長(zhǎng)的功能需求和特殊要求,許多微控制器廠商開(kāi)始拋棄他們傳統(tǒng)的8位、16位單片機(jī)。但是選擇32位處理器對(duì)于某些任務(wù)來(lái)可能并不是最適宜的。下面我們就討論一下單片機(jī)的選型問(wèn)題。

理解系統(tǒng)性能

MIPS(million instructions per second),是微控制器計(jì)算能力的表征。但是,所有的嵌入式應(yīng)用不僅僅是需要計(jì)算能力,所以應(yīng)用的多樣化決定了系統(tǒng)性能衡量方式的多樣化,大部分參數(shù)都同等重要并且難于用一個(gè)參數(shù)來(lái)表示,我們并不應(yīng)該僅僅從MIPS就判定系統(tǒng)的好壞。也許某一應(yīng)用由于成本的限制,需要一款高集成度的微控制器,該控制器需要多個(gè)定時(shí)器和多種接口。但是另一個(gè)應(yīng)用需要高的精度和快速的模擬轉(zhuǎn)換能力。兩者的共同點(diǎn)可能僅僅是供電部分,比如采用電池供電。對(duì)于一個(gè)實(shí)時(shí)的順序處理應(yīng)用來(lái)說(shuō),通信的失敗可能會(huì)導(dǎo)致災(zāi)難性后果。這樣的場(chǎng)合下就需要一個(gè)靈巧的控制器。這個(gè)控制器應(yīng)當(dāng)能夠以正確的順序處理任務(wù),并且響應(yīng)時(shí)間必須均衡。所有上述應(yīng)用的共同問(wèn)題可能就是定期的現(xiàn)場(chǎng)升級(jí)能力。

除了與具體的產(chǎn)品要求有關(guān)外,系統(tǒng)性能的衡量也可以考慮是否有容易上手、容易使用的開(kāi)發(fā)工具、應(yīng)用示例、齊全的文檔和高效的支持網(wǎng)絡(luò)。

系統(tǒng)性能的相關(guān)問(wèn)題

1.傳統(tǒng)8位單片機(jī)的局限

大多數(shù)工程師十分關(guān)注系統(tǒng)性能,因?yàn)樵絹?lái)越多的8位和16位單片機(jī)家族已經(jīng)無(wú)法滿足當(dāng)今日益增長(zhǎng)的需求。陳舊和低效的架構(gòu)限制了處理能力、存儲(chǔ)器容量、外設(shè)處理和低功耗要求。8位的處理器架構(gòu),比如8051、PIC14、PIC16、PIC18、78K0和HC08是在高級(jí)語(yǔ)言(比如C語(yǔ)言)出現(xiàn)之前開(kāi)發(fā)的,其指令集僅用于匯編開(kāi)發(fā)環(huán)境。并且這類(lèi)架構(gòu)的中央處理單元(CPUs)缺乏一些關(guān)鍵功能,比如16位的算數(shù)運(yùn)算支持、條件跳轉(zhuǎn)和存儲(chǔ)器指針。

許多CPU架構(gòu)執(zhí)行一條指令需要若干時(shí)鐘周期。Microchip的8位PIC家族執(zhí)行一條最簡(jiǎn)單的指令需要4個(gè)時(shí)鐘周期,這導(dǎo)致使用20M的時(shí)鐘僅能達(dá)到5MIPS.對(duì)于其他CPU架構(gòu),比如8051內(nèi)核。其執(zhí)行一條指令至少需要6個(gè)時(shí)鐘周期,這就使得實(shí)際的MIPS要比給定的時(shí)鐘頻率低很多。

int max(int *array)

{

char a;

int maximum=-32768;

for (a=0;amaximum)

maximum=array[a];

return (maximum);

}

上述代碼是一個(gè)簡(jiǎn)單的C語(yǔ)言函數(shù),表1列出了在三種不同CPU架構(gòu)上編譯這段代碼的相應(yīng)結(jié)果。8051內(nèi)核的執(zhí)行時(shí)間幾乎是PIC16內(nèi)核的4倍,對(duì)于AVR架構(gòu)更是達(dá)到了28倍。

表1不同CPU架構(gòu)的代碼容量和執(zhí)行時(shí)間

一些半導(dǎo)體廠商解決了時(shí)鐘分配問(wèn)題,使得微控制器實(shí)現(xiàn)了單時(shí)鐘周期指令。當(dāng)時(shí)鐘頻率為100MHz時(shí),Silicon Labs聲稱他們基于8位8051架構(gòu)的微控制器能夠達(dá)到100MIPS的峰值。但是,這里有幾個(gè)問(wèn)題:

第一,由于大部分指令需要兩個(gè)時(shí)鐘周期甚至更多,所以其實(shí)際能力接近于50MIPS;

第二,8051是基于累加器的CPU,所有需要計(jì)算的數(shù)據(jù)必須拷貝到累加器。查看8051處理器的匯編代碼,可以發(fā)現(xiàn)65%-70%的指令用來(lái)移動(dòng)數(shù)據(jù)。由于現(xiàn)代8位和16位單片機(jī)架構(gòu)中有一系列和算術(shù)邏輯單元(ALU)相連的寄存器。因此,8051內(nèi)核的50MIPS僅相當(dāng)于現(xiàn)代8位和16位單片機(jī)架構(gòu)的15MIPS。

MOV A,0x82

ADD A,R1

MOV 0x82,A

MOV A,0x83

ADDC A,R2

MOV 0x83,A

MOVX A,@DPTR

MOV OxF0,A

INC DPTR

MOVX A,@DPTR

RET

第三,較老的CPU架構(gòu)缺乏對(duì)大容量存儲(chǔ)器的支持。早在七十年代,很難想象需要超過(guò)64KB存儲(chǔ)器的嵌入式應(yīng)用,這使得許多CPU設(shè)計(jì)師選擇16位的地址總線。因此,CPU、寄存器、指令集以及程序存儲(chǔ)器和數(shù)據(jù)存儲(chǔ)器的數(shù)據(jù)總線始終受此限制。

第四,在2006年,約有9%的8位嵌入式應(yīng)用使用了64KB甚至更多的程序存儲(chǔ)空間,這代表了8位MCU市場(chǎng)26%的收益。推測(cè)2009年,14%的8位嵌入式應(yīng)用會(huì)代表36%的收益。而這14%的應(yīng)用會(huì)使用64KB甚至更多的程序存儲(chǔ)空間。

從系統(tǒng)性能的角度來(lái)看,所有這些使得較舊的8位MCU逐漸失去競(jìng)爭(zhēng)力。

2.不適宜32位處理器的場(chǎng)合

舊式CPU架構(gòu)無(wú)法滿足當(dāng)今的市場(chǎng)需求,為了解決這個(gè)問(wèn)題,許多廠商升級(jí)至32位的處理平臺(tái)。對(duì)于需要32位處理能力的應(yīng)用來(lái)說(shuō)這無(wú)疑是最棒的選擇,但是許多設(shè)計(jì)師轉(zhuǎn)換到32位平臺(tái)并非最正確的選擇。使用32位MCU來(lái)解決8位和16位單片機(jī)的自身限制將會(huì)導(dǎo)致過(guò)高的成本。

大部分32位微控制器無(wú)法提供高速、高分辨率的模數(shù)(ADC)轉(zhuǎn)換,EMC性能通常較低,且ESD保護(hù)較弱。而8位和16位單片機(jī)在這些方面優(yōu)勢(shì)明顯。另外,強(qiáng)的IO驅(qū)動(dòng)能力,可供選擇的多種內(nèi)部、外部振蕩器,無(wú)需外部器件的片內(nèi)電壓調(diào)整器等是8位和16位單片機(jī)的另一些優(yōu)點(diǎn)。

顯然,32位CPU包含比任何8位和16位CPU都要多的數(shù)字邏輯單元,這導(dǎo)致了高的制造成本。雖然使用一些特殊的半導(dǎo)體工藝可以降低成本,但是弊端是會(huì)導(dǎo)致較高的漏電流和靜態(tài)功耗。某些應(yīng)用,像水表、燃?xì)獗怼⑹召M(fèi)公路電子標(biāo)簽、安全系統(tǒng)等,在他們生命期中的大部分時(shí)間,CPU處于睡眠模式,即為停止?fàn)顟B(tài)。這類(lèi)應(yīng)用的電池壽命必須在5-10年,所以這情況中,不可能將CPU從8位或者16位升級(jí)至32位處理器。如果想要提升系統(tǒng)性能只有采用別的方法。

保持采用統(tǒng)一產(chǎn)品線

生產(chǎn)商會(huì)定期生產(chǎn)新的嵌入式產(chǎn)品擴(kuò)展產(chǎn)品線以保持競(jìng)爭(zhēng)力。這些新產(chǎn)品通常是完善需求、升級(jí)性能或者降低成本。其他因素還包括制造工藝升級(jí)、提升競(jìng)爭(zhēng)力和市場(chǎng)發(fā)展趨勢(shì)。獨(dú)立于最先的設(shè)想,新產(chǎn)品總是基于一些核心思想。因此,新的產(chǎn)品或者升級(jí)版本會(huì)依賴于已經(jīng)存在的平臺(tái)和源代碼。

研究表明,半數(shù)公司潛在重用已有硬件和軟件以減少開(kāi)發(fā)時(shí)間。工程師對(duì)特定MCU產(chǎn)品家族的了解程度、相關(guān)MCU的開(kāi)發(fā)文檔是否詳細(xì)以及是否具有高效的開(kāi)發(fā)工具也是降低開(kāi)發(fā)時(shí)間和成本的重要因素。

保護(hù)知識(shí)產(chǎn)權(quán)和處理保密信息

一些嵌入式應(yīng)用用來(lái)處理個(gè)人信息。另一些授權(quán)訪問(wèn)受限區(qū)域或者金融領(lǐng)域。幾乎所有的微控制器都在運(yùn)行具有產(chǎn)權(quán)的程序。如果相關(guān)軟件被破解,甚至克隆產(chǎn)品在市場(chǎng)流通,知識(shí)產(chǎn)權(quán)的所有人可能會(huì)失去未來(lái)的收益。正是由于這個(gè)原因,大部分微控制器都有保護(hù)機(jī)制。這種機(jī)制可以阻止黑客或者第三方使用編程器、調(diào)試器或者測(cè)試接口來(lái)讀出程序存儲(chǔ)器。

當(dāng)今,越來(lái)越多的應(yīng)用采用層次設(shè)計(jì)或者功能模塊設(shè)計(jì)。不同功能模塊或者部件之間的有線通信或者無(wú)線通信成為一個(gè)越發(fā)困難和值得注意的問(wèn)題。為了阻止第三方的非法訪問(wèn),必須進(jìn)行加密。這方面的一個(gè)例子就是遙控車(chē)門(mén)開(kāi)關(guān)(Remote Keyless Entry, RKE)或者家庭無(wú)線網(wǎng)絡(luò)。如果傳輸?shù)臄?shù)據(jù)沒(méi)有加密,那任何人都有可能使用您的車(chē)或使用您的無(wú)線互聯(lián)網(wǎng)連接。傳統(tǒng)的解決方法是使用封閉算法或者加密算法,這樣只有知道算法的人可以使用。這樣的方法被稱為通過(guò)隱匿來(lái)實(shí)現(xiàn)安全(security by obscurity),這是一種非常危險(xiǎn)的做法。最佳的解決方法是使用諸如AES或者DES這類(lèi)的公開(kāi)算法,這類(lèi)算法既允許公眾查閱又可以保障他們的安全。如果你使用私密加密算法或者匿名加密算法,則無(wú)法*估安全級(jí)別或者發(fā)現(xiàn)關(guān)鍵的設(shè)計(jì)缺陷。

使用公開(kāi)加密協(xié)議的問(wèn)題是需要強(qiáng)大的運(yùn)算能力和可靠的算法設(shè)計(jì)。在現(xiàn)代8位MCU上使用DES算法加密或者解密一個(gè)8字節(jié)的塊所需時(shí)間的典型值是大約10 萬(wàn)個(gè)時(shí)鐘周期。這相當(dāng)于使用全部的15MIPS來(lái)支持9600Kbps的通信速度。而32位CPU進(jìn)行同樣的運(yùn)算通常會(huì)快50%-60%.在32MHz系統(tǒng)時(shí)鐘下,使用45000周期或1.4毫秒只能以45 kbps的速度進(jìn)行安全數(shù)據(jù)通信,因?yàn)樗械腃PU時(shí)間都用于加密和解密。顯然,系統(tǒng)沒(méi)有多少時(shí)間可以留給實(shí)際的應(yīng)用程序。其次,大多數(shù)的無(wú)線應(yīng)用是電池驅(qū)動(dòng)的,如果大多數(shù)處理能力都用在安全方面,將縮短電池壽命。

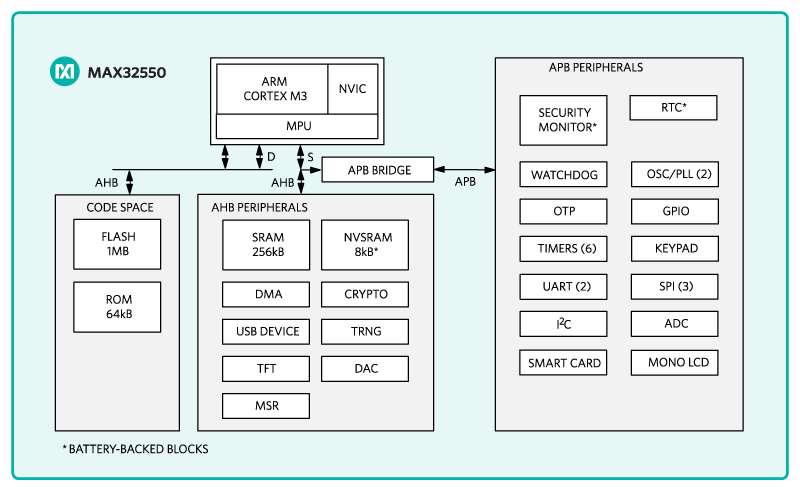

高集成度與中斷延時(shí)和安全

現(xiàn)在的微控制器在其片內(nèi)集成了越來(lái)越多的外設(shè)。通常來(lái)說(shuō),外設(shè)對(duì)微控制器高效的完成工作起著至關(guān)重要的作用。外設(shè)起著連接傳感器、系統(tǒng)控制、數(shù)據(jù)通信、故障控制和計(jì)時(shí)等多種作用。傳統(tǒng)方法是使用中斷來(lái)與片內(nèi)外設(shè)通信。這樣的優(yōu)勢(shì)很明顯,大大的節(jié)約CPU時(shí)間,使得軟件不必循環(huán)檢測(cè)外設(shè)狀態(tài),從而本質(zhì)上提高了CPU的效率。即使如此,中斷方式仍然有一些劣勢(shì),其中一個(gè)就是中斷例程中的上下文切換要花費(fèi)一些處理周期。對(duì)于現(xiàn)代的CPU架構(gòu)來(lái)說(shuō),中斷的上下文切換需要20-100個(gè)時(shí)鐘周期。假設(shè)有一個(gè)簡(jiǎn)單的任務(wù),它獲取發(fā)來(lái)的SPI數(shù)據(jù)。如果SPI的速率是1Mbps,則SPI接收中斷的頻率可達(dá) 125KHz.如果SPI中斷處理需要25時(shí)鐘周期(包括上下文切換),那對(duì)于20MIPS的CPU時(shí)間來(lái)說(shuō),僅處理SPI中斷就需要花費(fèi)15%的CPU 時(shí)間。如果同時(shí)還有其他一系列中斷,則意味著CPU必須處理巨大的任務(wù)。

使用中斷方式的另一個(gè)劣勢(shì)就是中斷響應(yīng)時(shí)間對(duì)關(guān)鍵系統(tǒng)事件的影響。某些中斷源可能要求在觸發(fā)后CPU必須立即響應(yīng)。比如汽車(chē)的安全氣囊、動(dòng)力設(shè)備的急停等危機(jī)情況以及緊急情況的應(yīng)用。所有這些都要求立即相應(yīng),或者立即關(guān)閉控制系統(tǒng)以防止發(fā)生永久性災(zāi)難事件。如果CPU需要首先完成其他的中斷服務(wù)程序或者需要花費(fèi)較長(zhǎng)的時(shí)間進(jìn)行上下文切換,結(jié)果將無(wú)法預(yù)知。

目前,已經(jīng)有些半導(dǎo)體廠商開(kāi)發(fā)了一些新的技術(shù)。這些技術(shù)用來(lái)取代傳統(tǒng)的中斷方式或者DMA方式,使用這類(lèi)技術(shù)進(jìn)行外設(shè)通信可以節(jié)省大量的CPU時(shí)間。

評(píng)論