通過將SystemC和SystemVerilog集成在單個(gè)環(huán)境中獲得事務(wù)級建模和高級驗(yàn)證功能

通過支持面向?qū)ο蟮木幊谭椒ǎ@兩種語言都能對更高層的抽象進(jìn)行建模,而且都包含象隨機(jī)化這樣的驗(yàn)證組件。兩者之間也有些區(qū)別。例如SystemC完全支持TLM,包括在高層抽象進(jìn)行描述、記錄和事務(wù)瀏覽;而SystemVerilog不完全支持TLM,但它支持聲明、功能覆蓋和改進(jìn)的受限隨機(jī)測試生成功能,因此也具有顯著的驗(yàn)證優(yōu)勢。這兩種語言在功能上多少有些重疊,因此用這兩種語言建立系統(tǒng)時(shí)可以做到平滑轉(zhuǎn)換。

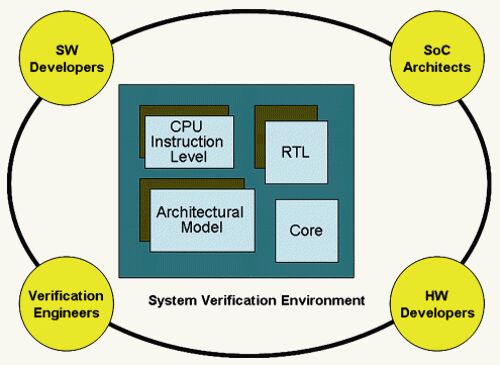

可以在多個(gè)抽象層實(shí)現(xiàn)的高級驗(yàn)證方法和建模技術(shù)能夠最佳地發(fā)揮TLM的優(yōu)勢。事務(wù)常用于建模硬件系統(tǒng),而系統(tǒng)軟件的語義很容易被表示為高層事務(wù)。這樣系統(tǒng)架構(gòu)師、軟件、驗(yàn)證和硬件工程師之間就能直接進(jìn)行交流。更高層抽象和TLM可以使大量軟件被用作測試平臺的一部分,并允許在RTL編碼完成之前開始測試平臺開發(fā)。當(dāng)RTL設(shè)計(jì)實(shí)現(xiàn)時(shí),驗(yàn)證工程師就可以插入將RTL事務(wù)轉(zhuǎn)換成信號層事務(wù)的事務(wù)處理器。

另外,設(shè)計(jì)領(lǐng)域和學(xué)科之間的這種高性能橋梁可以改善公司各個(gè)設(shè)計(jì)與驗(yàn)證團(tuán)隊(duì)的所有成員之間的交流和合作。它允許軟件工程師和系統(tǒng)架構(gòu)師與驗(yàn)證和硬件工程師直接分享數(shù)據(jù)。這種交叉學(xué)科交流本身也有助于發(fā)現(xiàn)和解決設(shè)計(jì)過程早期出現(xiàn)的問題,從而進(jìn)一步提高設(shè)計(jì)質(zhì)量和驗(yàn)證的產(chǎn)能。

圖1:在多個(gè)抽象層工作并使用高級驗(yàn)證方法可以為系統(tǒng)級平臺的建立提供極好的機(jī)會,此時(shí)驗(yàn)證復(fù)雜SoC所需的多學(xué)科匯聚要比以前早得多。

標(biāo)準(zhǔn)集成可進(jìn)一步方便高級驗(yàn)證

設(shè)計(jì)復(fù)雜性意味著驗(yàn)證小組必須能夠產(chǎn)生更多冗余度更少的測試,以便更快地覆蓋目標(biāo)性能。最佳的驗(yàn)證解決方案可以幫助工程師利用高級驗(yàn)證技術(shù)和方法實(shí)現(xiàn)更高的驗(yàn)證產(chǎn)能,例如基于聲明的驗(yàn)證、受約束的隨機(jī)測試、功能覆蓋和測試平臺自動化。

這些方法已被一些前沿設(shè)計(jì)公司所采用,其中大多數(shù)設(shè)計(jì)公司開發(fā)私有工具來支持這些方法。這些私有工具被證明可以增加驗(yàn)證效率和產(chǎn)能,并能提高設(shè)計(jì)質(zhì)量。然而,私有特性也阻礙了這些工具的廣泛采納。通常這些定制語言的集成以及獨(dú)立內(nèi)核和專用接口的整合限制被證明是相當(dāng)困難的。

克服這些障礙的第一步是由公認(rèn)的標(biāo)準(zhǔn)組織如OSCI、Accellera和IEEE開發(fā)出標(biāo)準(zhǔn)的驗(yàn)證語言和庫。這些新語言也必須克服其它HDL語言的設(shè)計(jì)與驗(yàn)證限制,因?yàn)檫@些HDL語言缺少對更高層抽象的驗(yàn)證支持。第二步是提供能夠全面支持在單個(gè)內(nèi)核和用戶接口中集成這些語言的仿真環(huán)境。這種語言的集成可以從根本上改變高級驗(yàn)證方法的部署,使之最佳匹配項(xiàng)目需要,而不受語言或工具的限制。

SystemVerilog和SystemC是適合高級設(shè)計(jì)與驗(yàn)證使用的最重要語言。SystemVerilog和SystemC設(shè)計(jì)構(gòu)造允許在更高抽象層進(jìn)行建模,從而有利于下一代設(shè)計(jì)的創(chuàng)建與驗(yàn)證。

SystemVerilog是許多現(xiàn)成的專有和標(biāo)準(zhǔn)驗(yàn)證與設(shè)計(jì)語言積累的結(jié)果,因此它能與現(xiàn)有的HDL環(huán)境無縫集成。SystemVerilog可以加快高級功能驗(yàn)證的構(gòu)建,實(shí)現(xiàn)缺陷檢測的自動化和設(shè)計(jì)的完全覆蓋,包括難以預(yù)料的偏僻案例。它能改善建模質(zhì)量,使之具有更好的可視性和更少的缺陷,并且能夠通過支持受限隨機(jī)測試、自動化、聲明、覆蓋和測試平臺復(fù)用改善測試平臺架構(gòu)的質(zhì)量。

SystemC能讓工程師在更高抽象層捕獲設(shè)計(jì),并使用包括軟件在內(nèi)的高層測試策略執(zhí)行驗(yàn)證。系統(tǒng)級測試平臺也可以在RTL級復(fù)用,實(shí)現(xiàn)驗(yàn)證產(chǎn)能的提高。SystemC包括一個(gè)功能強(qiáng)大的并發(fā)建模層,非常方便創(chuàng)建無時(shí)序、并發(fā)的系統(tǒng)級架構(gòu)模型。因?yàn)镾ystemC是C++的擴(kuò)展,因此它有許多固有屬性,如類、模板和多種繼承性,這些屬性自己就能建立適合功能驗(yàn)證的可復(fù)用事務(wù)級組件。用于開發(fā)軟件的同一可執(zhí)行平臺常被用于整個(gè)系統(tǒng)的驗(yàn)證。這種驗(yàn)證在項(xiàng)目初期就會發(fā)生,而事務(wù)級模型可以成為整個(gè)系統(tǒng)非常好的參考。

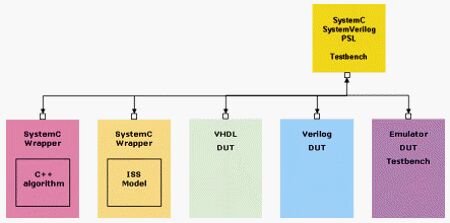

一個(gè)全面集成的多語言仿真環(huán)境允許用SystemVerilog或SystemC編寫的高級測試平臺和設(shè)計(jì)組件使用任何設(shè)計(jì)語言。混合和匹配多個(gè)語言的能力可以使設(shè)計(jì)人員在多個(gè)抽象層上共享數(shù)據(jù),并在單次仿真中集成多個(gè)運(yùn)算模型。不管設(shè)計(jì)人員處于哪個(gè)設(shè)計(jì)階段,工程師都可以使用事務(wù)器接口從不同抽象層連接即插即用模型,從而滿足不同層的需求。這樣不僅擴(kuò)展了通過接口的數(shù)據(jù)類型,還能對包括VHDL在內(nèi)的所有標(biāo)準(zhǔn)語言之間的測試平臺復(fù)用提供支持,從而推進(jìn)高級驗(yàn)證方法的廣泛采用。

進(jìn)一步的功能驗(yàn)證

高效驗(yàn)證需要兩個(gè)關(guān)鍵要素,而這兩個(gè)要素都可以由SystemVerilog和SystemC保證。首先,驗(yàn)證環(huán)境必須能夠盡可能自動地檢測缺陷,在這樣的環(huán)境中象聲明、自動化響應(yīng)檢查器和記分板等功能都會派上用場。其次,驗(yàn)證環(huán)境必須能夠產(chǎn)生能引起缺陷的正確激勵(lì)信號。激勵(lì)可以通過定向測試或受限隨機(jī)技術(shù)生成,這些技術(shù)能以相對較少的代碼遍歷各種情況。

SystemVerilog和SystemC SCV允許用戶在約束方面描述激勵(lì)情景,規(guī)定驅(qū)動設(shè)計(jì)的信號或事務(wù)所需的邏輯值。這樣仿真器可以為激勵(lì)產(chǎn)生隨機(jī)值,并具有能確保所生成的情景有效的約束條件。新的情景可以通過簡單地重新運(yùn)行具有不同隨機(jī)種子的仿真器形成,從而產(chǎn)生不同但等同有效的激勵(lì),因此可以用來檢查新的功能。

使用隨機(jī)化和約束條件可以在驗(yàn)證產(chǎn)能方面產(chǎn)生許多實(shí)質(zhì)性的改善。其它語言只能通過使用面向?qū)ο蠡蛎嫦蚍绞降膹?fù)雜編程技術(shù)才能提供這些性能。雖然SystemVerilog在其面向?qū)ο蟮募軜?gòu)中包括隨機(jī)化和約束條件,但它也能提供多種方式來部署這些性能,而且不需要學(xué)習(xí)面向?qū)ο蟮木幊碳夹g(shù),因此這些先進(jìn)技術(shù)得到了廣泛使用。

一旦測試平臺中整合了隨機(jī)化功能,就需要通過功能覆蓋判斷實(shí)際上可能會發(fā)生哪一種情景。SystemVerilog功能覆蓋將跟蹤設(shè)計(jì)的哪個(gè)功能會被運(yùn)用,因此不會在同一功能上浪費(fèi)時(shí)間。

橋接設(shè)計(jì)和小組層次

因?yàn)榭紤]驗(yàn)證過程的前后總是有所幫助,因此高效的方法是把測試平臺的重點(diǎn)放在設(shè)計(jì)該做什么,而不要放在如何做設(shè)計(jì)上。最便利的做事方式是在事務(wù)級編寫測試平臺。提高抽象層次可以增加產(chǎn)能,因?yàn)檫@樣可以使高層功能得到驗(yàn)證,并且糾正速度比較低抽象層快。可以通過某種自動方式使用受限隨機(jī)、聲明、形式或其它技術(shù)處理細(xì)節(jié),也可以在更廣泛的設(shè)計(jì)和驗(yàn)證工程師之間劃分細(xì)節(jié)。

事務(wù)是指在受限時(shí)間周期內(nèi)系統(tǒng)中發(fā)生的所有活動集合。感興趣活動在特定時(shí)間開始,在一段時(shí)間后結(jié)束。在特定設(shè)計(jì)單元中或在兩個(gè)單元之間發(fā)生的所有操作、狀態(tài)修改、數(shù)據(jù)移動和運(yùn)算都是事務(wù)。事務(wù)級模型用來在高層抽象描述復(fù)雜系統(tǒng),允許設(shè)計(jì)師在進(jìn)入完整實(shí)現(xiàn)的低層細(xì)節(jié)之前解決架構(gòu)問題。在功能驗(yàn)證方面,基于事務(wù)的測試平臺允許驗(yàn)證工程師在構(gòu)思設(shè)計(jì)的層次驗(yàn)證正確操作。

因?yàn)槭聞?wù)級模型提供的細(xì)節(jié)要比Verilog和VHDL RTL模型少得多,因此與在寄存器傳輸級建模的可執(zhí)行平臺相比,它們在仿真時(shí)的運(yùn)行速度非常快。SystemC事務(wù)模型也很快,甚至可以用作軟件開發(fā)平臺,從而支持早期的軟件開發(fā)和軟硬件協(xié)同仿真。另外,事務(wù)級和SystemC功能模型也具有足夠快的速度,可用于系統(tǒng)級架構(gòu)化建模和分析。

事務(wù)瀏覽功能可使SystemC TLM供從事項(xiàng)目的所有工程師使用,從而進(jìn)一步提高設(shè)計(jì)和調(diào)試的效率。SystemC和TLM可以為系統(tǒng)架構(gòu)師和編程人員建立多產(chǎn)的公共平臺。事務(wù)的可視性可以表明由模型產(chǎn)生和消耗的特殊事務(wù)序列以及彼此之間的關(guān)系。

SystemC和TLM還能為所有等級的設(shè)計(jì)層次上的復(fù)用提供重要的機(jī)會。例如,硬件設(shè)計(jì)師可以在預(yù)先定義的接口上用較低層RTL模型代替高層C模型。通過復(fù)用不同抽象層上的測試平臺組件可以在多個(gè)工程學(xué)科之間建立聯(lián)系路徑,增加信息共享,提高效率。

集成語言的價(jià)值

將多個(gè)先進(jìn)的編程語言集成在單個(gè)環(huán)境中可以使硬件設(shè)計(jì)師選擇復(fù)用用SystemC編寫的測試平臺,或選擇用SystemVerilog創(chuàng)建的額外驗(yàn)證組件。現(xiàn)在架構(gòu)師、編程人員和硬件設(shè)計(jì)師可以充分利用具有SystemVerilog聲明、受限隨機(jī)生成、功能覆蓋和測試平臺自動化等功能的可復(fù)用測試平臺組件。

有許多理由要求在同一仿真中整合用不同語言編寫的以及在不同抽象層次的模塊。IP有許多來源,也有許多種形式。而且在集成過程中,很有可能所有的模塊不會同時(shí)出現(xiàn)在相同的抽象層次。比如,在自頂向下的流程中,原本所有模塊都是事務(wù)級模型。在逐步調(diào)整的過程中,一些模塊會被RTL所替換。

SystemVerilog直接編程接口(DPI)可以在SystemC和SystemVerilog之間提供必要的高性能、易用性鏈接。有了SystemVerilog DPI后,系統(tǒng)架構(gòu)師和軟件工程師就可以用SystemC做設(shè)計(jì),然后直接移動到SystemVerilog域進(jìn)行驗(yàn)證,并允許他們充分利用受限隨機(jī)技術(shù)、測試平臺自動化、聲明和功能覆蓋等功能。

因?yàn)槭侵苯舆B接,SystemVerilog DPI要比編程語言接口(PLI)等標(biāo)準(zhǔn)應(yīng)用編程接口(API)更便利更快速。SystemVerilog面向?qū)ο蟮奶匦砸哺菀讋?chuàng)建可復(fù)用測試環(huán)境,因?yàn)樗试S約束和其它方面通過繼承進(jìn)行控制或覆蓋。不過對于不準(zhǔn)備或不愿意從事面向?qū)ο蟮木幊倘藛T而言,在事務(wù)級編寫測試和約束的能力也能顯著增加測試效率。

SystemVerilog DPI開放了一個(gè)公共的通信通道,因此允許跨越許多語言和引擎實(shí)現(xiàn)測試平臺的復(fù)用。

統(tǒng)一的驗(yàn)證環(huán)境

為了充分發(fā)揮這種混合語言環(huán)境的先進(jìn)驗(yàn)證性能,設(shè)計(jì)小組需要一個(gè)基于標(biāo)準(zhǔn)的解決方案,以便他們利用每種語言的長處,包括可應(yīng)用于多個(gè)抽象層的可復(fù)用驗(yàn)證組件。

仿真仍然是高級驗(yàn)證方法的核心。仿真器應(yīng)該從根本上支持SystemVerilog、SystemC、Verilog和VHDL。對單個(gè)內(nèi)核中HDL和高層驗(yàn)證語言的根本性支持可以獲得更快的性能和高度集成的調(diào)試和分析環(huán)境。如果在使用公共圖形用戶接口的統(tǒng)一內(nèi)核中支持所有的語言,并且語言的混合是透明的,那么肯定能獲得很大的靈活性,語言之間也很容易移植。

仿真器應(yīng)該將SystemVerilog和SystemC的設(shè)計(jì)與驗(yàn)證功能集成在統(tǒng)一的環(huán)境中,并設(shè)定最大化產(chǎn)能的階段。一個(gè)全面的混合語言設(shè)計(jì)環(huán)境允許用SystemVerilog或SystemC編寫的高級測試平臺與包括Verilg或VHDL在內(nèi)的任何設(shè)計(jì)語言一起使用。

這樣,架構(gòu)師和設(shè)計(jì)師就可以選用他們所專長的任何語言,然后與項(xiàng)目的其他成員一起共享成果。在不同學(xué)科之間的這座橋梁可建立用于開放通信線的整體協(xié)作過程。結(jié)果將形成在線對話,使得許多問題和機(jī)會可以在設(shè)計(jì)開發(fā)過程的早期獲得討論澄清,而此時(shí)這些問題解決起來會更容易,代價(jià)也較低。

高級驗(yàn)證方法和事務(wù)級建模的有機(jī)結(jié)合可以創(chuàng)造出極大的靈活性,顯著地提高驗(yàn)證產(chǎn)能和設(shè)計(jì)質(zhì)量,同時(shí)在系統(tǒng)架構(gòu)師、軟件設(shè)計(jì)師、硬件設(shè)計(jì)師和驗(yàn)證工程師之間促成更好的交流。使用高層SystemC和事務(wù)級模型可以加速設(shè)計(jì)創(chuàng)建,推進(jìn)架構(gòu)化選擇的開發(fā)。SystemVerilog可以通過聲明和功能覆蓋等高級驗(yàn)證技術(shù)加快系統(tǒng)有效性的確認(rèn)。

評論