100MHz 數字存儲示波表樣機的研究與試制----數據采集系統(tǒng)設計(三)

3.4.3隨機采樣

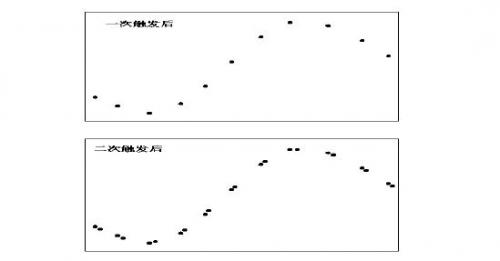

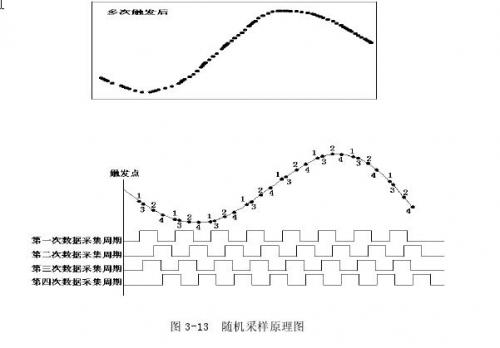

本文引用地址:http://www.104case.com/article/201706/348243.htm隨機采樣也是一種等效時間采樣。它的采樣點是在隨機時刻采集的,與觸發(fā)事件無關。這些采樣點之間的時間間隔為一已知的時間,由采樣時鐘確定。當示波器在等待觸發(fā)事件時,A/D就在連續(xù)的進行采樣,并存入FIFO.當一個觸發(fā)事件到來時,時間測量電路就對觸發(fā)脈沖到觸發(fā)脈沖后第一個采樣脈沖之間的時間間隔進行測量。由于采樣間隔是固定的,所以,示波器能得到相對位置固定的一組采樣點。當第一次采集的所有采樣點存儲完畢之后,就開始采集一組新的采樣點,并等待新的觸發(fā)事件。新觸發(fā)事件到來以后,時間測量電路又進行新的時間測量,以此來排列第一組采樣點和第二組采樣點的相對位置,并按順序存入存儲器。隨機采樣的原理圖如圖3-13.

順序采樣與隨機采樣都屬于等效時間采樣,在這兩種取樣方式下,示波器的帶寬稱為等效帶寬。它們的共同之處是都只能觀測周期信號。但同時它們也有很大的不同:1.順序采樣的采樣點與觸發(fā)脈沖有△t的延遲時間關系,而隨機采樣的采樣點與觸發(fā)脈沖無任何關系,完全是隨機的。2.順序采樣觸發(fā)后每個信號周期只有一個采樣點,而隨機采樣每個信號周期可以獲得一組采樣點。在實際應用中,由于隨機采樣要計算擺點的位置,所以它填滿一個完整的波形所花的時間要比順序采樣多一些,但隨機采樣相比于順序采樣最大的優(yōu)點在于能夠提供預觸發(fā)信息。

1.隨機采樣的實現

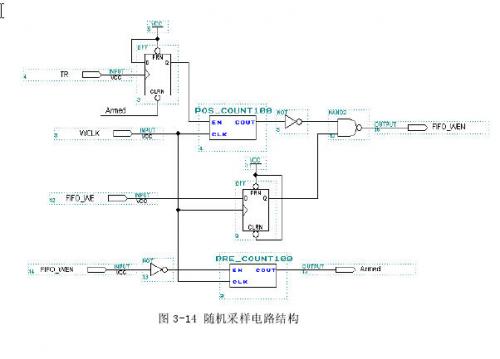

隨機采樣與實時采樣的實現電路有所不同。實時采樣的“+”延遲觸發(fā)計數器和“—”延遲觸發(fā)計數器是通過DSP來設置計數值,而隨機采樣我們是固定兩個計數器的值為100,也就是說觸發(fā)前和觸發(fā)后各采100個點。隨機采樣的主要電路結構如圖3-14.

首先,在每個寫時鐘(WCLK)檢測DSP是否發(fā)出FIFO寫使能信號(FIFO_WE)。當DSP發(fā)出寫FIFO命令時,D觸發(fā)器輸出為“1”。同時,由于計數器POS_COUNT100初始時輸出為“0”,所以經反相后輸出為“1”,與D觸發(fā)器的輸出同作為與非門的輸入,將FIFO寫使能(FIFO_WEN)置為“0”。FIFO_WEN經反相后作為PRE_COUNT100的計數使能信號,計數器根據寫時鐘計數。當計滿100個數后,Armed變?yōu)楦唠娖剑试S觸發(fā)信號TR.等待觸發(fā)過程中,FIFO寫時鐘等于FIFO讀時鐘。當觸發(fā)脈沖到來時,FIFO讀時鐘無效,POS_COUNT100開始根據寫時鐘計數。計滿100個數后POS_COUNT100輸出變?yōu)?ldquo;1”,使FIFO寫使能無效,從而結束一次觸發(fā)一組數據的采集。

2.時間測量電路

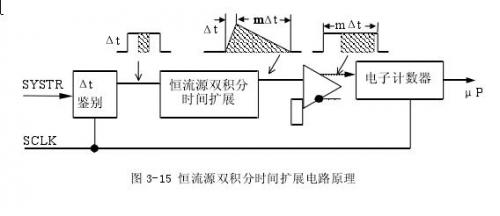

要實現隨機采樣技術,其關鍵就是要精確測量觸發(fā)脈沖與觸發(fā)脈沖后第一個采樣脈沖之間的△t,只有準確的測量出這個△t才能擺正各次觸發(fā)所采集的采樣點在時間軸上的時間關系,從而保證正確的重現信號波形。

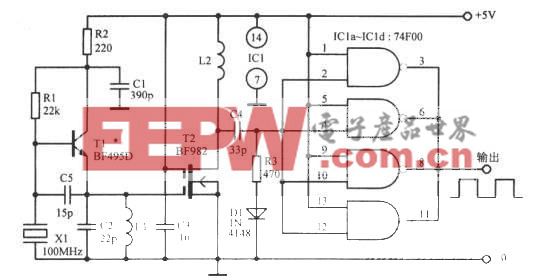

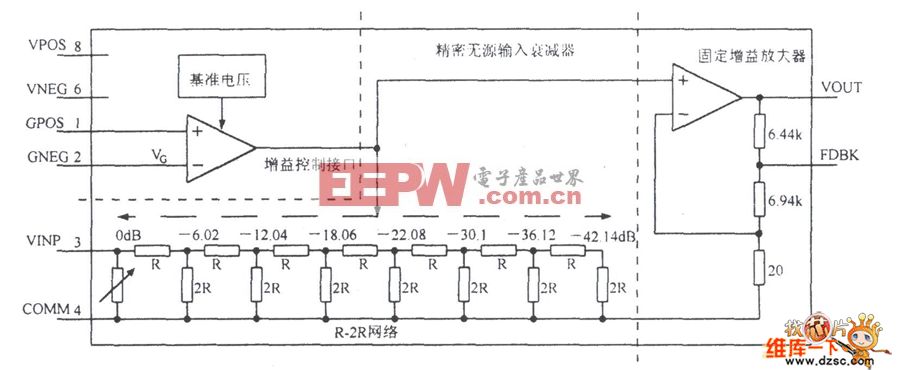

項目中,由于實時采樣率為100MSPS,且觸發(fā)脈沖和采樣脈沖的出現在時間軸上具有隨機性,因此,兩者間的時間間隔△t很小(0≤△t<10nS),且為0至10nS區(qū)間的任意值,難于對其進行直接的測量和處理。間接測量的方法有多種,采用模擬時間擴展器測量第一采樣脈沖與觸發(fā)脈沖之間的隨機時間間隔△t是一種可行的方案。我們采用的模擬擴展電路是恒流源雙積分時間擴展電路,它將時間間隔△t線性放大數倍(通常放大倍率為250至500倍),形成計數時間閘門,在閘門時間內對標準時鐘源T 0計數。然后根據計數結果確定△t的值。該功能單元的原理框圖由圖3-15所示。

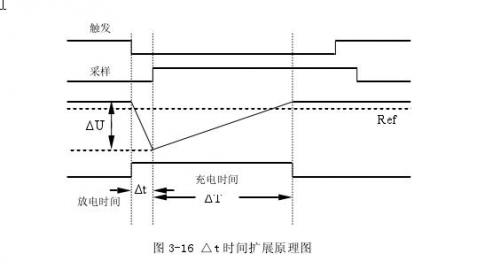

本系統(tǒng)采用的恒流源雙積分時間擴展電路是利用兩個恒流源對一個電容的快放慢充電,來實現對時間的展寬:在觸發(fā)脈沖下降沿到來時進行放電,當第一個采樣脈沖上升沿到來時進行充電,且放電電流遠大于充電電流,就可以實現時間的展寬。圖3-16為雙斜率電容充電電路時間展寬工作原理示意圖。

由圖知,

即雙斜率積分時間展寬電路的放大倍數是放電電流與充電電流之比。而實際電路的充放電流具有非線性,尤其對很小的時間間隔,非線性的影響就非常明顯。另外充放電路輸出的鋸齒波,還要送到比較器以產生所需的計數時間閘門,所以實際的放大倍數小于理論計算出的放大倍數。

若DSO的最小時間分辨率tes =200ps,計數脈沖為To =10ns,則時間放大倍數是K:K= To/tes =50,因此雙斜率積分時間展寬電路的實際放大倍數必須大于50倍。在保證充放電線性的基礎上提高放大倍率顯然有利于提高時間測量精度,放大倍率的調節(jié)可以通過調節(jié)充電電流和放電電流的大小實現,還可通過調節(jié)比較電壓和電容值來實現微調。

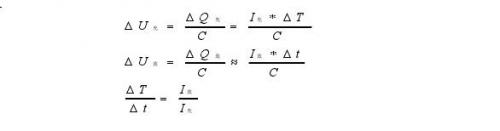

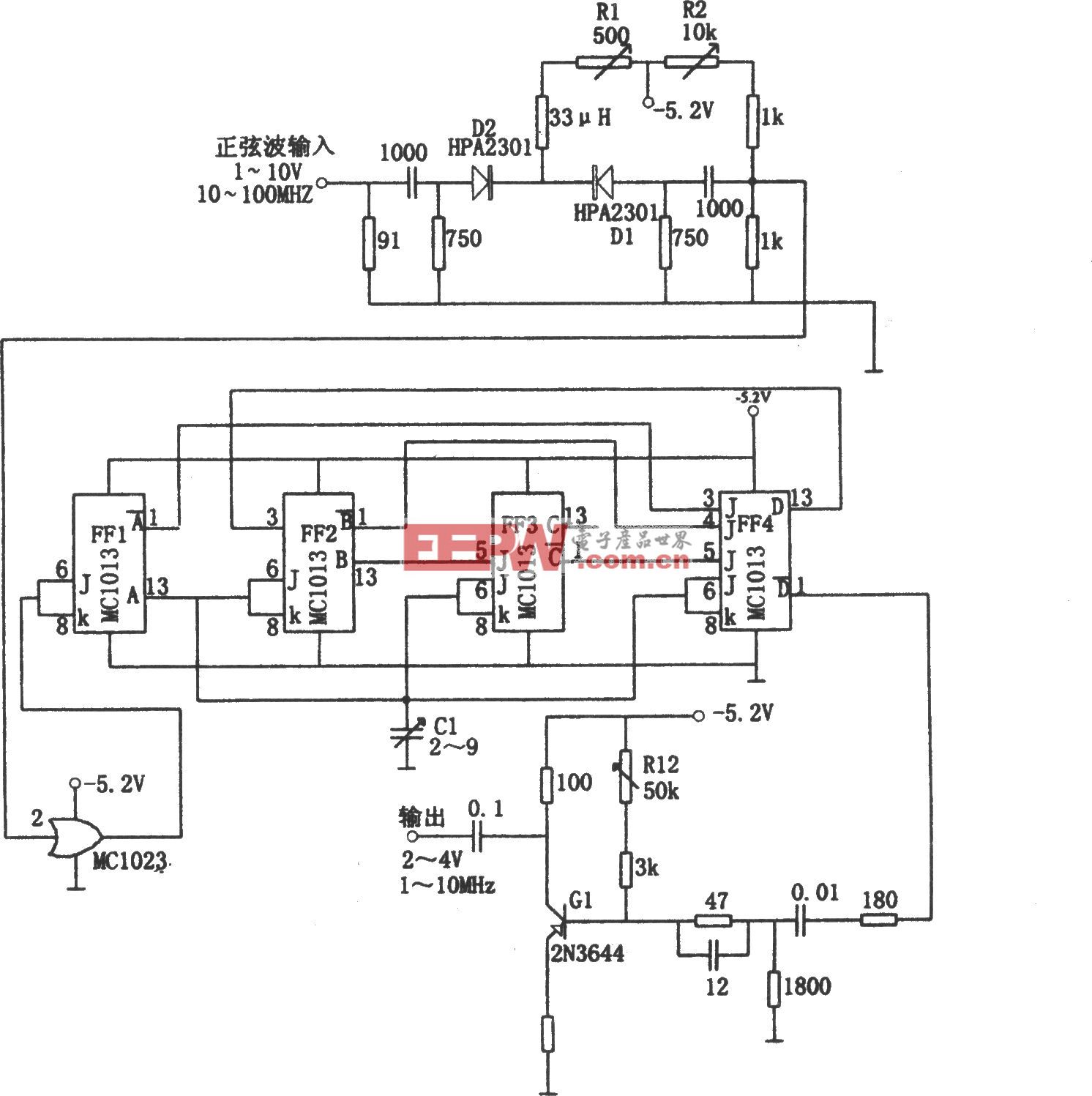

事實上,要讓恒流源雙積分時間擴展電路要工作在線性區(qū)△t不能太小,而由上文分析知道0≤△t<10nS,且在[0,10nS)區(qū)間任意取值,這就必然導致有時模擬擴展器不能正常工作。為了解決這一矛盾,我們在△t上插入一個恒定的時間間隔T0(T0 =10nS),這樣△t +T0∈[10 nS,20nS)。經過處理后的時間間隔就可以確保時間擴展器電路工作在線性區(qū)。實現電路如圖3-17所示。

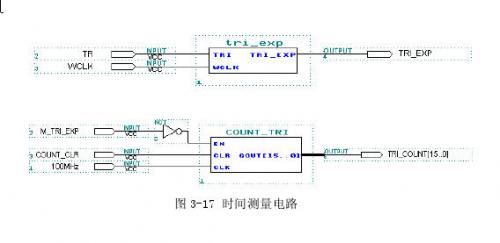

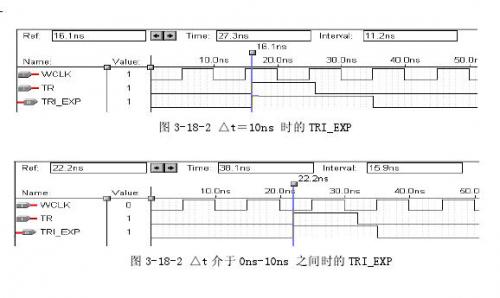

如圖所示,TRI_EXP 模塊主要完成△t+10ns 的功能,其仿真圖如圖 3-18。

COUNT_TRI 模塊主要完成對模擬展寬后脈沖的計數工作。其中,M_TRI_EXP為模擬電路送來的展寬后脈沖所形成的閘門信號,用它來作為計數使能控制。同時,用 100MHz 時鐘來對它進行計數。TRI_COUNT[15..0]為展寬脈沖的計數值,計數結束后將它送入 DSP,做為擺點的依據。

3.時間擴展器的校準

由于模擬脈沖展寬電路是由一些分離元件設計的,工作狀態(tài)易受溫度等外界環(huán)境因素影響,展寬倍數也因此隨時在改變,所以很難精確的計算其展寬倍數。為了消除K值的變化、比較電平的漂移帶來的誤差,所以引入校正技術:通過三次測量,即先測To和2To的值,再測tx+To值進行計算處理。

(1)當t = T0時,擴展后得:NsT0=KT0-TH

計數值Ns=(KT0-TH)/TH (A)(其中,TH為無效擴展時間)

(2)當t = 2T0時,擴展后得:NsT0=2KT0-TH

計數值Nr=(KT0-TH)/TH (B)

(3)當t=tx+T0時,擴展后得:NsT0=K(tx+T0)-TH

計數值Nx=[(K(tx+T0)-TH)]/TH(C)

將式(B)減去式(A),得Nr-Ns=K

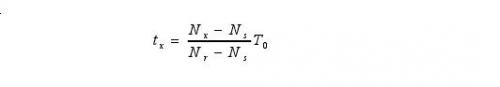

將式(C)減去式(A),得Nx-Ns=Ktx/T0,并將上面的K值帶入,得:

由上式可見,通過對擴展器的校正,完全消除了恒流源和比較電平的變化對測量結果的影響。以上電路可以方便地在FPGA中實現。

4.隨機采樣的顯示

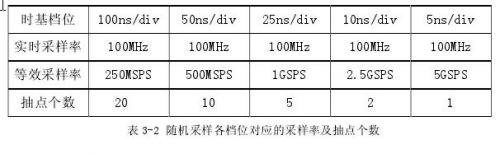

上面我們已經介紹過本項目中在100ns/div-5ns/div的檔位下采用隨機采樣技術,而且隨機采樣的時候,我們的采樣率固定為100MHz.我們知道示波器時間軸上共有10格,每格25個點。所以,當在5ns/div檔位下的時候示波器的等效采樣率最高,等于5GSPS(5ns/25 =0.2ns)。在具體實現隨機顯示的過程中,我們采用抽點顯示的方法,即在等效采樣率最高的時候,采樣足夠多的點,然后每個檔位依此抽點顯示。隨機采樣時,各檔位的等效采樣率以及抽點個數如表3-2.

評論