鋰離子電池管理芯片的研究及其低功耗設計 — 鋰離子電池管理芯片的電路實現 (二)

4.2.2振蕩器

本文引用地址:http://www.104case.com/article/201706/348223.htm1電路結構

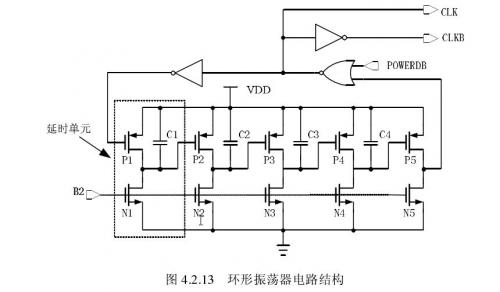

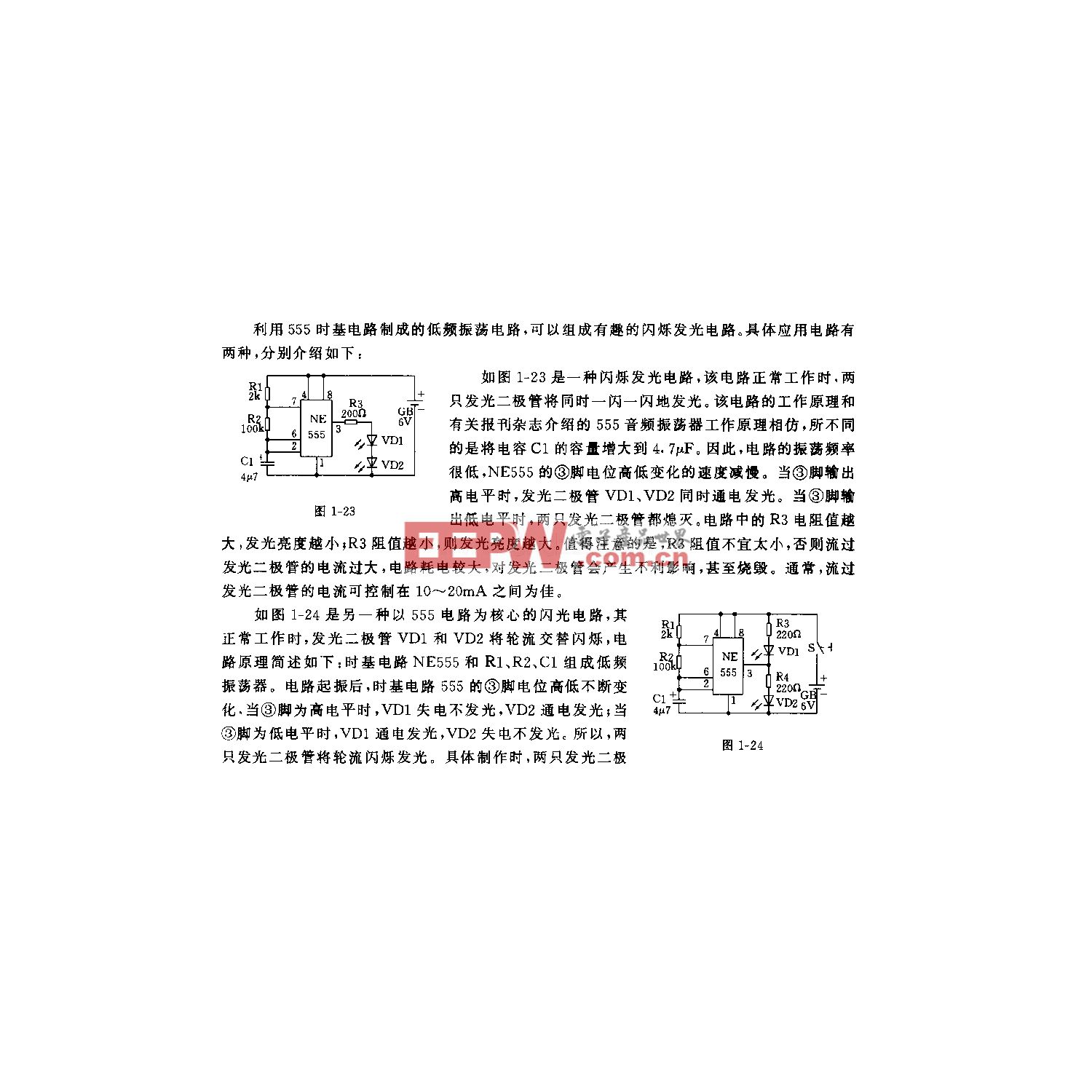

延時電路設計中,一個重要的部分便是振蕩器。電池管理芯片中的振蕩器,必須能在較寬的工作電壓范圍(1.5V~8V)內、在各種工藝和使用條件下輸出頻率相對穩定的時鐘信號,而且電流消耗要足夠低。除負載短路外,電池產生過充電、過放電和過流等意外情況發生后,允許存在的時間均在ms級;又考慮到延時時間參數的設置和頻率對功耗以及亞閾值電 路的影響,振蕩器的頻率設為2kHz.振蕩器結構中,RC振蕩器是常見的一種,其輸出頻率受閾值電壓影響較小,但是受電源電壓影響較大;Relax振蕩器是另一種常見結構,其結構簡單,輸出頻率受電源電壓變化影響較小,但是在電容放電時,存在從電源到地的通路,因此并不適合在低功耗場合使用。而環形振蕩器結構簡單,通過改進易于實現低電流消耗,所以本文設計了一個環形結構的振蕩器,電路如圖4.2.13所示。

圖 4.2.13中,偏置電路通過B2端給NMOS提供柵級電壓,即給振蕩器提供了電流源I CTRL;POWERDB信號由邏輯控制電路輸出,正常情況下為低電平,當電池電壓降低到一設定值時,系統進入Power Down狀態,POWERDB將變為高電平,此時振蕩器輸出為零。

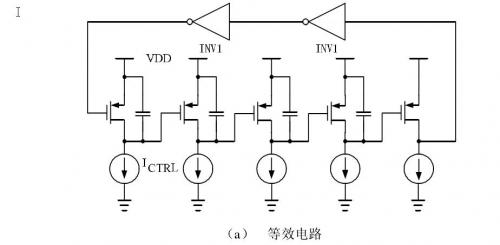

正常工作時,振蕩器的等效電路如圖4.2.14所示。在正常情況下,振蕩器由5個電流源負載反相器和2個推挽反相器組成,反相器數目為奇數,所以振蕩器振蕩,輸出一對頻率相同、相位相反的矩形波CLK和CLKB.從圖4.2.13可知,第5個電流源負載反相器中,負載電容是或非門的輸入柵極電容,該電容很 小,因此該反相器的上升延時和下降延時很短。同樣,推挽反相器的上升延時和下降延時通常在ns級,對于低頻振蕩器也可以忽略。所以,振蕩周期主要由前四個電流源負載反相器的上升延時和下降延時來決定。可將前四個電流源反相器視為延時單元,如圖4.2.14(b)所示。在估算振蕩器的振蕩周期時,只需要考慮 延時單元。

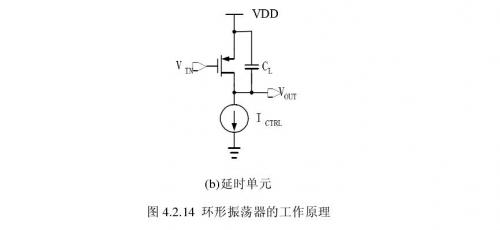

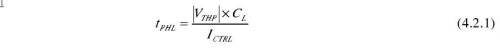

顯然,延時單元的上升延時和下降延時,與其充放電速率及負載電容CL相關。由圖4.2.14(b)可知,當輸入VIN變為高電平時,PMOS管關斷,電容CL開始恒流放電,VOUT電平將下降至使下一級PMOS管導通。將這期間所經歷的時間計為下降延時tPHL,有

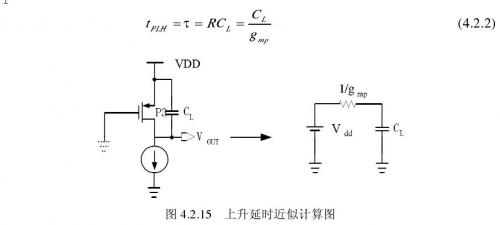

式中,VTHP為PMOS閾值電壓。反之,電容CL充電時,VOUT由低電平將上升至下級PMOS管關斷,所經歷的時間定義為上升延時tPLH。由圖4.2.15的上升延時近似計算圖可以近似求出tPLH為

式中,gmp為PMOS管的跨導。一般地,CL取2pF左右,提高電源電壓和增大PMOS管的寬長比可以增大gmp,從而減小上升延時。和下降延時相比,上升延時較小,估算時可以忽略不計。

因此,振蕩頻率fOSC可以表示為

式中,N為電流源負載反相器數目,此處有N=4.由式(4.2.3)可知,在不考慮工藝容差和負載電容值偏移情況下,振蕩頻率誤差主要由電流源所提供的電流穩定性所決定,所以振蕩器希望電流源是一個理想的恒流源,并且有很高的電源電壓抑制比。

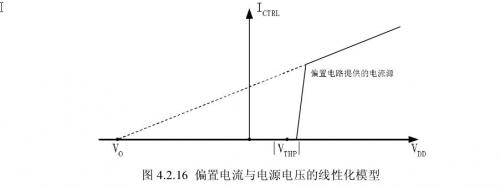

2振蕩頻率誤差因素而在實際應用中,并不存在理想的恒流源,偏置電路提供的輸出電流ICTRL和電源電壓的關系,可由圖4.2.16所示的線性化模型來表征。

圖4.2.16中,當電源電壓在1.5V到8V之間變化時,ICTRL近似線性上升。(4.2.3)式則可變為

式(4.2.4)中,k是斜率,單位為歐姆。式(4.2.4)表征了振蕩器的振蕩頻率與電源電壓V DD、|VTHP|及CL之間的函數關系。下面討論各因素變化對輸出頻率穩定性的影響:

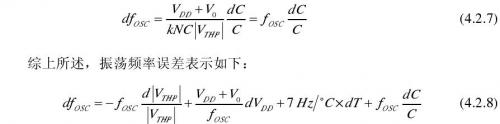

當VDD固定不變時,|VYHP|變化時,對(4.2.4)兩邊求導有

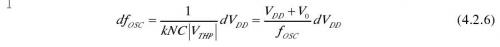

當|VYHP|固定不變時,VDD變化時,對(4.2.4)兩邊求導有

當溫度變化時,其他參數不變,溫度升高時,振蕩頻率上升,反之下降。溫度變化時,振蕩頻率變化主要是PMOS管的閾值電壓隨溫度變化。由于閾值電壓與溫度之間的關系很復雜,所以通過模擬來確定溫度與振蕩頻率之間的關系。

模擬結果表明,溫度變化,其他參數不變時,振蕩頻率隨溫度近似線性上升,估算時取(Δfosc/T)≈7Hz/℃。

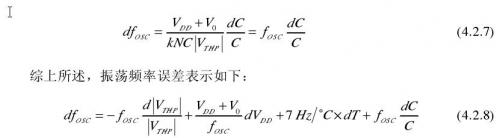

當電容C變化,其他參數不變時,對(4.2.4)式兩邊求導有:

由(4.2.8)式可知,振蕩頻率誤差也與振蕩頻率值有關。降低振蕩頻率,將在一定程度上減小振蕩頻率誤差。對于給定的振蕩頻率,要想減小振蕩頻率誤差,從根本上應使偏置電路的輸出電路更接近恒流。

3波形及噪聲考慮

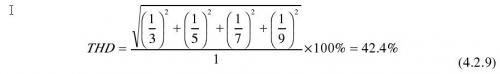

同一頻率的周期矩形波和方波信號頻譜中,諧波的幅度以1/n規律收斂。方波的偶次諧波落在頻譜包絡線的零值點上,所以它的頻譜只包含基波和奇次諧波分量,所以和同一振蕩頻率的矩形波相比,方波具有最小的諧波失真(THD),即有

設計時調整C1的電容使得輸出波形CLK和CLKB接近方波。

時鐘抖動和相位噪聲描述的是同一現象,都指的是振蕩器輸出的不確定性。

兩者不同之處在于時鐘抖動描述輸出時域的不確定性,而相位噪聲則描述輸出頻域的不確定性。

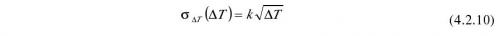

開環系統中,絕對時鐘抖動與測量間隔的平方根成正比,如下式所示

式 中k為比例系數,T為測量間隔。在鋰離子電池管理芯片中,由于振蕩器作用于計數器的時間間隔固定(等于3Tosc、5Tosc、7Tosc、 12Tosc),而且系統延時容許的誤差遠遠大于測量間隔期間的絕對時鐘抖動,故振蕩器對相位噪聲沒有嚴格的要求,盡管如此,設計中還是采取了一些措施來 減小相位噪聲。

研究表明,低頻電源噪聲和高頻襯底耦合噪聲對環形振蕩器的相位噪聲影響最大,所以要盡量減小電源噪聲和襯底耦合噪聲。而圖 4.2.13所示的電路中,延時單元的負載電容不接地而接電源電壓即是為此目的。從NMOS管的源極看進去,NMOS和C L組成低通濾波器,能夠有效濾除數字電路的開、關通過襯底引入振蕩器的高頻噪聲。

同時,根據線性時變模型(LTV)的研究可知,不對稱的上升和下降沿將增加1/f3角頻率,從而增大相位噪聲和時鐘抖動,使得THD變大。1/f3角頻率隨著振蕩器的級數增大而減小,因此設計時振蕩器采用七級反相器,既可以減小1/f3角頻率、減小THD,同時有利于產品的系列化。

評論