時鐘的抖動測量與分析

時鐘是廣泛用于計算機、通訊、消費電子產品的元器件,包括晶體振蕩器和鎖相環,主要用于系統收發數據的同步和鎖存。如果時鐘信號到達接收端時抖動較大,可能出現:并行總線中數據信號的建立和保持時間余量不夠、串行信號接收端誤碼率高、系統不穩定等現象,因此時鐘抖動的測量與分析非常重要。

時鐘抖動的分類與定義

時鐘抖動通常分為時間間隔誤差(Time Interval Error,簡稱TIE),周期抖動(Period Jitter)和相鄰周期抖動(cycle to cycle jitter)三種抖動。

TIE又稱為phase jitter,是信號在電平轉換時,其邊沿與理想時間位置的偏移量。理想時間位置可以從待測試時鐘中恢復,或來自于其他參考時鐘。Period Jitter是多個周期內對時鐘周期的變化進行統計與測量的結果。Cycle to cycle jitter是時鐘相鄰周期的周期差值進行統計與測量的結果。

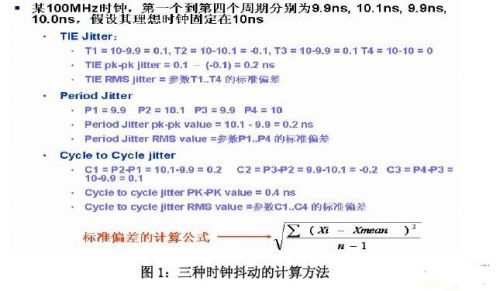

對于每一種時鐘抖動進行統計和測量,可以得到其抖動的峰峰值和RMS值(有效值),峰峰值是所有樣本中的抖動的最大值減去最小值,而RMS值是所有樣本統計后的標準偏差。如下圖1為某100M時鐘的TIE、Period Jitter、Cycle to Cycle jitter的峰峰值和RMS值的計算方法。

時鐘抖動的應用范圍

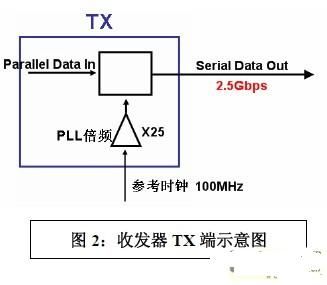

在三種時鐘抖動中,在不同的應用范圍需要重點測量與分析某類時鐘抖動。TIE抖動是最常用的抖動指標,在很多芯片的數據手冊上通常都規定了時鐘TIE抖動的要求。對于串行收發器的參考時鐘,通常測量其TIE抖動。如下圖2所示,在2.5Gbps的串行收發器芯片的發送端,參考時鐘為100MHz,鎖相環25倍頻到2.5GHz后,為Serializer(并行轉串行電路)提供時鐘。當參考時鐘抖動減小時,TX輸出的串行數據的抖動隨之減小,因此,需要測量該參考時鐘的TIE抖動。另外,用于射頻電路的時鐘通常也需測量其TIE抖動(相位抖動)。

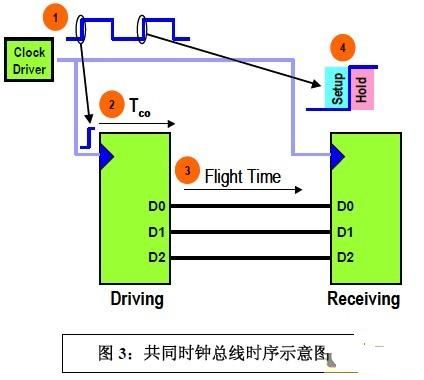

在并行總線系統中,通常重點如在共同時鐘總線(common clock bus)中(如圖3所示),完整的數據傳輸需要兩個時鐘脈沖,第一個脈沖用于把數據鎖存到發送芯片的IO Buffer,第二個脈沖將數據鎖存到接收芯片中,在一個時鐘周期內讓數據從發送端傳送到接收端,當發送端到接收端傳輸延遲(flight time)過大時,數據的建立時間不夠,傳輸延遲過小時,數據的保持時間不夠;同理,當這一個時鐘的周期值偏大時,保持時間不夠;周期值偏小時,建立時間不夠。可見,時鐘周期的變化直接影響建立保持時間,需要測量period jitter和cycle to cycle jitter。關于共同時鐘總線的時序分析的詳細講解,請參考Stephen H. Hall、Garrett W. Hall和James A. McCall寫的信號完整性分析書籍:《High-Speed Digital System Design》。

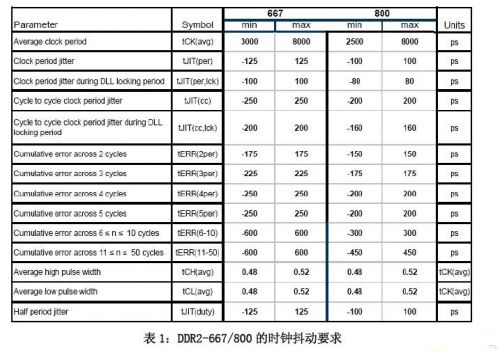

另外一種常見的并行電路-源同步總線(Source Synchronous bus),通常也重點測量period jitter和cycle to cycle jitter。比如DDR2就屬于源同步總線,在Intel DDR2 667/800 JEDEC Specification Addendum規范中定義了時鐘的抖動測試包括周期抖動和相鄰周期抖動,分別如表格1中tJIT(per)和tJIT(cc),此外,還需要測量N-Cycle jitter,即N個周期的相鄰周期抖動,比如表格1中tERR(2per)是連續2個周期的周期值與下2個周期的周期值的時間差,tERR(3per)是3個周期組合的相鄰周期抖動,依此類推。

時鐘抖動的來源和分解

時鐘的抖動可以分為隨機抖動(Random Jitter,簡稱Rj)和固有抖動(Deterministic jitter),隨機抖動的來源為熱噪聲、Shot Noise和Flick Noise,與電子器件和半導體器件的電子和空穴特性有關,比如ECL工藝的PLL比TTL和CMOS工藝的PLL有更小的隨機抖動;固定抖動的來源為:開關電源噪聲、串擾、電磁干擾等等,與電路的設計有關,可以通過優化設計來改善,比如選擇合適的電源濾波方案、合理的PCB布局和布線。

和串行數據的抖動分解很相似,時鐘的抖動可以分為Dj和Rj。但不同的是,時鐘的固有抖動中通常只有周期性抖動(Pj),不包括碼間干擾(ISI)。當時鐘的上下邊沿都用來鎖存數據時占空比時鐘(DCD)計入固有抖動,否則不算固有抖動。

時鐘抖動測量方法

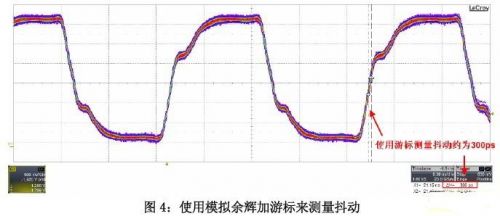

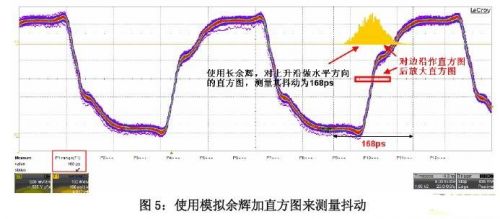

在上個世紀90年代,抖動的測量方法非常簡單,示波器觸發到時鐘的一個上升沿,使用余輝模式,測量下一個上升沿余輝在判定電平上(通常為幅度的50%)的水平寬度。測量水平寬度有兩種方法。

第一種使用游標測量波形邊沿余輝的寬度,如下圖4所示。由于像素偏差或屏幕分辨率(量化誤差)會降低精度,而且引入了觸發抖動,所以這種方法誤差較大。

第二種使用直方圖,對邊沿余輝的水平方向進行直方圖統計,如下圖5所示。測量直方圖的最左邊到最右邊的間距即為抖動的峰峰值(168皮秒)。這種方法的缺點是:引入了示波器的觸發抖動;一次只測量一個周期,測試效率低,某些出現頻率低的抖動在短時間內不能測量到。

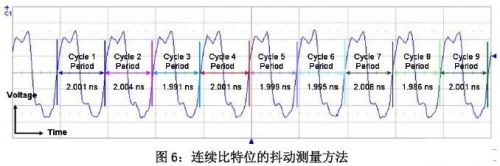

隨著測試儀器技術的發展與進步,目前,示波器的抖動分析軟件不再是測量一兩個周期波形后分析抖動,而是一次測量多個連續比特位,計算與統計所有比特位的抖動,測量的數據量非常大、效率非常高。如下圖6所示為某50MHz時鐘的Period抖動測試,示波器的抖動測試軟件可以一次測量所有周期的周期值,計算出抖動的峰峰值與有效值。

將已測量的每個周期的抖動值做直方圖,可以統計大數據量的抖動的峰峰值和RMS值,如下圖7所示為某時鐘周期抖動的直方圖分析,樣本數量為103k個i,周期抖動的峰峰值為80.45皮秒,周期抖動的RMS值為9.25皮秒。

相位噪聲與TIE抖動

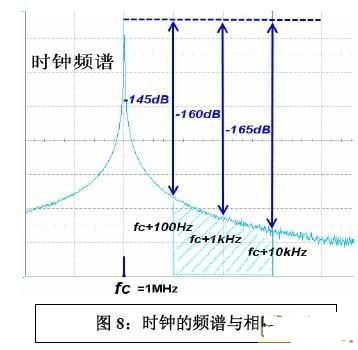

在一些時鐘芯片的數據手冊上規定了相位噪聲(phase noise)的指標要求,相噪可以理解為TIE抖動在頻域的表達方式,通常是使用某些頻譜儀或相噪測試儀測量出來的,單位通常為dBc/Hz,比如某頻率為1MHz的晶振的相噪為:

-145dBc/Hz @100Hz -160dBc/Hz @1kHz -165dBc/Hz @10kHz

如圖8所示為該時鐘的頻譜,在頻點fc+100Hz 的功率與fc頻點(即時鐘頻率)的功率的比值取對數后為-145dB,在頻點fc+1kHz的功率與時鐘頻率的功率之比為-160dB,在頻點fc+10kHz的功率與時鐘頻率的功率之比為-165dB。在安裝了相噪分析軟件的頻譜儀(或者相噪儀)上,通過對圖8的陰影部分的求面積后進行簡單運算,可以得到該時鐘從100Hz到10kHz的TIE的RMS抖動值。對于某些精準的晶振,在某頻段內的RMS抖動可以小于幾百fs。由于實時示波器的抖動噪聲基底大約在2ps左右,對于這類晶振的抖動測試,無法使用實時示波器的測量到,必須使用頻譜儀或相噪儀測量。關于相位噪聲與TIE抖動的換算,可以參考相噪測試儀廠商的技術圖8:時鐘的頻譜與相噪文檔。

時鐘抖動的分析

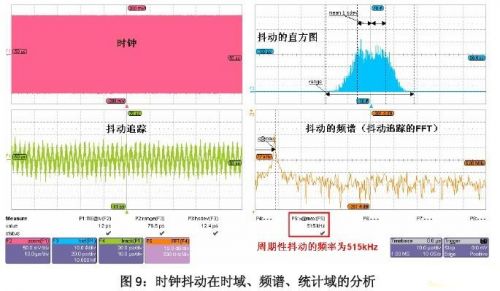

在時鐘抖動測量時,可以在三個域分析抖動,即在時域分析抖動追蹤(jitter track/trend)、在頻域觀察抖動的頻譜、在統計域分析抖動的直方圖。如下圖9所示,左上角的F2為某100MHz時鐘,P1是時鐘的TIE參數測量;右上角的F3是TIE抖動的直方圖,直方圖不是高斯分布,可見時鐘存在固有抖動。

左下角的F4為TIE track(即TIE抖動隨時間變化的趨勢),從TIE Track中可以看到周期性的變化趨勢;右下角的F5是F4的FFT運算,即抖動的頻譜,頻譜的峰值頻率為515kHz,說明該時鐘的周期性抖動(Pj)的主要來源為515kHz,找到頻點后,可以查找電路板上主頻或諧波為該頻率的芯片和PCB走線,進一步調試與分析。

評論