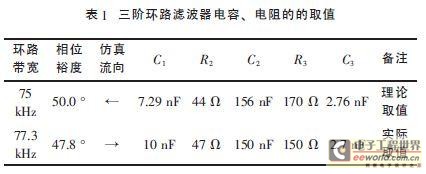

基于芯片測(cè)試的環(huán)路濾波器設(shè)計(jì)

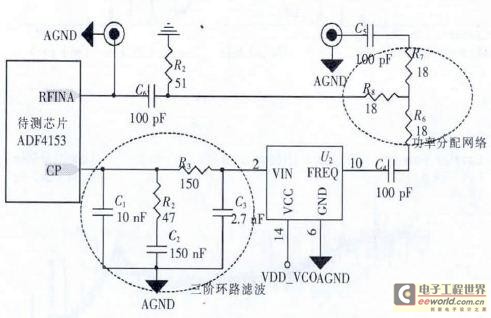

由此,我們確定了環(huán)路濾波器中各個(gè)電容、電阻的取值,并設(shè)計(jì)了可用于ADF 4153芯片測(cè)試的電路原理圖,如圖4所示。VCO的輸出不僅需要連接外部頻譜儀進(jìn)行測(cè)試,還需要通過電容反饋到ADF 4153的REFINA端,同時(shí)REFINA端還需要預(yù)留SMA頭用于射頻輸入頻率范圍及靈敏度測(cè)試。一個(gè)簡單的電阻網(wǎng)絡(luò)用于完成VCO輸出信號(hào)功率的再分配。

圖4環(huán)路濾波器及射頻電路設(shè)計(jì)

3環(huán)路濾波器的測(cè)試驗(yàn)證

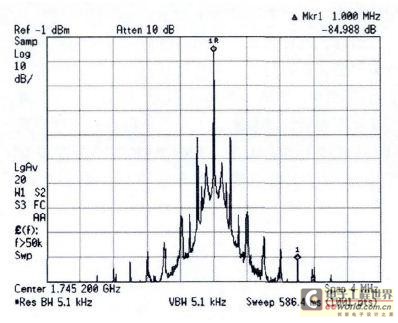

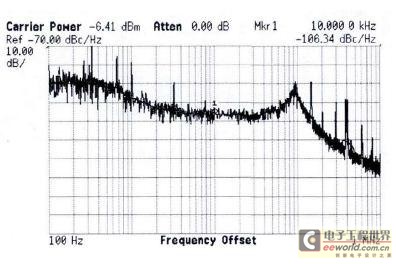

在仿真的基礎(chǔ)上,我們?cè)O(shè)計(jì)并加工了ADF4153的測(cè)試板,并按照計(jì)算的電容、電阻值組成了環(huán)路濾波網(wǎng)絡(luò)。采用Agilent8257D射頻信號(hào)源提供250MHz作為fREFIN,通過SPI端口設(shè)定fPFD=25MHz,N=69,4/5分頻模模式,ICP=5mA,F(xiàn)RAC=101,MOD=125.使用頻譜儀測(cè)量輸出信號(hào),能夠正常鎖定在1.7452GHz,如圖5所示。圖6為該頻點(diǎn)的相位噪聲測(cè)試圖,實(shí)測(cè)相位噪聲為-106.34dBc/Hz.環(huán)路帶寬約為85kHz,與理論值77.3kHz存在一定的差距。這是由于在仿真時(shí)并沒有考慮測(cè)試板走線及測(cè)試插座等存在的寄生電容所導(dǎo)致的偏差,但仍在合理范圍以內(nèi)。

圖5輸出信號(hào)頻譜

圖6相位噪聲測(cè)試圖

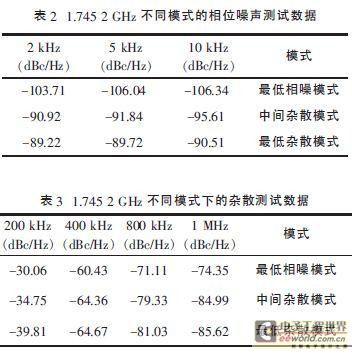

針對(duì)芯片進(jìn)行不同工作模式下的相位噪聲及雜散進(jìn)行測(cè)試,測(cè)試結(jié)果如表2、3所示。

數(shù)據(jù)手冊(cè)規(guī)定最低的相位噪聲模式下5kHz頻偏的相位噪聲PN≤-95dBc/Hz,實(shí)測(cè)該點(diǎn)為-106.04dBc/Hz,測(cè)試結(jié)果滿足要求。

數(shù)據(jù)手冊(cè)規(guī)定中間雜散模式下1MHz頻偏的雜散SN≤-65dBc/Hz,實(shí)測(cè)該點(diǎn)為-84.99dBc/Hz,測(cè)試結(jié)果滿足要求。

綜上所述,該濾波器的設(shè)計(jì)能達(dá)到預(yù)期的設(shè)計(jì)目標(biāo),滿足不同模式下的雜散及相噪測(cè)試的要求,可用于ADF 4153芯片的性能測(cè)試。

4結(jié)束語

本文主要基于芯片測(cè)試目的,針對(duì)外圍電路中的環(huán)路濾波器設(shè)計(jì)來進(jìn)行討論,文中給出了一種簡單、易行的工程化計(jì)算方法和流程,并對(duì)其進(jìn)行了驗(yàn)證測(cè)試,測(cè)試結(jié)果滿足芯片測(cè)試的需要。這種方法已經(jīng)應(yīng)用于多款小數(shù)分頻頻率合成器的測(cè)試電路的設(shè)計(jì)中。

評(píng)論